# Fakultät für Physik und Astronomie Ruprecht-Karls-Universität Heidelberg

Diplomarbeit im Studiengang Physik

vorgelegt von **Daniel Baumeister**aus Aschaffenburg

März 1999

# Entwicklung und Charakterisierung eines ASICs zur Kathodenauslese von MWPCs für das H1-Experiment bei HERA

Die Diplomarbeit wurde von Daniel Baumeister ausgeführt am

Physikalischen Institut

unter der Betreuung von

Herrn Prof. Dr. Ulrich Straumann

#### Zusammenfassung

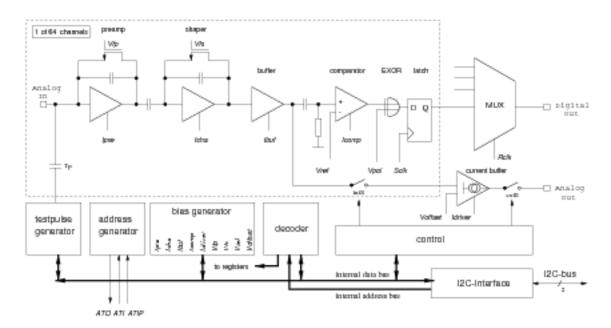

In dieser Arbeit wird die Entwicklung und Charakterisierung des CMOS-ASICs CIPix vorgestellt. Der CIPix wird als Auslesechip für die innere Vieldrahtproportionalkammer des H1-Detektors im Rahmen des CIP-Upgrade-Projektes im Jahr 2000 eingesetzt.

Der Chip integriert 64 Kanäle mit ladungsempfindlichen, rauscharmen Vorverstärkern und Pulsformern. Die verstärkten Signale

werden durch 64 Komparatoren mit einstellbarer Polarität und

Schwellenspannung digitalisiert und durch einen vierfachen Multiplexer auf 16 Digitalausgänge geführt. Die Spannungen und

Ströme zur Regelung der analogen Komponenten sowie verschiedene andere Parameter sind über ein serielles I<sup>2</sup>C-Bus Protokoll

programmier- und rücklesbar. Es werden die Architektur des

CIPix und einzelne Funktionselemente beschrieben, sowie durchgeführte Simulationen und Meßergebnisse präsentiert.

#### Abstract

This thesis describes the development and characterization of the CMOS-ASIC CIPix. The CIPix will be used as a readout chip for the central inner proportional chamber (CIP) of the H1-detector for the CIP upgrade project in the year 2000.

The chip integrates 64 channels with low noise charge sensitive preamplifiers and shapers. The input signals are digitized by 64 comparators with configurable polarity and threshold level and multiplexed by 4 onto 16 digital outputs. The bias settings and various other parameters are programmable and monitorable via an I<sup>2</sup>C-bus serial protocol. The architecture of the CIPix and different functional elements are described as well as the simulation and test results are presented.

# Inhaltsverzeichnis

| 1 | Einl | eitung                                     | 1 |

|---|------|--------------------------------------------|---|

| 2 | Das  | H1-Experiment                              | 3 |

|   | 2.1  |                                            | 3 |

|   | 2.2  |                                            | į |

|   | 2.3  |                                            | 9 |

|   | 2.4  | Das H1-Upgrade-2000-Projekt                | - |

|   | 2.5  | Die alte und neue CIP                      |   |

| 3 | Dor  | CIP-Auslese-ASIC 1                         | • |

| 0 | 3.1  | Überblick                                  | _ |

|   | 3.2  | Die äußeren Randbedingungen                | - |

|   | 3.3  | Das Frontend: Preamplifier, Shaper, Buffer | _ |

|   | 3.4  | Der Komparator                             |   |

|   | 3.5  | Der Multiplexer                            | - |

|   | 3.6  |                                            | - |

|   | 3.7  | Der Analog-Ausgang                         | - |

|   | 3.8  | Die Bias-Generatoren                       |   |

|   | 3.9  | Die Pads                                   |   |

|   |      |                                            |   |

|   | 3.10 | Die Spannungsversorgung                    | M |

| 4 | Digi | ital-Design 3                              | Ę |

|   |      | CMOS-Technologie                           | į |

|   | 4.2  | Design-Methoden                            | 7 |

|   | 4.3  | Der Design-Prozeß                          | į |

|   |      | 4.3.1 Schaltungsbeschreibung mit Verilog   | d |

|   |      | 4.3.2 Synthese                             | 1 |

|   |      | 4.3.3 Layout-Generierung                   | 3 |

| 5 | Der  | Digitalteil des CIPix 4                    | 7 |

| v | 5.1  | Das I <sup>2</sup> C-Interface             | - |

|   | 0.1  | 5.1.1 Der I <sup>2</sup> C-Bus             |   |

|   |      | 5.1.2 Das Interface                        |   |

|   | 5.2  | Der Adress-Generator                       |   |

|   | 5.3  | Die Decoder-Logik                          |   |

|   | 5.4  | Die Testpuls-Steuerlogik                   |   |

|   | 5.5  | Die Steuerlogik für die Analogschalter     |   |

|   | 0.0  | Die Stederlogik für die Analogschauer      | 1 |

|   | 5.6 | Simulationen                              | 68 |

|---|-----|-------------------------------------------|----|

| 6 | Mes | ssungen am CIPix                          | 73 |

|   | 6.1 | Messaufbau                                | 73 |

|   | 6.2 | Messungen am Interface                    | 74 |

|   | 6.3 | Frontend-Messungen                        | 76 |

| 7 | Aus | blick                                     | 79 |

|   | 7.1 | Korrekturen am Adressgenerator            | 79 |

|   | 7.2 | Korrekturen am I <sup>2</sup> C-Interface | 79 |

|   | 7.3 | Korrekturen am Dekoder                    | 80 |

|   | 7.4 | Simulationen                              | 80 |

|   | 7.5 | Korrekturen an der Testpulssteuerlogik    | 81 |

|   | 7.6 | Korrekturen an den LVDS-Receivern         | 84 |

| 8 | Zus | ammenfassung                              | 85 |

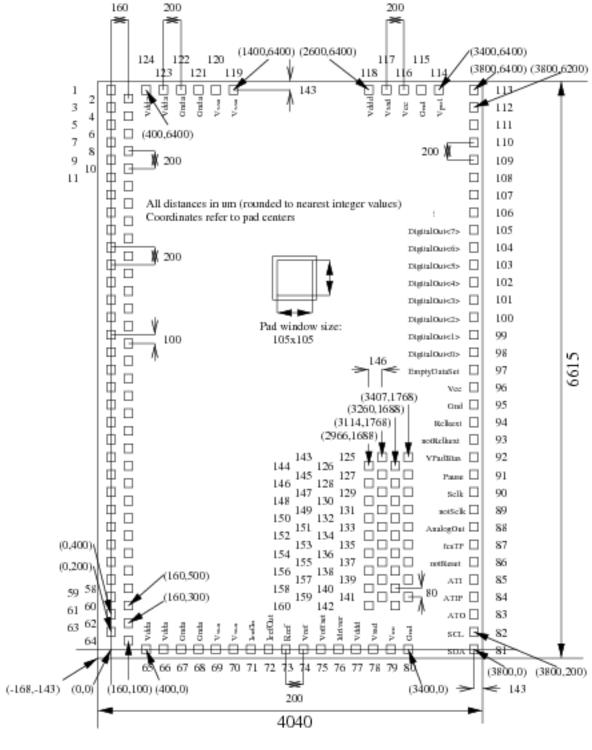

| A | Pad | -Beschreibung des CIPix1.0                | 87 |

|   | A.1 | Pads vorne                                | 87 |

|   | A.2 | Pads unten                                | 89 |

|   | A.3 | Pads hinten                               | 90 |

|   | A.4 | Pads oben                                 | 91 |

|   | A.5 |                                           | 92 |

| В | Evt | erne Beschultung des CIPiv1 0             | 95 |

# Abbildungsverzeichnis

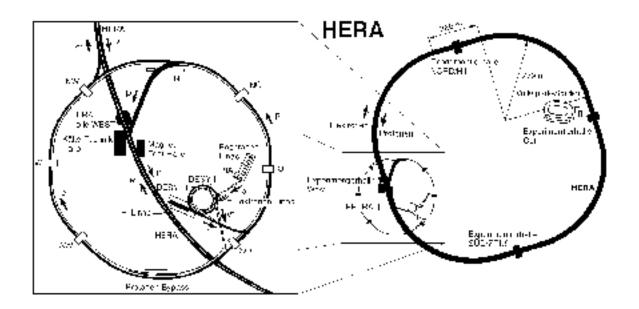

| 2.1  | Der Speicherring HERA am DESY in Hamburg                                    | 4       |

|------|-----------------------------------------------------------------------------|---------|

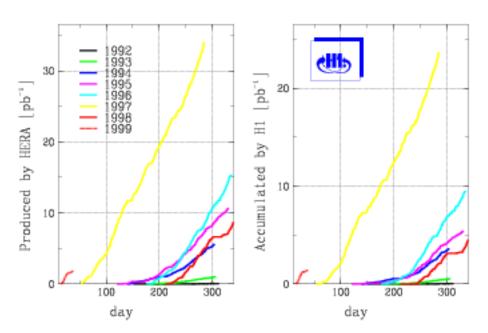

| 2.2  | Von HERA produzierte und von H1 genutzte integrierte Luminosität            | 5       |

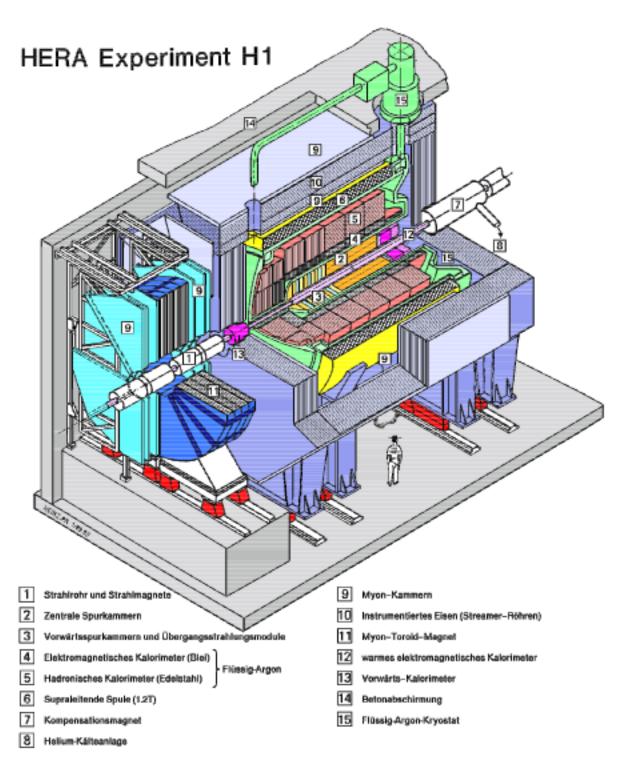

| 2.3  | Schematische Ansicht des H1-Detektors                                       | 6       |

| 2.4  | Das H1-Koordinatensystem                                                    | 7       |

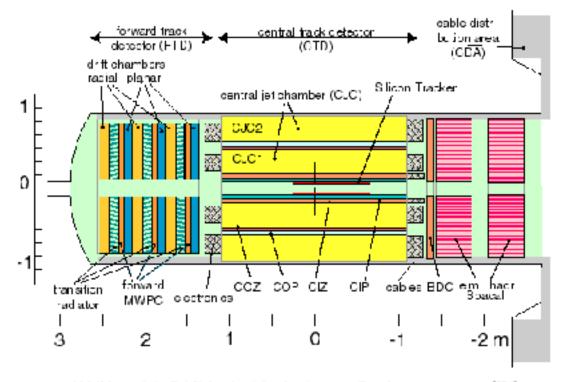

| 2.5  | Seitliche Ansicht des inneren Spurkammersystems                             | 9       |

| 2.6  | Radiale Ansicht des inneren Spurkammersystems                               | 10      |

| 2.7  | Schema der Hierarchie des H1-Triggersystems                                 | 11      |

| 2.8  | Schema der Generierung der Subtrigger durch RAM-Lookup Tables               | 12      |

| 2.9  | Funktionsweise des z-Vertex-Triggers.                                       | 12      |

| 2.10 |                                                                             | 15      |

|      | Schematischer Aufbau einer Kammerlage der neuen CIP                         | 16      |

| 2.12 | z-Abstand aktivierter Pads zur Spur und Anzahl der Pads innerhalb von 5 cm. | 17      |

| 2.13 | Zahl der Cluster in einer Lage der CIP                                      | 17      |

| 2.14 | Verteilung von upstream-Spuren gegen Vertex-Spuren                          | 18      |

| 3.1  | Blockdiagramm des CIPix1.0                                                  | 20      |

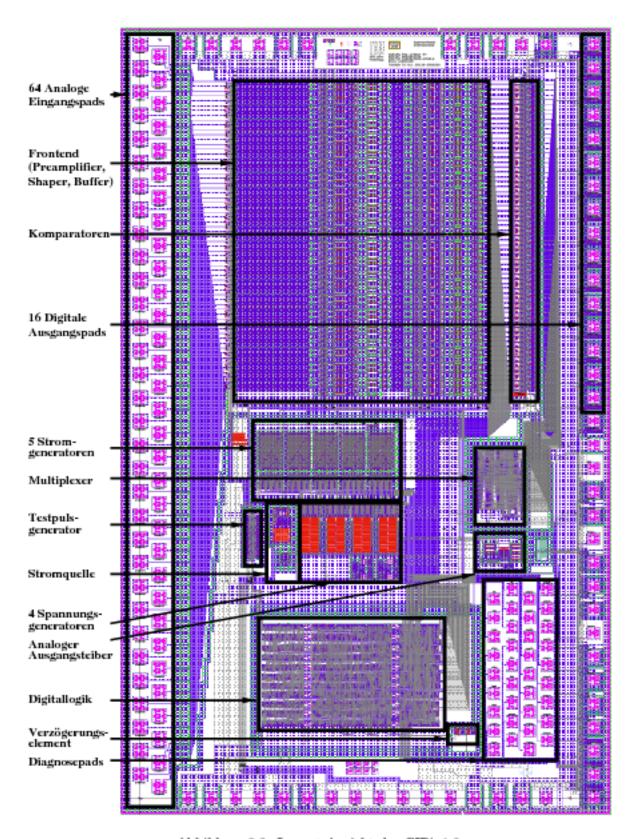

| 3.2  | Layout-Ansicht des CIPix1.0                                                 | $^{22}$ |

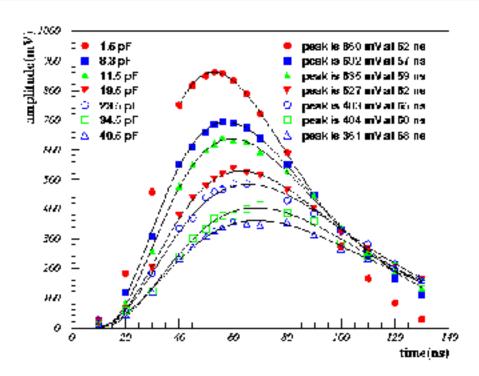

| 3.3  | Pulsshape-Scan am Helix2.0 mit verschiedenen Lastkapazitäten                | $^{23}$ |

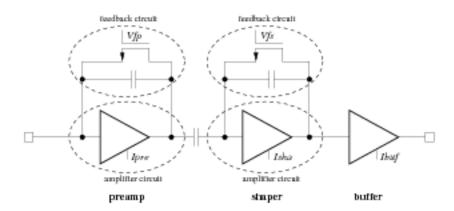

| 3.4  | Schematischer Aufbau der analogen Eingangsstufe                             | $^{24}$ |

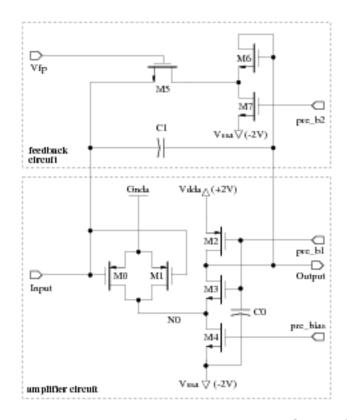

| 3.5  | Schaltplan des Vorverstärkers                                               | $^{25}$ |

| 3.6  | Schematischer Aufbau der Komparatorstufe                                    | $^{25}$ |

| 3.7  | Schaltplan der AC-Kopplung des Komparators                                  | $^{26}$ |

| 3.8  | Schaltplan des differentiellen Komparators                                  | 27      |

| 3.9  | Funktionsprinzip eines Multiplexers                                         | $^{28}$ |

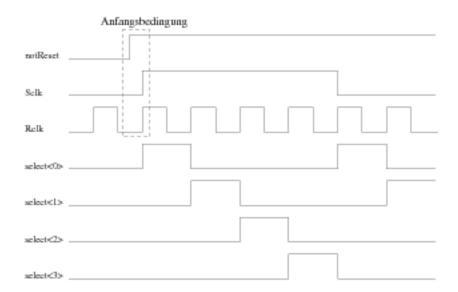

| 3.10 | Multiplexer-Startbedingung und zeitliche Abfolge der Selektionsleitungen    | $^{29}$ |

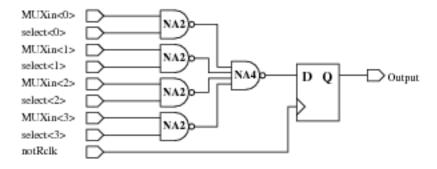

| 3.11 | Schaltplan des Multiplexers                                                 | $^{29}$ |

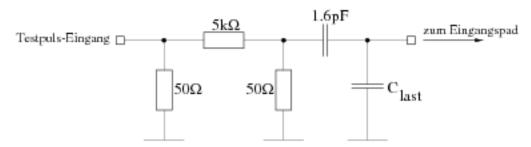

|      | Schema der Testpulseinkopplung                                              | 31      |

|      | Schaltplan des Eingangs-Levelsifters                                        | 32      |

|      | Schaltplan des Ausgangs-Levelshifter                                        | 33      |

| 3.15 | Schematischer Aufbau der bidirektionalen Levelshifter                       | 33      |

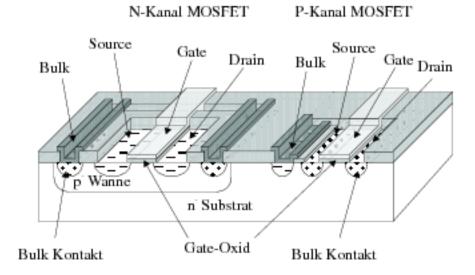

| 4.1  | p-MOSFET und n-MOSFET in einer p-well CMOS-Technologie                      | 36      |

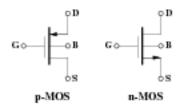

| 4.2  | Schaltungssymbole eines n-MOS- und p-MOS-Transistors                        | 36      |

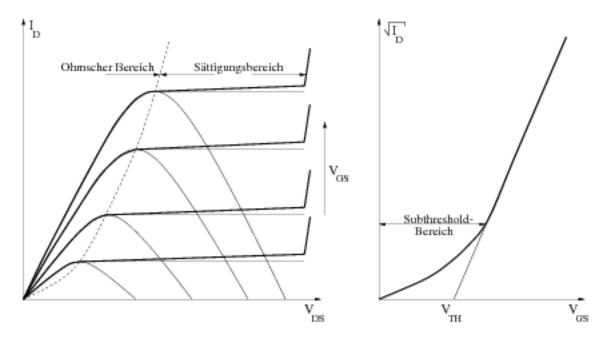

| 4.3  | Übertragungskennlinie und Transkonduktanzkurve eines MOSFETs                | 37      |

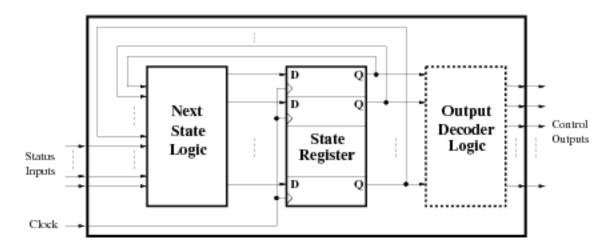

| 4.4  | Struktur eines digitalen Top-Down Designs                                   | 38      |

| 4.5  | Schematische Struktur einer Zustandsmaschine                                | 39      |

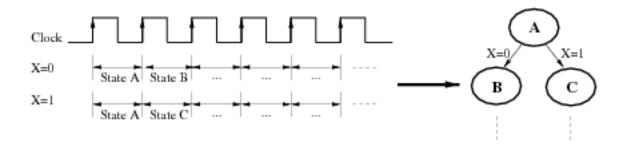

| 4.6  | Prinzip eines Zustandsdiagramms.                                            | 39      |

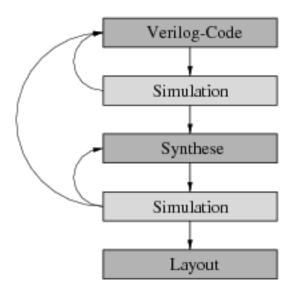

| 4.7  | Typischer Top-Down ASIC-Design Prozeß                                   | 0 |

|------|-------------------------------------------------------------------------|---|

| 4.8  | Verilog-Code eines 4-bit Up-Down Zählers mit asynchronem Reset 42       | 2 |

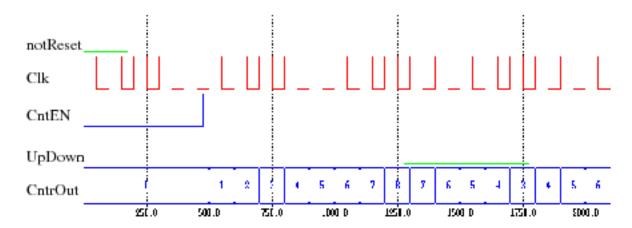

| 4.9  | Simulationsergebnis des 4-bit Zählers                                   | 3 |

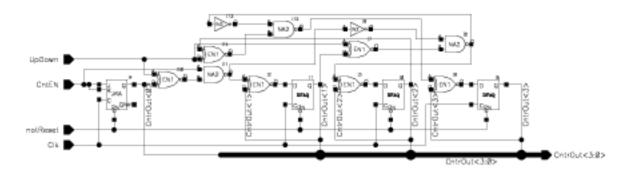

| 4.10 | Synthese-Ergebnis der Verilog-Beschreibung des Zählers                  | 4 |

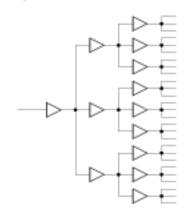

| 4.11 | Schema eines Clock-Trees                                                | 4 |

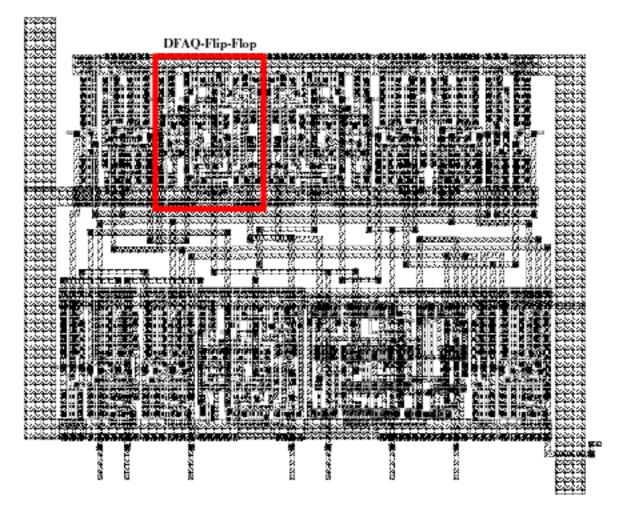

| 4.12 | Ergebnis der Layout-Generierung des 4-bit Zählers                       | 5 |

|      |                                                                         | _ |

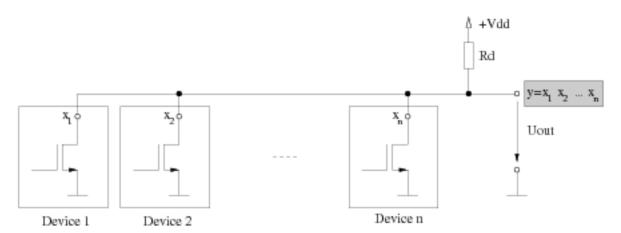

| 5.1  | Schema einer wired-AND Schaltung                                        |   |

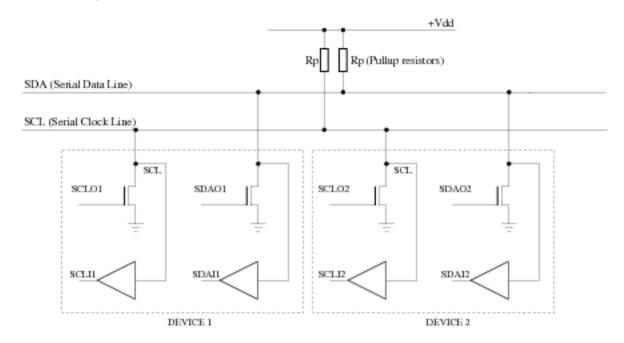

| 5.2  | Blockschaltbild der I <sup>2</sup> C-Ausgangsstufen                     | _ |

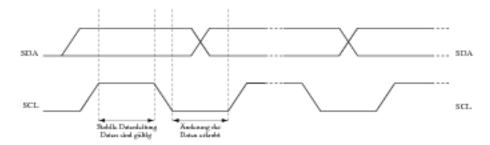

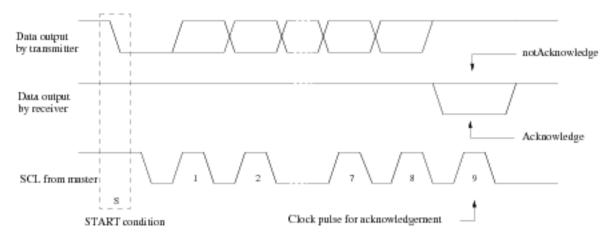

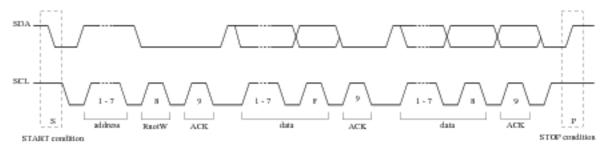

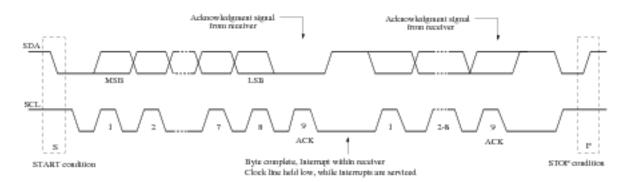

| 5.3  | Schema des bitweisen Transfers auf dem I <sup>2</sup> C-Bus             |   |

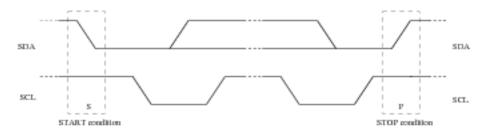

| 5.4  | Start- und Stop-Bedingungen auf dem I <sup>2</sup> C-Bus                |   |

| 5.5  | Acknowledge-Signale auf dem Bus                                         |   |

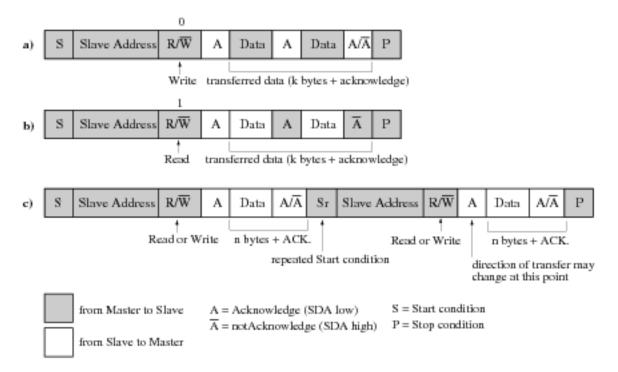

| 5.6  | Schema eines kompletten Datentransfers                                  |   |

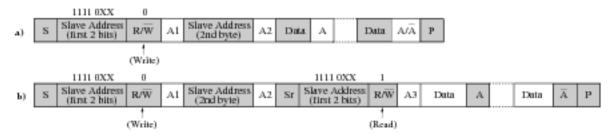

| 5.7  | 7-bit Übertragungssequenzen                                             |   |

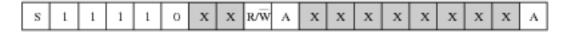

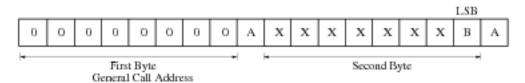

| 5.8  | Format der 10-bit Adresse                                               |   |

| 5.9  | 10-bit Übertragungssequenzen                                            |   |

|      | Format einer General Call Übertragung                                   |   |

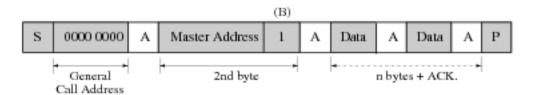

|      | Übertragungssequenz eines Hardware-General Call                         |   |

|      | Erzwingung eines Wartezustands auf dem Bus                              | 5 |

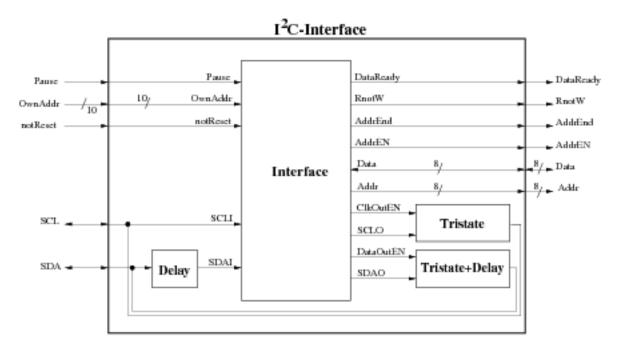

|      | Blockdiagramm der obersten Ebene des I <sup>2</sup> C-Interfaces        | - |

| 5.14 | Blockdiagramm des Interfaces                                            | 7 |

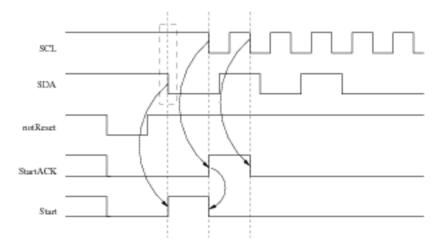

| 5.15 | Handshake-Prozedur nach einer Start-Bedingung                           | 9 |

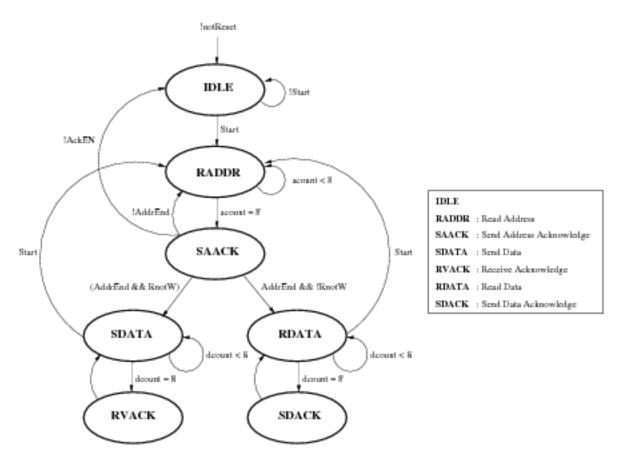

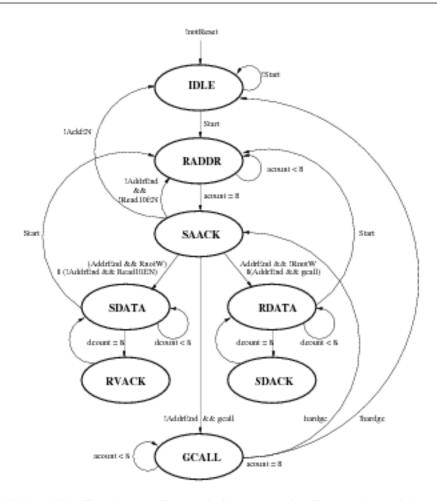

| 5.16 | Zustandsdiagramm des Moduls Ctrl                                        | 0 |

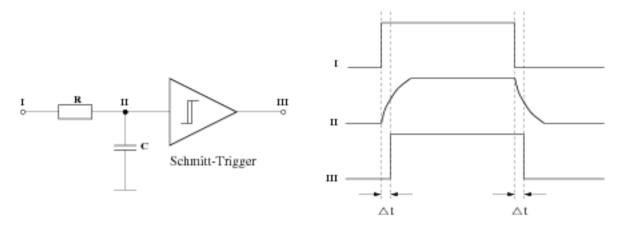

| 5.17 | Prinzip der Verzögerung eines digitalen Pulses                          | 1 |

| 5.18 | Schaltplan der Realisierung des Verzögerungswiderstandes 62             | 2 |

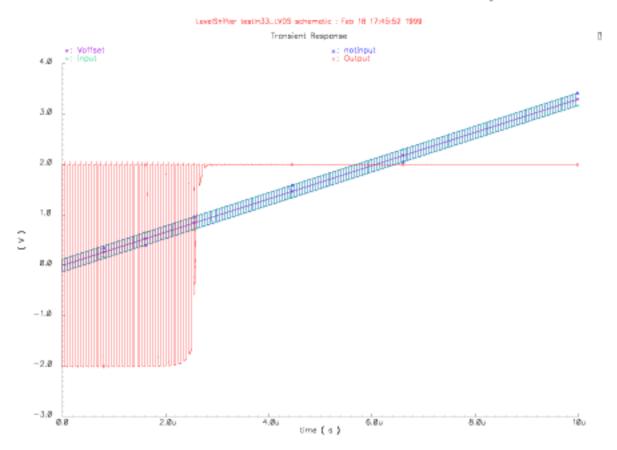

| 5.19 | Simulationsergebnis des Verzögerungselements                            | 2 |

| 5.20 | Schematische Darstellung der Adressierungskette                         | 4 |

| 5.21 | Übertragungssequenz im Single Write Mode 6                              | 4 |

| 5.22 | Übertragungssequenz im Consecutive Write Mode 6                         | 4 |

|      | Format der gesendeten 7-Bit und 10-Bit Adressen                         | 5 |

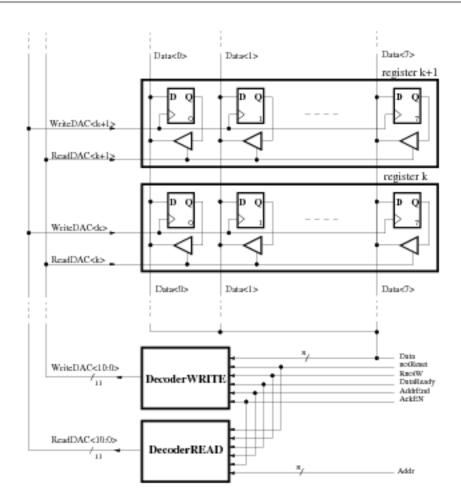

|      | Schematische Verschaltung der Dekoder und DAC-Register 60               | 6 |

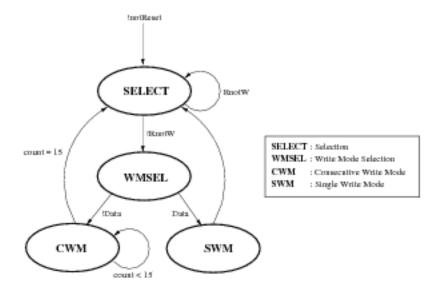

|      | Zustandsdiagramm des Schreib-Dekoders                                   | 6 |

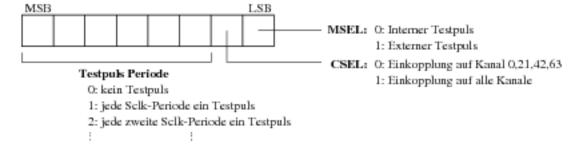

|      | Belegung des Registers $TpReg.$                                         | 7 |

|      | Belegung des Registers AnalogOut                                        | 8 |

|      | Simulationsergebnis des Adressgenerators                                | 8 |

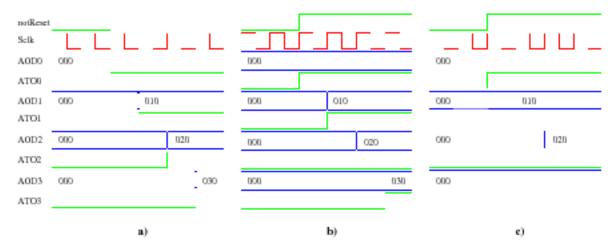

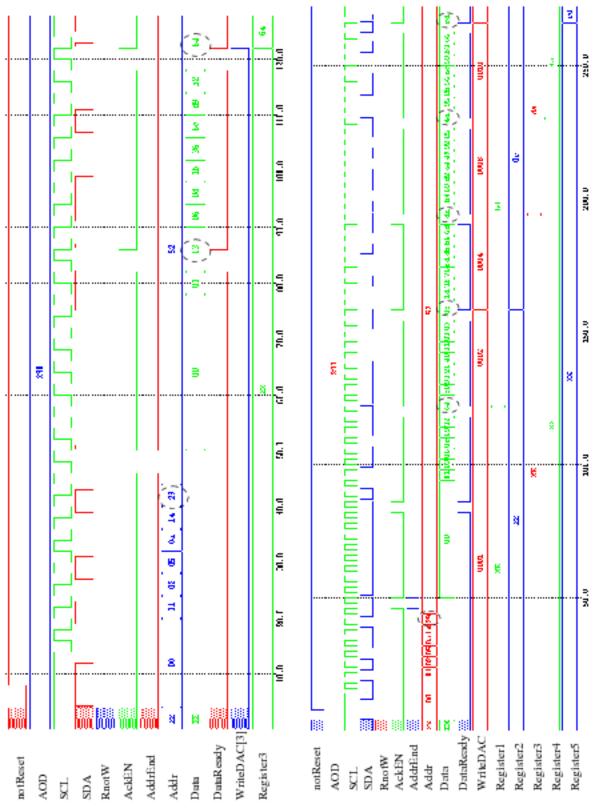

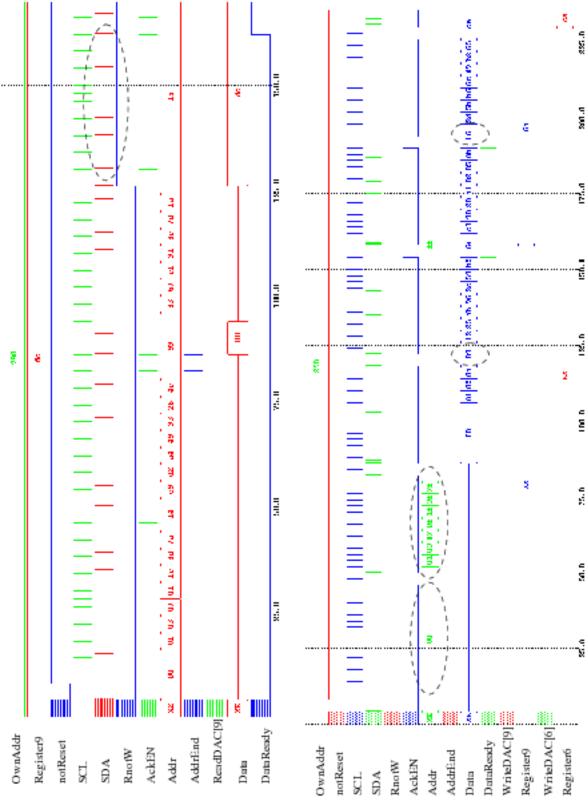

|      | Simulation des Single Write Mode                                        | 0 |

|      | Simulation des Consecutive Write Mode                                   |   |

|      | Simulation der implementierten Auslesesequenz                           |   |

|      | Simulation eines Wartezustands auf dem I <sup>2</sup> C-Bus             |   |

|      |                                                                         |   |

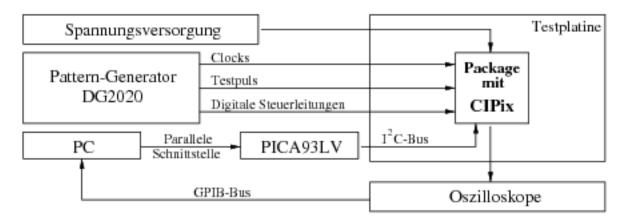

| 6.1  | Schematischer Überblick über den Meßaufbau                              | 3 |

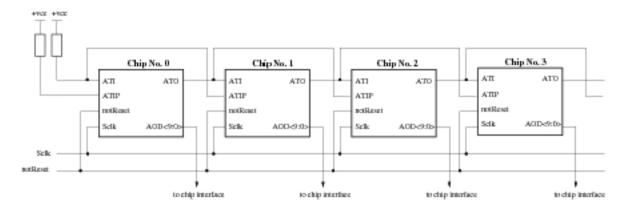

| 6.2  | CIPix-Adressvergabe                                                     | 5 |

| 6.3  | Schaltung zur Einkopplung eines Signals auf ein analoges Eingangspad 70 | 6 |

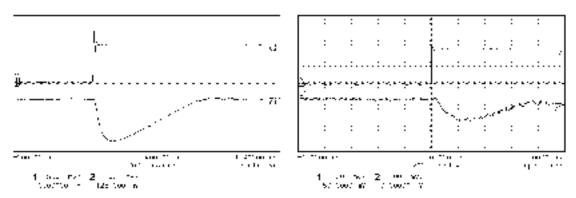

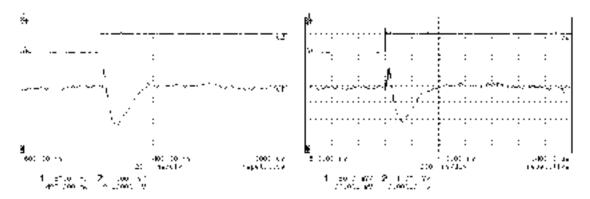

| 6.4  | Analoges Ausgangssignal ohne Lastkapazität und bei Einkopplung über ein |   |

|      | Microkoaxialkabel                                                       | 6 |

| 6.5  | Analoges Ausgangssignal bei Lastkapazitäten von 21 pF und 45 pF         | 7 |

| 6.6  | Analoges Ausgangssignal bei Lastkapazitäten von 66 pF und 100 pF        | 7 |

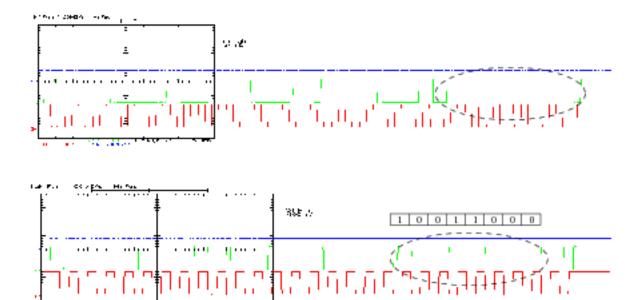

| 7.1 | Gegenüberstellung der implementierten und der spezifizierten Auslesesequenz.               | 79 |

|-----|--------------------------------------------------------------------------------------------|----|

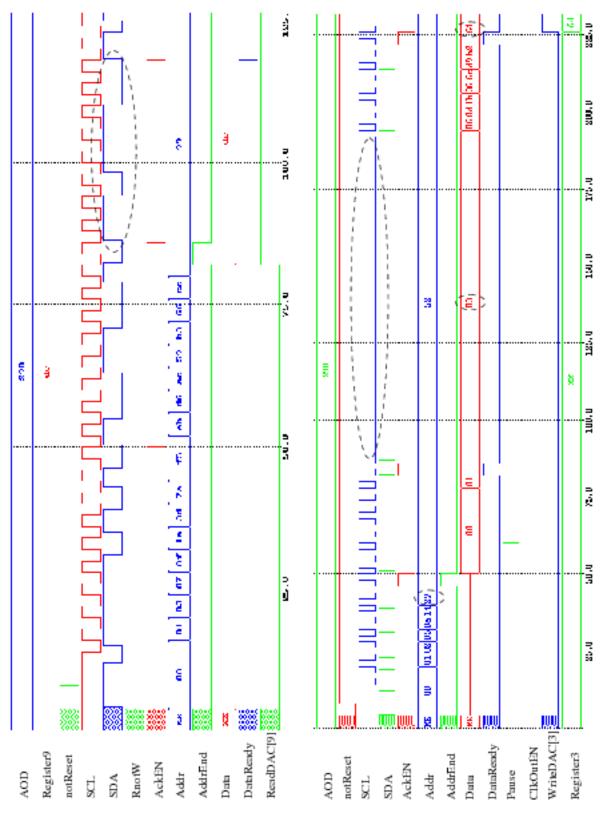

| 7.2 | Fehlerhafte I <sup>2</sup> C-Auslesesequenz                                                | 80 |

| 7.3 | Erweitertes Zustandsdiagramm der Zustandsmaschine Ctrl                                     | 81 |

| 7.4 | Erweitertes Zustandsdiagramm der Zustandsmaschine Decoder WRITE                            | 82 |

| 7.5 | Simulation der korrigierten I <sup>2</sup> C-Auslesesequenz bei einer 10-Bit Adressierung. | 83 |

| 7.6 | Simulation des korrigierten General Call-Modus                                             | 83 |

| 7.7 | Simulationsergebnis der LVDS-Receiver                                                      | 84 |

| A.1 | Schematische Zeichnung der Padanordnung des CIPix<br>1.0                                   | 88 |

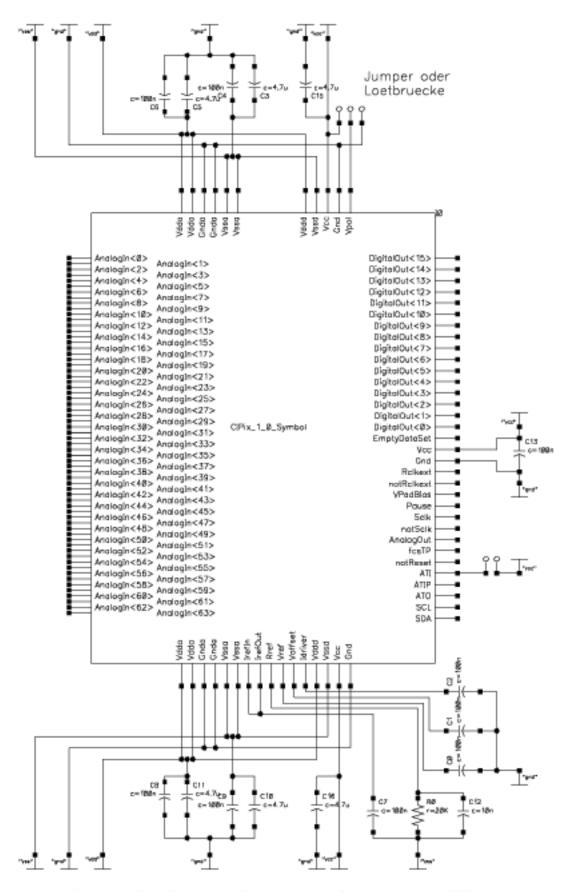

| B.1 | Externe Beschaltung des CIPix1.0                                                           | 96 |

# **Tabellenverzeichnis**

| 3.1 | Zuordnung der analogen Kanäle zu den Digitalausgängen und | ŀ | cl | k- | P | er. | io | de | m | 30 |

|-----|-----------------------------------------------------------|---|----|----|---|-----|----|----|---|----|

| 3.2 | Versorgungsspannungen des CIPix                           | - |    |    |   | -   |    | -  |   | 34 |

| 5.1 | Definition der $I^2$ C-Terminologie                       |   |    |    |   |     |    |    |   | 48 |

| 5.2 | Definition des ersten Bytes nach einer Start-Bedingung    |   |    |    |   |     |    |    |   | 51 |

| 5.3 | Externe Signale der I <sup>2</sup> C-Schnittstelle        |   |    |    |   |     |    |    |   | 56 |

| 5.4 | Interne Signale der I <sup>2</sup> C-Schnittstelle        |   |    |    |   |     |    |    |   | 58 |

| 5.5 | Ein- und Ausgangssignale des Adressgenerators             | - |    |    |   |     |    |    |   | 63 |

| 5.6 | Ein- und Ausgänge der Testpuls-Logik                      |   |    |    |   |     |    | -  |   | 67 |

| 6.1 | Belegung der internen Register des CIPix1.0               |   |    |    |   |     |    |    |   | 74 |

| 6.2 | Nominalwerte der analogen Regelspannungen und -ströme     |   |    |    |   |     |    | -  |   | 75 |

| A.1 | Pads an der Vorderseite des CIPix1.0                      |   |    |    |   |     |    |    |   | 87 |

| A.2 | Pads an der Unterseite des CIPix1.0                       |   |    |    |   |     |    |    |   | 89 |

| A.3 | Pads an der Rückseite des CIPix1.0                        |   |    |    |   |     |    |    |   | 90 |

| A.4 | Pads auf der Oberseite des CIPix1.0                       | _ |    |    |   |     |    |    |   | 91 |

| A.5 | Innere Testpads des CIPix1.0                              |   |    |    |   |     |    |    |   | 93 |

# Kapitel 1

# Einleitung

Am H1-Experiment am Elektron-Proton Speicherring HERA des Deutschen Elektronen Synchrotrons (DESY) in Hamburg wird ein breites Gebiet der Forschung im Bereich der Hochenergiephysik abgedeckt. Um neue kinematische Regionen zu erschließen, sind eine Reihe von Veränderungen am Speicherring und am H1-Detektor geplant, unter anderem eine Erhöhung der Luminosität um einen Faktor 5, sowie eine Verbesserung des H1-Detektors. Das H1-Upgrade-2000 Projekt umfaßt einen Umbau der inneren Multi Wire Proportional Chamber (MWPC) und den Einsatz einer integrierten Ausleseelektronik für diese.

Diese Diplomarbeit beschäftigt sich mit der Entwicklung und Charakterisierung des Auslesechips CIPix für die innere Proportionalkammer. Der Schwerpunkt liegt auf der Beschreibung der Entwicklung der digitalen Komponenten des Chips. Während der Arbeit wurden alle wesentlichen Schritte einer Chip-Entwicklung durchlaufen: Von der Erstellung einer Spezifikation der künftigen Eigenschaften, über die Schaltplan-Generierung und Layout-Erzeugung bis hin zum Test des produzierten Chips.

Nach einer Beschreibung des künftigen Einsatzgebietes des Chips in Kapitel 2, wird in Kapitel 3 die Architektur des CIPix1.0 vorgestellt.

Kapitel 4 zeigt Entwickungskonzepte eines digitalen Designs auf und erläutert den Entwicklungsprozeß einer digitalen Schaltung an einem Beispiel.

In Kapitel 5 werden die digitalen Komponenten des Chips ausführlich erklärt. Es werden Aufbau und Funktion beschrieben, sowie Simulationsergebnisse gezeigt.

Kapitel 6 stellt den Messaufbau und die durchgeführten Messungen vor, und präsentiert die Ergebnisse.

Während der Messungen an dieser ersten Version des Chips ergaben sich viele Verbesserungsansätze und es wurden Fehler aufgedeckt. In Kapitel 7 werden diese beschrieben.

Im Anhang A und B findet sich eine Beschreibung der Anschlüsse des CIPix, sowie ein Schaltplan für die externe Beschaltung mit Kapazitäten und Widerständen. 2 1 Einleitung

# Kapitel 2

# Das H1-Experiment

Der in der vorliegenden Arbeit beschriebene integrierte Schaltkreis dient zur Auslese der zentralen inneren Proportionalkammer (central inner proportional chamber, CIP), die Teil des H1-Detektors am Speicherring HERA<sup>1</sup> der Großforschungsanlage DESY<sup>2</sup> in Hamburg ist. Im folgenden sollen nach einer kurzen Beschreibung des Beschleunigersystems die wichtigsten Komponenten des H1-Detektors sowie die Funktionsweise des Triggersystems beschrieben werden. Im weiteren wird auf das H1-Upgrade-2000-Projekt eingegangen, wobei der Schwerpunkt auf der Beschreibung der Neuerungen der CIP liegt.

## 2.1 Der Speicherring HERA

Im Speicherring HERA, dem weltweit einzigen Beschleunigersystem dieser Art, werden Elektronen<sup>3</sup> und Protonen bei einer Schwerpunktsenergie von  $\sqrt{s_{ep}} \approx 300 GeV$  zur Kollision gebracht. Die Abb. 2.1 zeigt einen Überblick über HERA. Der Speicherring verläuft unterirdisch und hat einen Umfang von 6,3 km.

In einem System aus Linearbeschleuniger und Vorbeschleuniger (PETRA) werden Positronen und Protonen auf Energien von 12 bzw. 40 GeV gebracht. Anschließend werden diese in den Speicherring (HERA) eingekoppelt und auf die Endenergien von 27,5 GeV für die Positronen bzw. 820 GeV für die Protonen beschleunigt. Die beiden Teilchenstrahlen bestehen aus bis zu 210 einzelnen Teilchenpaketen, sogenannten "bunches". Jedes dieser Pakete besteht aus  $10^{10}$  bis  $10^{11}$  Teilchen, so daß die Ströme beider Strahlen typisch  $I_{c+}$ =20 mA und  $I_p$ =60 mA betragen. Der zeitliche Abstand zwischen zwei Paketen und damit die Zeit mit der diese aufeinandertreffen ("bunchcrossing") beträgt 96 ns. Das entspricht einer Frequenz von 10,4 MHz, der sogenannten "HERA-Clock". Diese gibt die Datenrate der von HERA durchgeführten Experimente vor und definiert den externen Referenztakt.

Die beiden Strahlen werden getrennt in zwei Hochvakuum-Strahlröhren geführt. An zwei von vier Wechselwirkungszonen werden Positronen und Protonen zur Kollision gebracht. In der Nord- und Südhalle sind die Experimente H1 und ZEUS aufgebaut, die seit Sommer 1992 Daten nehmen. Die physikalischen Fragestellungen, die in diesen beiden Experimenten untersucht werden sollen, sind im wesentlichen:

<sup>&</sup>lt;sup>1</sup>Hadron-Elektron-Ring Anlage

<sup>&</sup>lt;sup>2</sup>Deutsches Elektronen-Synchrotron

<sup>&</sup>lt;sup>3</sup>Seit Mitte 1994 werden aus technischen Gründen ausschließlich Positronen verwendet. Mit diesen lassen sich höhere Strahlströme und damit höhere Luminositäten erreichen.

Abbildung 2.1: Der Speicherring HERA am DESY in Hamburg [H1].

- Bestimmung der Protonenstrukturfunktion F<sub>2</sub>(x,Q<sup>2</sup>). x ist dabei im Quark-Parton-Modell der Impulsbruchteil des Partons am Gesamtimpuls des Protons. Q<sup>2</sup> ist das negative Quadrat des Viererimpulsübertrags.

- Untersuchung der hadronischen Struktur des Photons. Ein Photon kann in ein virtuelles Quark-Antiquark-Paar fluktuieren, das mit anderen Hadronen stark wechselwirken kann.

- Präzisionstests der Theorien zur starken und elektroschwachen Wechselwirkung.

- Suche nach Physik jenseits des Standardmodells (z. B. SUSY<sup>4</sup>, GUTs<sup>5</sup>).

Die Abb. 2.2 zeigt im linken Diagramm die von HERA produzierte integrierte Luminosität<sup>6</sup>  $\int \mathcal{L}dt$  für die Jahre 1992-1998 und Januar 1999. Im rechten Diagramm ist die für den gleichen Zeitraum von H1 akkumulierte Luminosität dargestellt. Wegen Ausfällen von Detektorkomponenten, Start- und Stop-Phasen und einer endlichen Triggereffizienz werden nur ungefähr zwei Drittel der produzierten Luminosität vom Detektor H1 für die Datennahme genutzt.

An den anderen zwei Wechselwirkungszonen wird jeweils nur einer der beiden Teilchenstrahlen verwendet. HERMES (Halle Ost) untersucht die Streuung polarisierter Elektronen an polarisierten Atomkernen. HERA-B (Halle West), das sich noch im Aufbau befindet, soll die CP-Verletzung im System der neutralen B-Mesonen nachweisen. Dazu werden Protonen

<sup>&</sup>lt;sup>4</sup>Super Symmetry

<sup>&</sup>lt;sup>5</sup>Grand Unified Theories

<sup>&</sup>lt;sup>6</sup>Die Lumnosität definiert die Intensität von Collider-Maschinen. Die Anzahl von Ereignissen einer bestimmten Klasse ist gegeben durch: N<sub>class</sub> = Aσ<sub>class</sub> ∫ Ldt, wobei A die Akzeptanz, σ der Wirkungsquerschnitt und ∫ Ldt die integrierte Luminosität ist.

### INTEGRATED LUMINOSITY

Abbildung 2.2: Von HERA produzierte integrierte Luminosität (links) und von H1 genutzte (rechts). Für das Jahr 1999 sind nur die Daten für Januar eingetragen [H1].

aus dem Halo des Protonenstrahls an Drahttargets gestreut. Eine erste Datennahme soll 1999 erfolgen.

#### 2.2 Der H1-Detektor

Der H1-Detektor (Abb. 2.3) besteht aus mehreren Komponenten, die die Wechselwirkungszone annähernd vollständig umschließen (4π-Detektor). Aufgrund der unterschiedlichen Energie der Protonen und Positronen bewegt sich das Schwerpunktsystem gegenüber dem Laborsystem. Deshalb ist der Detektor stark asymmetrisch gebaut.

Das H1-Koordinatensystem wird durch den HERA-Ring definiert. Der nominelle Wechselwirkungspunkt (Vertex) legt den Ursprung des Koordinatensystems fest (Abb. 2.4). Die z-Achse zeigt in Richtung des einlaufenden Protonenstrahls, die x-Achse zeigt auf den Mittelpunkt des Beschleunigerrings und die y-Achse nach oben. Auf diese Weise ergibt sich ein rechtshändiges Koordinatensystem. Der Azimutwinkel  $\phi$  wird von der x-Achse im Uhrzeigersinn und der Polarwinkel  $\theta$  von der z-Achse gegen die Protonenflugrichtung gemessen. Den Bereich negativer z-Koordinaten bzw. großer Polarwinkel bezeichnet man als Rückwärtsbereich.

Im folgenden Abschnitt werden die wichtigsten Komponenten des Detektors beschrieben. Eine detaillierte Beschreibung des H1-Detektors findet sich in [H1 97b]. Von der Wechselwirkungszone aus gesehen ist der H1-Detektor wie folgt aufgebaut<sup>7</sup>:

<sup>&</sup>lt;sup>7</sup>Die angegebenen Ziffern beziehen sich auf Abb. 2.3

Abbildung 2.3: Schematische Ansicht des H1-Detektors [H1]. An der Stelle des warmen elektromagnetischen Kalorimeters [12] befindet sich seit 1995 das Blei-Faser-Kalorimeter (Spacal).

Abbildung 2.4: Das H1-Koordinatensystem

#### Silizium-Vertexdetektor

Der Kollisionspunkt, sowie die Zerfallsorte von Teilchen aus der ep-Reaktion werden durch einen zweilagigen Silizium-Vertexdetektor (central silicon tracker, CST) bestimmt. Dessen intrinsische Ortsauflösung liegt bei 10 µm. Der CST ist eine Erweiterung des ursprünglichen H1-Konzeptes und erst seit 1997 voll einsetzbar.

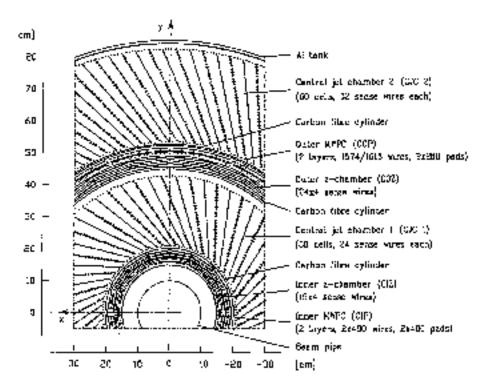

# Zentrales Spurkammersystem [2] An das Strahlrohr und den CST schließt sich ein komplexes System von sechs, konzentrischen Spurkammern an (vergrößerte Seitenansicht in Abb. 2.5, radiale Ansicht in Abb. 2.6). Ihre Aufgabe ist es, die Spur von geladenen Teilchen und ihren Winkel θ gegenüber der Strahlachse zu bestimmen. Von inneren zu äußeren Radien ist das innere Trackingsystem wie folgt aufgebaut:

- eine doppellagige Vieldrahtproportionalkammer (central inner proportional chamber, CIP)

- eine z-Driftkammer (central inner z-chamber, CIZ) zur Bestimmung der z-Koordinate von Spuren, mit einer Auflösung von 200μm.

- zwei Jet-Driftkammern CJC1 und CJC2 (central jet chambers, CJC) zur Rekonstruktion geladener Teilchenspuren in einem Winkelbereich von 30° < θ < 150°.</li>

Die Winkelauflösung beträgt σ<sub>θ</sub> ≈ 1 mrad bei einer Impulsauflösung von σ/p² ≈ 3 · 10<sup>-3</sup>GeV<sup>-1</sup>.

- eine äußere z-Driftkammer (central outer z-chamber, COZ) und eine weitere doppellagige Vieldrahtproportionalkammer central outer proportional chamber, COP), die sich zwischen den beiden CJCs befinden.

## • Vorwärtsspurkammersystem 3

Das Vorwärtsspurkammersystem wird aus drei identischen Supermodulen gebildet. Es besteht aus einer planaren und einer radialen Driftkammer sowie einem Übergangsstrahlungsdetektor und einer Vieldrahtproportionalkammer (forward proportional chamber, FPC). Durch dieses Kammersystem wird die Winkelakzeptanz für geladene Teilchen bis  $\theta$ =5° ausgedehnt.

Flüssig-Argon-Kalorimeter 4 und 5

Das Flüssig-Argon-Kalorimeter (LAr-Kalorimeter) besteht aus einer elektromagneti-

schen 4 und einer hadronischen 5 Komponente. Es erlaubt eine Energiemessung in einem Winkelbereich von  $3^{\circ} < \theta < 155^{\circ}$ . Der elektromagnetische Teil besteht aus Bleiabsorberplatten und ist, abhängig von  $\theta$ , 20-30 Strahlungslängen dick. Der hadronische Teil benutzt als Absorber Edelstahlplatten. Zwischen den Platten befindet sich flüssiges Argon als aktives Material, was die Unterbringung des Kalorimeters in einem Kryostaten bedingt.

Das Kalorimeter ist nicht kompensierend, das heißt, daß die Antwort auf Elektronen und Hadronen gleicher Energie unterschiedlich ausfällt. Durch die Lage der Schauer lassen sich beide Teilchensorten unterscheiden. Elektronen deponieren ihre Energie in den ersten Lagen des Kalorimeters, Hadronen dagegen passieren die ersten Schichten und deponieren ihre Energie in den hinteren Kalorimeterlagen. Die Energieauflösung liegt bei  $\sigma(E)/E = 12\%/\sqrt{E/GeV} \oplus 1\%$  für Elektronen und  $\sigma(E)/E = 50\%/\sqrt{E/GeV} \oplus 2\%$  für Hadronen. Die absolute Energieskala hat eine Unsicherheit von 3% für Elektronen und 4% für Hadronen.

- Vorwärtskalorimeter 13

Im Vorwärtsbereich wird der H1-Detektor durch ein Kupfer-Silizium Kalorimeter ergänzt.

Dieser sogenannte Plug-Detektor erschließt den Akzeptanzbereich von 0,7° < θ < 3,2°.</p>

- Supraleitende Spule [6]

Die supraleitende Spule erzeugt im Bereich der Spurkammern ein nahezu homogenes, axiales (parallel zur Strahlachse ausgerichtetes) Magnetfeld von 1,16 T. Dieses ermöglicht die Impulsbestimmung geladener Teilchen in den Driftkammern durch Messen der Spurkrümmung. Die Rückführung des magnetischen Flusses geschieht durch ein Eisenjoch, in dem zusätzlich Streamerkammern für den Nachweis von Myonen eingebettet sind ([9], [10]). Damit das Magnetfeld der supraleitenden Spule nicht die Teilchenbahn im Strahlrohr beeinflußt, ist am Ende des Detektors um das Strahlrohr ein supraleitender Kompensationsmagnet angebracht [7].

- Spaghetti-Kalorimeter [12]

Im Rückwärtsbereich des Detektors steht seit 1995 ein Blei-Faser-Kalorimeter (Spaghetti calorimeter, SpaCal). Es besteht aus in Bleiplatten eingebetteten, szintillierenden Fasern. Zusammen mit einer rückwärtigen Driftkammer (backward drift chamber, BDC) können damit Elektronen und Hadronen bei großen Streuwinkeln von θ = 152° 177° nachgewiesen werden.

- Luminositätssystem

Die von HERA gelieferte Luminosität wird von H1 über den Bethe-Heitler Prozeß ep $\rightarrow$ ep $\gamma$  (Bremsstrahlung) gemessen, dessen Wirkungsquerschnitt theoretisch sehr gut beschrieben ist. Die Luminosität wird über die Beziehung

$$\mathcal{L} = \frac{R_{tot} - (I_{tot}/I_0)R_0}{\sigma_{vis}}$$

bestimmt, wobei  $R_{tot}$  die gesamte, beobachtete Rate der Bremsstrahlungsereignisse ist,  $R_0$  die Rate Elektron-Pilotbunches<sup>8</sup>,  $I_{tot}$  und  $I_0$  die entsprechenden Ströme des Elektronenstrahls.  $\sigma_{vis}$  ist der mit der Akzeptanzfunktion der Detektoren und der Trigger-Effizienz gefaltete Wirkungsquerschnitt. Zwei kleine Kalorimeter, 105 m und 33 m

<sup>&</sup>lt;sup>8</sup>Elektronenpakete ohne ein Protonenpaket als Kollisionspartner.

von der Wechselwirkungszone installiert, weisen diese Photonen (Photonentagger) und Elektronen (Elektronentagger) nach.

Abbildung 2.5: Seitliche Ansicht des inneren Spurkammersystems [H1].

## 2.3 Das H1-Triggersystem

Der Trigger<sup>9</sup> hat die Aufgabe, die zahlenmäßig dominierenden Untergrundereignisse von physikalisch interessanten ep-Streuereignissen zu trennen. Zu den Untergrundquellen zählen Synchrotron-Strahlung der Positronen, Proton-Gas-Wechselwirkungen in der Beampipe<sup>10</sup> und Streuprotonen, die durch Zusammenstöße mit dem Strahlrohr und anderem Material um den Detektor Teilchenschauer erzeugen. Myonen aus dem Strahlhalo und kosmische Myonen spielen ebenfalls eine Rolle.

Die wesentlichen Aufgaben des Triggers sind es, die Datenrate auf ein für die Speicherung und Nachverarbeitung mögliches Maß zu reduzieren und die Totzeit des Detektors zu minimieren. Da die Auslese des Detektors Zeit in Anspruch nimmt und währenddessen die Auslesekette keine neue Daten annimmt, soll der Detektor im Idealfall nur für physikalisch interessante Ereignisse ausgelesen werden. Das Triggersystem besteht bei H1 aus drei unabhängigen Stufen (L1, L2, und L4), die synchron zur Datennahme ("online") arbeiten. In

<sup>&</sup>lt;sup>9</sup>Auslöser

<sup>10</sup>Strahlröhre

Abbildung 2.6: Radiale Ansicht des inneren Spurkammersystems [H1].

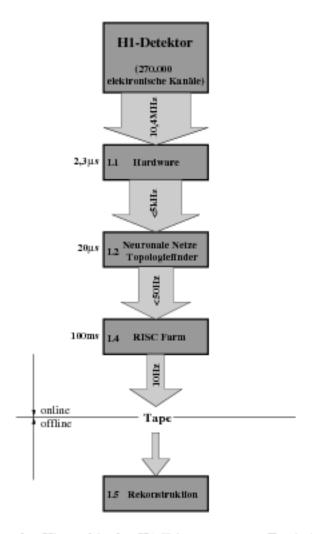

Abb. 2.7 ist die Hierarchie des H1 Triggersystems schematisch dargestellt. Es sind die Einund Ausgaberaten sowie die Entscheidungszeiten jeder Stufe gezeigt.

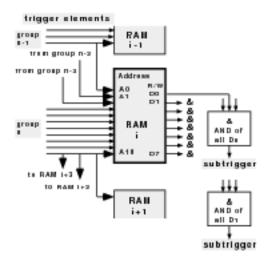

Die erste Triggerstufe (L1) wird von schnellen, in Hardware realisierten Triggerelementen gebildet. Ein Triggerelement nutzt unmittelbar nach einer Wechselwirkung verfügbare Informationen aus verschiedenen Detektorkomponenten für erste Aussagen über ein Ereignis. Diese können z. B. eine bestimmte Spurtopologie in einer Driftkammer oder das Überschreiten einer voreingestellten Schwelle für Energie-Deposition in einem Kalorimeter repräsentieren. Die Triggerelemente werden logisch miteinander zu 128 Subtriggern (Triggerelement-Koinzidenzen) verknüpft (siehe Abb. 2.3).

Diese Triggerkoinzidenzen werden elektronisch über sogenannte RAM<sup>11</sup>-Lookup-Tables gebildet. Die logischen Signale der Triggerelemente eines Subsystems werden dabei auf den Adressbus eines schnellen RAM-Bausteins gegeben, dessen 8-Bit-Speicherzellen die frei programmierbare Kombination logischer Ausdrücke der Triggerelemente ermöglichen<sup>12</sup>. Jeder Ausgang eines RAM-Bausteins kann mit Ausgängen anderer RAM-Bausteine durch UND-Gatter logisch verknüpft werden. Zusammen bilden diese eine von insgesamt 128 möglichen Subtrigger-Bedingungen. Eine erfüllte Subtrigger-Bedingung führt jedoch nicht automatisch zu der Entscheidung, daß ein Ereignis weiter behandelt werden soll ("L1 keep"). Man bedient sich eines Skalierungsverfahrens (prescaling), mit welchem nur jeweils eines aus einer voreingestellten Anzahl von Ereignissen (prescale factor), die die Subtrigger-Bedingung ausgelöst haben, tatsächlich ausgelesen wird.

<sup>&</sup>lt;sup>11</sup>Random Access Memory

<sup>&</sup>lt;sup>12</sup>In jeder Triggerkoinzidenz muß ein sogenanntes t<sub>0</sub>-Triggerelement vorhanden sein, das das zu dem anliegenden Ereignis gehörende Bunchcrossing markiert.

Abbildung 2.7: Schema der Hierarchie des H1-Triggersystems. Es sind die Ein- und Ausgaberaten, sowie die Entscheidungszeiten jeder Stufe gezeigt [Nic96].

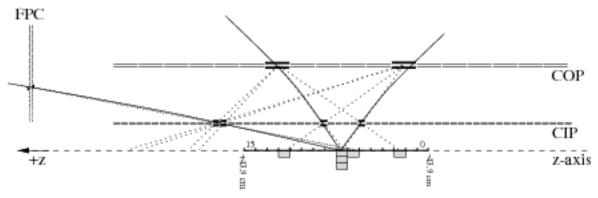

Von den verschiedenen Triggerelementen des L1-Triggers soll an dieser Stelle der z-Vertex-Trigger näher beschrieben werden. Das Prinzip der z-Vertex-Bestimmung wird in Abb. 2.9 veranschaulicht. Aus den aktivierten Pads der CIP, COP und der fMWPC werden alle möglichen Spuren rekonstruiert und in Richtung der Strahlachse extrapoliert. Alle Spuren, die ihren Schnittpunkt mit der Strahlachse im Bereich z=43,9 cm und z=-43,9 cm haben, werden in ein Histogramm eingetragen. Ein signifikanter Peak in diesem Histogramm bestimmt die z-Position des Vertex. Der z-Vertex Trigger liefert mehrere Triggerelemente. Das schwächste Element  $(T\theta)$  wird bei einem nicht-leeren Histogramm generiert.

Je nach Strahlbedingung (Strahlströme und Untergrund) wird ein Run<sup>13</sup> einer Runphase zugeordnet; diese reichen von 1 ("hohe Luminosiät, hoher Untergrund") bis 4 ("niedrige Lunimosität, niedriger Untergrund")<sup>14</sup>. Abhängig von der Runphase werden die Subtrigger

<sup>&</sup>lt;sup>13</sup>Periode der Datennahme.

<sup>&</sup>lt;sup>14</sup>Eine Ausnahme bilden Cosmic Runs und Test Runs, die u. a. zur Kalibrierung von Detektorkomponenten dienen

Abbildung 2.8: Generierung der Subtrigger durch RAM-Lookup Tables. Triggerelemente eines Subsystems werden zusammen mit den t<sub>0</sub>-Triggerelementen auf die Adressleitungen eines RAM-Bausteins gelegt. Die mittels konventioneller UND-Gatter erzeugte Koinzidenz der RAM-Ausgänge aller Subsysteme erzeugt die Subtrigger-Bedingung [Sef92].

Abbildung 2.9: Funktionsweise des z-Vertex-Triggers. Koinzidenzen von jeweils vier Proportionalkammer-Pads von CIP, COP und FPC definieren einen Spurkandidaten [HB96].

festgelegt, die ein Ereignis triggern können.

Die Triggerstufe L1 arbeitet totzeitfrei bei einer Frequenz von 10,4 MHz. Die Entscheidung ist um 2,5  $\mu$ s verzögert, da die volle Triggerinformation über ein Ereignis erst nach dieser Zeit vorliegt. Diese Zeitspanne wird bestimmt durch die längste Driftzeit in den Driftkammern ( $\approx 1 \mu$ s) und der Integrationszeit der Vorverstärker des LAr-Kalorimeters ( $\approx 1,5 \mu$ s). Die Signale der Detektorkomponenten müssen also bis zum Eintreffen einer L1-Triggerentscheidung elektronisch zwischengespeichert werden. Dies erfolgt mittels zyklisch überschriebener Ringspeicher, sogenannter "Pipelines".

Eine positive Entscheidung der Triggerstufe L1 ("L1 keep") stoppt die Pipeline und führt eine Entscheidung der nachfolgenden Triggerstufe L2 herbei. Diese benutzt topologische Informationen und neuronale Netzwerke zur Entscheidungsfindung. Mit dem Stoppen der Pipeline beginnt die Totzeit des Detektors. Eine Entscheidung von L2 liegt im Mittel nach  $20\mu$ s vor. Erst nach einer positiven Entscheidung ("L2 keep") wird die zeitaufwendige Auslese der Driftkammern und die analoge Auslese des Kalorimeters initiiert. Andernfalls wird der Ringspeicher zurückgesetzt.

Die folgende Triggerstufe L4 verifiziert die L2-Entscheidung durch eine schnelle, reduzierte Ereignisrekonstruktion. L4 besteht aus einer massiv parallelen Rechnerfarm. Die Stufe arbeitet asynchron zu den vorangegangenen Stufen und trägt daher nicht weiter zur Totzeit bei, solange eine bestimmte "L2 keep"-Rate nicht überschritten wird. Auf L4 wird zum ersten mal die gesamte zu einem Ereignis gehörende Detektorinformation zusammengeführt. Sämtliche L1-Subtrigger werden anhand der vollen Information überprüft und gegebenenfalls verworfen. Zu Kontrollzwecken werden 1% der von L4 verworfenen Ereignisse aufgezeichnet.

Die von L4 akzeptierten Ereignisse, typischerweise 10 pro Sekunde, werden der Ereignisrekonstruktion (L5) zugeführt. Die Stufe L5 arbeitet unabhängig von der Datennahme ("offline"). Hier werden die Ereignisse nach Physikklassen gegliedert.

## 2.4 Das H1-Upgrade-2000-Projekt

Für das Jahr 2000 ist geplant, ein Upgrade bei HERA durchzuführen, um die Luminosität  $\mathcal{L}$ um einen Faktor 5 gegenüber den Design-Parametern zu erhöhen. Das würde eine Vergrößerung auf  $\mathcal{L} = 1, 5 \cdot 10^{31} \, \text{cm}^2 \text{s}^{-1}$  bedeuten. Die Hauptmotivation für dieses Projekt ist das Bestreben, die zur Zeit bestehenden Experimente sensibler auf Physik außerhalb des Standardmodels zu machen und die Sensitivität auf seltene Ereignisse mit großem  $Q^2$  oder großem Transversalimpuls zu vergrößern. Die Erhöhung der Luminosität wird durch einen höheren Protonenstrom und eine bessere Fokussierung der beiden Strahlen erreicht. Eine ausführliche Beschreibung des jetzigen Stands, der Motivation und der Maßnahmen für das Upgrade befindet sich in [H1 97a].

Die bessere Fokussierung der Strahlen bedingt es, daß die zur Strahltrennung bzw. zusammenführung notwendigen Quadropolmagnete näher an den Kreuzungspunkt herangebracht werden. Für den H1-Detektor bedeutet das, daß sich die Magnete dann im Detektor

selbst befinden. Ein Magnet ragt in das Vorwärtsspurkammer-System (FTD), der andere in

das elektromagnetische und hadronische Kalorimeter (SpaCal) im Rückwärtsbereich. Eine

weitere Konsequenz der neuen Quadropolmagnete ist, daß sich die e<sup>+</sup>- und p-Strahlen unter

einem größeren Winkel im Wechselwirkungspunkt schneiden. Um zukünftig nahe genug an

das Strahlrohr heranzukommen, dennoch aber nicht die seitliche Strahltrennung zu behindern, wird die Beampipe durch ein ovales Rohr ersetzt. Weiterhin muß die Abschirmung der

Synchrotronstrahlung, das Argon-Kühlsystem sowie das Luminositäts-System komplett überarbeitet werden. Diese Veränderungen ziehen Modifikationen einiger bestehender Detektorkomponenten nach sich. Zusätzlich werden aber auch primär nicht betroffene Komponenten

im Rahmen der Upgrade-Maßnahmen verbessert.

Nachfolgend sollen die geplanten Veränderungen für den Bereich des Trackingsystems beschrieben werden:

Central silicon tracker (CST), backward silicon tracker (BST)

Der CST muß der neuen ovalen Strahlröhre angepaßt werden, wobei die vorhandenen Detektormodule wiederverwendet werden können und nur ihre Anordnung verändert wird. Die verbesserte z-Information der CIP wird in späteren Analysen der Daten dazu dienen, die dreifach Ambiguität<sup>15</sup> des CST aufzulösen.

Der BST wird mit neuen  $\phi$ -Detektoren ausgerüstet und ebenfalls an die veränderte Geometrie der Strahlröhre angepaßt.

<sup>&</sup>lt;sup>15</sup>= Mehrdeutigkeit aufgrund der Signalauslese des CST: Der CST ist in z-Richtung dreifach segmentiert. Signale aus diesen drei Bereichen werden über eine Leitung ausgelesen, wodurch eine eindeutige Zuordnung eines Signals zu einem bestimmten z-Segment nicht möglich ist.

- Central jet chamber (CJC)

Die beiden Jetkammern (CJC1 und CJC2) erhalten eine schnellere Ausleseelektronik, die es gestattet, Informationen über die invariante Masse bereits nach 20 μs für den L2-Trigger zur Verfügung zu stellen. Bisher konnte die invariante Masse erst von der Triggerstufe L4 berechnet werden.

- Central outer z-chamber (COZ), central inner z-chamber (CIZ)

Die COZ wird unverändert beibehalten. Aufgrund von Alterungsprozessen der CIZ,

bedingt durch den geringen Abstand zum Strahl, wird diese Kammer ausgebaut. Ihre

Aufgaben werden vom CST übernommen.

- Central inner proportional chamber (CIP)

Die Anzahl der Kammerlagen der CIP wird von 2 auf 5 Lagen erhöht und die Zahl der Pads in z-Richtung von 60 auf 120 verdoppelt (siehe Abschnitt 2.5 für eine ausführlichere Beschreibung). Durch diese Veränderungen erreicht man vor allem eine Verbesserung der z-Vertex-Information. Die Akzeptanz für sehr flache Spuren in Vorwärts- und Rückwärtsrichtung wird stark verbessert und macht den Ausbau einer Komponente des FTD möglich (siehe unten). Protonstrahl-Untergrundereignisse, die einen Vertex außerhalb des H1-Detektors haben, werden besser erkannt. Außerdem wird man sensitiver auf Ereignisse mit kleinem Q², bei denen das Elektron unter einem sehr flachen Winkel rückwärts gestreut wird. Die neue CIP soll in der Lage sein, die dreifache Ambiguität des CST aufzulösen, was zuvor von der CIZ wahrgenommen wurde.

- Forward track detector (FTD)

Die MWPC, eine der Komponenten der drei Supermodule des FTD, werden nicht mehr benötigt. An ihre Stelle wird eine planare Driftkammer eingebaut, die zur Feststellung der (r,z)-Komponente eines durchfliegenden Teilchens dient. Die zuvor von den MWPC gelieferte Triggerinformation bei kleinen θ wird durch die neue CIP bereitgestellt.

#### 2.5 Die alte und neue CIP

#### Die alte CIP

Die CIP ist eine dünne (0,14% Strahlungslänge) zwei Meter lange, zylindrische Vieldrahtproportionalkammer mit Kathodenauslese. Die bisher im H1-Detektor eingebaute Kammer besteht aus zwei übereinanderliegenden Lagen mit einer 8-fach Segmentierung in  $\phi$ . Die beiden Lagen sind gegeneinander um 22,5° (entspricht einem halben Segment) gedreht, wodurch effektiv eine 16-fach Segmentierung erreicht wird. Entlang der Zylinderachse befinden sich 60 Pads mit einer Länge von 3,5 cm und einer Breite von etwa 13 cm. Die Kammer ist in einer Art "Sandwich-Bauweise" aus dünnen Metallschichten und Rohazell aufgebaut.

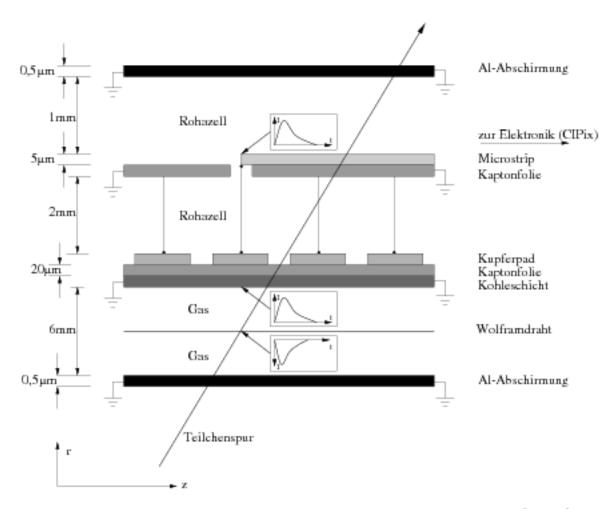

Die beiden Lagen der CIP sind identisch aufgebaut. Die radialsymmetrische Konstruktion soll im folgenden kurz beschrieben werden: Eine Kammerlage besteht aus einem 6 mm dicken Gasvolumen, in dessen Mitte vergoldete Wolframdrähte als Anoden gespannt sind. Der Gasraum wird von innen durch eine Aluminiumfolie als Kathode und von außen von einer hochohmigen Kohleschicht begrenzt. An die Kohleschicht schließt sich eine 20  $\mu$ m dicke Kaptonfolie an, auf der die Kathodenpads aufgebracht sind. Die Abmessungen der Pads betragen 3,5 cm in z-Richtung und etwa 13 cm in  $\phi$ . Die Pads werden durch die darüberliegende 2mm dicke Rohazellschicht mit den Auslesedrähten aus Aluminium kontaktiert. Den Abschluß der Kammer bilden eine  $20 \mu m$  dicke Kaptonfolie, eine  $0.5 \mu m$  dicke Aluminium-Abschirmung, eine 1 mm dicke Rohazellschicht und schließlich eine Aluminiumschicht. Letztere dient wiederum als Aluminium-Kathode der nächsten Kammerlage. Eine genaue Beschreibung der CIP findet sich in [KM92] und [MK98].

Die Hauptaufgabe der CIP ist die Lieferung der z-Vertexinformation für den L1-Trigger (zusammen mit der COP oder der ersten fMWPC<sup>16</sup>). Abb. 2.10 zeigt einen Ausschnitt der CIP und der COP, sowie die rekonstruierte Spur zwischen den aktivierten Pads beider Kammern. Die bisher verwendete CIP bietet einen erprobten und stabilen Betrieb mit Triggerinformationen für fast alle Ereignisklassen.

Abbildung 2.10: Rekonstruktion einer Spur durch aktivierte Pads in der CIP und COP [HB96].

#### Die neue CIP

#### Geometrie

Bei der neuen Kammer wird die Anzahl der Lagen von 2 auf 5 erhöht und die Zahl der Pads in z-Richtung von 60 auf 120 verdoppelt. Die Lagen sind einheitlich 16-fach in  $\phi$  segmentiert.

Der prinzipielle Aufbau der einzelnen Lagen gegenüber der alten Kammerversion bleibt unverändert: Der wesentliche Unterschied besteht in der Anpassung der Größe der Kupferpads an die erhöhte Padanzahl. Außerdem werden die Auslesedrähte der alten Kammer in der neuen Version durch Microstriplines ersetzt. Diese verlaufen durch eine Rohazellschicht getrennt auf einer Kaptonfolie über den Kupferpads. In Abb. 2.11 wird die Schichtfolge der neuen Kammerlagen gezeigt.

Die auf den Kupferpads induzierten elektrischen Signale werden über die Microstrips an die -z-Seite der Kammer geführt. Hier sitzt, neben anderer Elektronik, der Auslese-ASIC<sup>17</sup> CIPix (siehe Abb. 2.11), der die Nachverarbeitung der Kammersignale übernimmt. Dazu zählen im wesentlichen: Pulsverstärkung, Pulsformung, Digitalisierung und Multiplexing. Im Rahmen dieser Diplomarbeit wurde dieser ASIC in Zusammenarbeit mit Sven Löchner [SL98] entwickelt und getestet.

<sup>16=</sup>forward MWPC.

<sup>&</sup>lt;sup>17</sup>ASIC = Application Specific Integrated Circuit.

Abbildung 2.11: Schematischer Aufbau einer Kammerlage der neuen CIP [MK98].

#### z-Vertex Trigger

Die neue Kammer liefert eine verbesserte z-Vertex Information. Protonenstrahl-induzierte Untergrundereignisse können besser unterdrückt werden und die Akzeptanz für sehr flache Spuren in Vorwärts- und Rückwärtsrichtung wird stark erhöht. Damit verbunden ist eine größere Sensitivität für Ereignisse mit kleinem  $Q^2$ , bei denen das Elektron unter einem sehr flachen Winkel rückwärts gestreut wird.

Studien zur Vertex-Rekonstruktion und zur Unterdrückung von Untergrundereignissen durch die neue 5-lagige CIP wurden von Katharina Müller an der Universität Heidelberg durchgeführt und sollen im folgenden kurz vorgestellt werden [H198].

Zunächst wurde versucht, die Padverteilung der alten CIP durch Simulation der Ladungsverteilung in der Kammer zu reproduzieren. Man stellt fest, daß ein Großteil der aktiven Pads mit Spuren im H1-Trackingsystem korreliert. In Abb. 2.12 (a) ist die Anzahl der aktiven Pads gegen die z-Distanz zum Track für Daten<sup>18</sup> und die Simulation aufgetragen. Abb. 2.12 (b)

<sup>&</sup>lt;sup>18</sup>Für diese Untersuchungen wurden Daten aus einem speziellen Run im Jahr 1997 verwendet, bei dem nur Protonen in der HERA Maschine waren. Die Ereignisse wurden für eine Spur aus der Wechselwirkungsregion mit der schwächsten Bedingung des alten z-Vertex-Triggers (zvtx-T0) getriggert.

3000 b) 300 b) 300

zeigt die Anzahl der Pads innerhalb von 5 cm um die Spur.

Abbildung 2.12: z-Abstand aktivierter Pads zur Spur (a) und Anzahl der Pads innerhalb von 5 cm (b) für Daten (hell) und Simulation (dunkel) [H198].

Number of pads within 5 cm

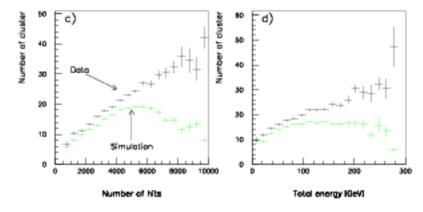

Man erkennt jedoch, daß ein Teil der aktiven Pads nicht mit gemessenen Spuren korreliert. Dies gilt vor allem für den Vorwärts- und Rückwärtsbereich. Die zusätzlichen Pads werden durch geladene Teilchen aktiviert, die infolge von Ineffizienz oder Akzeptanzverlust von den Spurkammern nicht detektiert oder rekonstruiert werden. Für Untergrunddaten verstärkt sich dieser Effekt noch, da viele sehr flache Spuren vorhanden sind. Die Anzahl dieser zusätzlichen Spuren hängt von der Topologie des Ereignisses, insbesondere von der Gesamtenergie und der Gesamtanzahl der Treffer in den Spurkammern ab (Abb. 2.13).

Abbildung 2.13: Zahl der Cluster in einer Lage der CIP gegen die Gesamtzahl an Hits im Spurkammersystem (c) und die Gesamtenergie (d) für Daten und Simulation [H198].

Für die Simulationen der neuen CIP wurde diese Abhängigkeit, sowie die z-Verteilung der aktivierten Pads berücksichtigt. Die 5-lagige CIP wurde für verschiedene Geometrien hinsichtlich der Unterdrückung von Untergrundereignissen simuliert.

Die Rekonstruktion der z-Vertex Position der Wechselwirkung liefert ein starkes Kriterium für die Seperation von Untergrundereignissen. Typische protonen-induzierte Untergrundereignisse haben eine Vertex-Position außerhalb des H1-Detektors bei z=-150...-200 cm, wohingegen die Vertex-Position von Physik-Ereignissen bei  $z=0\pm30$  cm liegt.

Die Idee eines neuen z-Vertex Triggers besteht nun darin, einen Spurfindungs-Algorithmus zu verwenden. Anders als bei der Histogrammbildung und Spitzenwertfindung des alten Triggers werden hierbei die Anzahl der von upstream kommenden Spuren (z < -70 cm) mit der Anzahl der aus der Vertexregion kommenden Spuren (z= $\pm$  50 cm) verglichen (Abb. 2.14). Mit einem einfachen Schnitt kann zwischen den beiden Ereignisklassen unterschieden werden.

Abbildung 2.14: Verteilung von upstream-Spuren (z < -70cm) gegen Vertex-Spuren (z=± 50 cm) für Physik- (b) und Untergrundereignisse (b) [H198].

Der Verlust für Physikereignisse beträgt weniger als 1%, Untergrundereignisse können mit einer Effizienz von mehr als 95% verworfen werden. Die Auflösung für die z-Vertex Position beträgt etwa 6 cm. Mit dem neuen Triggersystem kann der Protonenstrahl-Untergrund für das schwächste z-Vertex Triggerelement (zvtx-T0) um einen Faktor 20 reduziert werden. Mit Daten der neuen CIP und des CST alleine erreicht man in der Offline-Rekonstruktion eine typische Vertex-Auflösung von 0,46 cm.

# Kapitel 3

# Der CIP-Auslese-ASIC

Im nachfolgenden Kapitel soll die Architektur des CIPix1.0 beschrieben werden. Nach einer kurzen Spezifizierung des künftigen Einsatzgebietes des Chips werden die einzelnen Komponenten dem Signalfluß folgend dargestellt. Die digitalen Baugruppen werden, mit Ausnahme des Multiplexers, separat in Kapitel 5 behandelt.

Betrachtet man die alte Version der CIP-Kammer, so kommt diese bei 960 auszulesenden Pads noch mit konventioneller, d. h. nicht integrierter Ausleseelektronik aus. Die neue Kammer liefert jedoch einen Faktor 10 mehr Signale (9600). Für diese Größenordnung ist die Entwicklung eines integrierten Verstärkerschaltkreises sinnvoll. Der im Rahmen des CIP-Upgrade Projektes für die Entwicklung des Auslesechips vorgesehene Zeitraum (ungefähr ein Jahr, [Prop98]) schloß eine völlige Neuentwicklung eines ASICs aus. Stattdessen sollte versucht werden, soweit wie möglich vorhandene Komponenten ähnlicher Systeme zu verwenden. Für das Experiment HERA-B am DESY wird im ASIC-Labor Heidelberg ebenfalls ein Auslesechip entwickelt, der schon mehrere Iterationen durchlaufen hat und sich in der Massenproduktion befindet. Der Helix 128-2.2 ist ein analoger Auslesechip für den Vertexdetektor und die MSGCs<sup>2</sup> des inneren Spurkammersystems des HERA-B Detektors. Der Helix128-2.2 integriert 128 ladungsempfindliche rauscharme Vorverstärker und Pulsformer, sowie einen analogen Zwischenspeicher aus Kapazitäten. Dem Vorverstärker und Pulsformer ist ein Komparator nachgeschaltet, der beim Überschreiten einer einstellbaren Schwelle ein Triggersignal liefert. Dieses wird bei HERA-B für den First Level Trigger (FLT) verwendet. Die verstärkten und geformten analogen Signale werden über einen Multiplexer zeitlich hintereinander ausgegeben [ES97].

Sven Löchner untersuchte im Rahmen seiner Diplomarbeit [SL98], inwieweit Komponenten des Helix128 für den CIPix zu verwenden sind und modifizierte diese.

## 3.1 Überblick

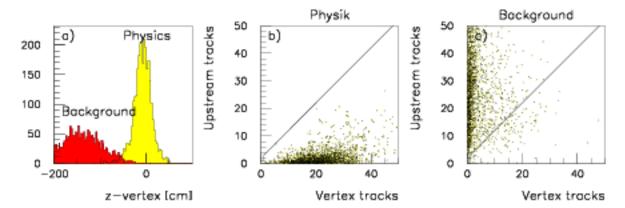

Der CIPix wurde in einem  $0.8\mu m$  CMOS-Prozeß entworfen und im Oktober 1998 von der Firma Austria Micro Systeme (AMS) produziert. Der Chip hat eine Fläche von  $4040~\mu m \times 6615~\mu m$  und integriert die folgenden Schaltkreise (siehe Abb. 3.1):

<sup>&</sup>lt;sup>1</sup>Das ASIC-Labor Heidelberg wurde 1994 gegründet und ist eine Gemeinschaftseinrichtung des Physikalischen Instituts, des Max-Planck-Instituts für Kernphysik (MPIK), des Instituts für Hochenergiephysik (IHEP) und des Instituts für Angewandte Physik.

<sup>&</sup>lt;sup>2</sup>Micro Strip Gaseous Chambers

Abbildung 3.1: Blockdiagramm des CIPix1.0.

#### 64 Kanäle bestehend aus

- einem ladungsempfindlichen rauscharmen Vorverstärker mit einem Verstärkungsfaktor von etwa 40mV/10<sup>5</sup> Elektronen.

- einem CR-RC Pulsformer (Shaper), der einen semigausschen Puls mit einer Peaktime von 50...70ns<sup>3</sup> formt.

- einer Treiberstufe (Buffer).

- einem Komparator mit einstellbarer Polarität.

- Multiplexer: Der Multiplexer arbeitet mit der vierfachen Abtastrate, d.h. 40 MHz.

Dieser Takt (Rclk) wird, wie die Abtastrate Sclk, extern zugeführt.

- Analoger Ausgangstreiber: Dieser führt einen der 64 analogen Kanäle als Stromausgang nach außen. Die Auskopplung des analogen Signals erfolgt nach dem Frontend und ist über die Programmierschnittstelle steuerbar.

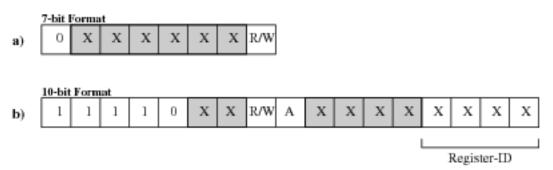

- I<sup>2</sup>C-Interface: Der CIPix benutzt das I<sup>2</sup>C-Protokoll [I<sup>2</sup>C98] zur Programmierung und zum Rücklesen der Register.

- Adressgenerator: Die Chip-Adresse wird in einem selbstprogrammierenden Verfahren vergeben. Dadurch wird vermieden, jeden Chip in unterschiedlicher Weise zu bonden<sup>4</sup>, um so eine Kennung zu erreichen.

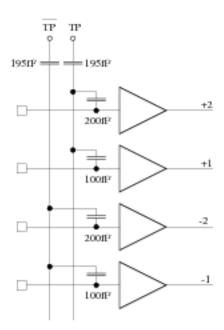

- Testpulsgenerator: Für Testzwecke lassen sich Pulse intern über Kapazitäten in die einzelnen Kanäle einkoppeln. Diese werden vom Testpulsgenerator erzeugt, der selbst über die Programmierschnittstelle gesteuert wird.

<sup>&</sup>lt;sup>3</sup>Der Scheitelwert hängt von der Lastkapazität am Eingang ab (s. u.).

<sup>&</sup>lt;sup>4</sup>Kontaktieren der Anschlußflächen eines Chips.

Bias-Generatoren: Der CIPix enthält 5 Strom- und 4 Spannungsquellen. Die Ströme und Spannungen werden durch 8-Bit DACs<sup>5</sup> generiert und dienen zur Regelung der analogen Verstärkerkomponenten.

Abb. 3.2 zeigt das Layout des Chips. Um die einzelnen Komponenten besser identifizieren zu können, wurden diese entsprechend markiert und beschriftet.

## 3.2 Die äußeren Randbedingungen

Beim Betrieb des CIPix an der MWPC<sup>6</sup> sind zwei Aspekte zu berücksichtigen. Zum einen wird der Eingang des Vorverstärkers des CIPix durch die Signalleitung kapazitiv belastet, zum anderen stellt der CIPix durch seine Eingangsimpedanz einen Terminierungs-Widerstand für die Microstrip-Leitung dar.

Der Eingangsschaltkreis des CIPix ist ein ladungsempfindlicher Vorverstärker. Diese haben die Eigenschaft, daß ihr Rauschen proportional zur Lastkapazität am Eingang ist. Für den im CIPix verwendeten Vorverstärker wurde ein Rauschen von 380e<sup>-</sup> + 38e<sup>-</sup>/pF gemessen [UT98]. Pulsformmessungen am Frontend des Helix2.0 [Pad98] zeigen, daß sich zum einen der Zeitpunkt der maximalen Signalhöhe (Peaktime) mit steigender Lastkapzität nach hinten verschiebt und zum anderen die Signalamplitude mit steigenden Lastkapzitäten abnimmt (Abb. 3.3). Dieses Verhalten hat mehrere Konsequenzen: Das Signal-zu-Rausch-Verhältnis (SNR) verschlechtert sich und die Triggerschwellen des Komparators müssen, im Verhältnis zum Rauschen, sehr klein eingestellt werden. Das wiederum bewirkt, daß der Trigger mehrere Buchcrossings anspricht. Vor diesem Hintergrund wurde die maximal zulässige Eingangskapazität auf 50pF festgelegt.

Michael Kollak entwickelte in seiner Diplomarbeit verschiedene Modelle einer Stripline-Auslese für die künftige CIP-Kammer [MK98]. In einem ersten Modell betrug die Lastkapazität für ein maximal weit vom CIPix entferntes Pad 200pF. Ein auf eine Kapazitätsminimierung optimiertes Modell liefert eine Lastkapazität für ein solches Pad von etwa 32pF.

Um Reflexionen am Ende einer Signalleitung zu vermeiden, muß diese mit ihrem Wellenwiderstand terminiert werden. Der CIPix schließt die Microstripline jedoch nicht mit dem richtigen Widerstand ab. Am CIPix-Eingang reflektierte Signale kommen dort nach einer Laufzeit von 22ns wieder an. Untersuchungen von Sven Löchner und Michael Kollak haben gezeigt, daß diese Fehlanpassung keine Konsequenzen für das Frontend hat.

## 3.3 Das Frontend: Preamplifier, Shaper, Buffer

Das im CIPix verwendete Frontend wurde für den Helix128 entwickelt und hinsichtlich dessen Anforderungen an Verstärkung, Signalform, Rauschen und Platzbedarf optimiert [WFB98]. Das Frontend gliedert sich in drei Stufen (Abb. 3.4). Preamplifier und Shaper haben prinzipiell den gleichen Aufbau, sie unterscheiden sich nur in der Dimensionierung der Transistoren.

Der Preamplifier selbst besteht aus einer Verstärker- und einer Rückkoppelstufe. Der Schaltplan ist in Abb. 3.5 dargestellt: Es wurde eine gefaltete Kaskodenschaltung verwendet. Der Transistor M3 ist im Signalpfad in Reihe zu den parallel geschalteten Eingangstransistoren Mθ und M1 geschaltet. Der Transistor M2 dient zur Einstellung des Arbeitspunktes der

<sup>&</sup>lt;sup>5</sup>DAC=Digital to Analog Converter

<sup>&</sup>lt;sup>6</sup>Multi Wire Proportional Chamber

Abbildung 3.2: Layout-Ansicht des CIPix1.0.

Abbildung 3.3: Pulsshape-Scan am Helix 2.0 mit verschiedenen Lastkapazitäten. Es wurde ein Signal von –10MIP (1MIP=24.000e<sup>-</sup>) auf Kanal 29 eingekoppelt [Pad98]. Die Zeit bis zum Pulsmaximum vergrößert sich von 52ns bei 1,5pF auf 68ns bei 40,5pF. Der Verstärkungsfaktor reduziert sich um einen Faktor 2 von 1,5pF auf 23,5pF.

Kaskodenschaltung. Durch die Spannung pre\_b1 am Gate von M2 wird dessen Widerstand variiert. M4 hat die Funktion einer Konstantstromquelle, deren Wert über die Spannung pre\_bias am Gate eingestellt wird (entspricht Ipre in Abb. 3.4). Die Transistoren M6 und M7 bewirken einen Spannungsoffset am Ausgang. Der Rückkoppeltransistor M5 hat die Aufgabe, die Kapazität C1 zu entladen. Dadurch wird verhindert, daß sich die Rückkoppelkapazität durch mehrere aufeinanderfolgende Pulse auflädt und so der Verstärker in den Sättigungsbereich gerät. Die Spannung Vfp am Gate von M5 regelt dessen Widerstand und bestimmt so die Zeitkonstante der Entladung.

Der auf das analoge Eingangspad eingekoppelte Ladungspuls wird auf das Gate der beiden Eingangstransistoren  $M\theta$  und M1 geführt und durch die Rückkoppelkapazität C1 invertierend integriert. Die Kapazität zwischen Preamplifier und Shaper bildet mit dem Widerstand des Rückkoppeltransistors des Shapers einen Hochpaß. Dieser differenziert das Signal, bevor es erneut durch den Shaper invertierend integriert wird. Die sich anschließende Treiberstufe (Buffer) ist als einfacher Source-Folger realisiert und erniedrigt den Innerwiderstand auf circa 1 k $\Omega$ .

Die Verstärkung des Vorverstärkers berechnet sich alleine aus der Rückkoppelkapazität nach  $U = \frac{Q_{in}}{C}$ . Für  $10^5$  eingekoppelte Elektronen am Eingang ergibt sich für C1=342 fF eine Ausgangsspannung von U=47 mV.

Im folgenden soll der Einfluß der einzelnen Regelspannungen und -ströme des Frontends auf die Signalform erläutert werden:

Abbildung 3.4: Blockschaltbild der analogen Eingangsstufe. Deutlich zu erkennen ist der dreiteilige Aufbau.

## Vorverstärker-Biasstrom Ipre

Ipre bestimmt die Anstiegsgeschwindigkeit der Spannung am Ausgang des Vorverstärkers. Ein größerer Strom bewirkt eine längere Anstiegszeit und damit verbunden eine größere Amplitude des Ausgangssignals, da der Vorverstärker durch einen Bandpaß beschrieben werden kann. Ein grösserer Wert von Ipre reduziert zudem den Unterschwinger.

## Vorverstärker-Biasspannung Vfp

Vfp steuert die Größe des Rückkoppelwiderstandes, der für eine Entladung der Rückkoppelkapazität sorgt und somit verhindert, daß der Verstärker in Sättigung gerät. Ist die Zeitkonstante dieses RC-Gliedes groß gegen die Integrationszeit des Pulsformers befindet sich der Verstärker im linearen Bereich und Vfp hat keinen Einfluß auf die Pulsform.

## Pulsformer-Biasstrom Isha Isha hat den gleichen Einfluß auf den Pulsformer wie Ipre auf den Vorverstärker.

### Pulsformer-Biasspannung Vfs

Vfs steuert die Größe des Rückkoppelwiderstand des Pulsformers wodurch die Integrationszeit des Shapers bestimmt wird. Ein grösserer Wert von Vfs erniedrigt den Widerstand und der Puls fällt schneller auf die Basislinie ab. Dadurch wird auch die Amplitude am Ausgang erniedrigt, da nicht alle Ladungsträger am Eingang aufintegriert werden können.

# Treiber-Biasstrom Ibuf Ibuf hat keinen Einfluß auf die Pulsform.

Typische Werte für die Regelspannungen und -ströme mit denen der CIPix bei den Messungen programmiert wurde, sind in Tabelle 6.2 in Kapitel 6 aufgeführt.

Abbildung 3.5: Schaltplan des Vorverstärkers [WFB98].

## 3.4 Der Komparator

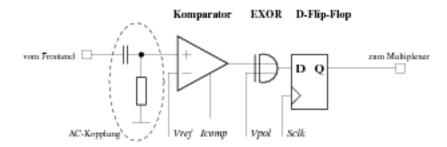

Der Komparator wurde von B. Glass [BG97] für den Helix128 entwickelt und von S. Löchner [SL98] für den CIPix modifiziert. Er hat die Aufgabe, aus dem verstärkten und geformten analogen Eingangssignal beim Überschreiten einer einstellbaren Referenzspannung ein digitales Signal zu erzeugen. Die Komparatorschaltung setzt sich aus einer AC-Kopplung, dem Komparator selbst, einem EXOR-Gatter und einem D-Flip-Flop zusammen (Abb. 3.6).

Abbildung 3.6: Schematischer Aufbau der Komparatorstufe.

## AC-Kopplung

Eine AC-Kopplung dient dazu, die Gleichspannungskomponente eines Signales zu unterdrücken. Der CIPix nutzt die AC-Kopplung aus, um Offsetvariationen zwischen verschiedenen Kanälen zu beseitigen, mit dem Ziel, bei allen Kanälen die gleiche Referenzspannung zu verwenden.

Eine gebräuchliche Art der Realisierung einer solchen Kopplung ist ein Hochpaß. Ein CR-Glied mit hinreichend tiefer Grenzfrequenz (d. h. großer Zeitkonstante  $\tau$ =RC) entkoppelt niedrige Frequenzen und unterdrückt so den Gleichspannungsanteil des Signals. Die angestrebte Zeitkonstante liegt in der Größenordnung von einigen Mikrosekunden.

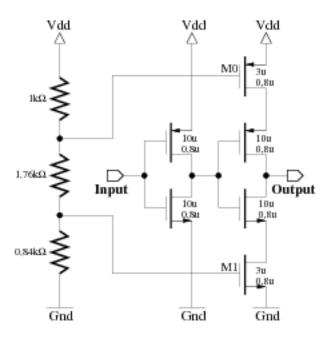

Bei integrierten Schaltkreisen können Kapazitäten in der Größenordnung von 100 fF bis 10 pF hergestellt werden. Kleinere Kapazitäten werden vergleichbar mit parasitären Effekten, größere Werte haben einen zu großen Platzbedarf. Der benötigte Widerstand liegt in der Größenordnung von 1 M $\Omega$ . Ohmsche Widerstände werden durch Bahnen aus einem möglichst hochohmigen Material realisiert. Bei dem verwendeten Prozeß besitzt die Polysiliziumschicht "Poly-2" den größten Flächenwiderstand mit  $R_{\Box}^{poly2} = 27\frac{\Omega}{\Box}$ ". Ein Poly2-Widerstand hätte dann bei einer minimalen Breite von 1,6  $\mu$ m eine Länge von  $l = \frac{R}{R_{\Box}^{poly2}} = 37mm$ . Bei Chipabmessungen von einigen Millimetern ist das völlig ausgeschlossen. Stattdessen benutzt man zwei Transistoren mit großer Kanallänge L (Abb. 3.7), um einen großen Widerstand (R $\geq$  M $\Omega$ ) zu realisieren.

Abbildung 3.7: Schaltplan der AC-Kopplung des Komparators. Die beiden Transistoren bilden einen Widerstand in der Größenordnung 2 MΩ [WFB98].

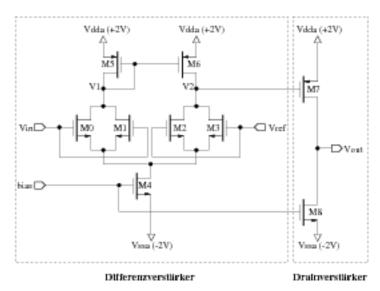

## Komparator

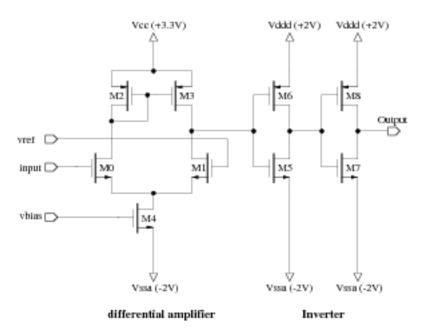

Der Komparator ist aus einer Differenzstufe und einem Drain-Verstärker aufgebaut (Abb. 3.8). Die Transistoren M4 und M8 arbeiten als Konstantstromquellen. M4 bewirkt, daß die Summe der Ströme durch die beiden Zweige (M0, M1) und (M2, M3) konstant bleibt.

Im Ruhezustand sind die beiden Eingangsspannungen Vin und Vref gleich groß und der Referenzstrom  $I_{D_4}$  teilt sich aus Symmetriegründen auf die beiden Zweige auf.

Der "selbststeuernde" Transistor M5 (Gate und Drain sind miteinander verbunden) verhält sich im Sättigungsbereich wegen  $R_{DS} = \frac{U_{DS}}{I_D}$  und  $U_{GS} \sim I_D$  wie ein ohmscher Widerstand.

Die Spannungen  $V1 = V_{dda} - V_{DS_5} = \tilde{V}^2 = V_{dda} - V_{DS_6}$  bleiben solange konstant, wie die Ströme durch beide Zweige sich nicht ändern. Auch bei einer Änderung der Eingangsspannungen um den gleichen Wert (Gleichtaktunterdrückung) bleiben die Potentiale an diesen Knoten

Oer Flächenwiderstand ist als Widerstand pro Anzahl der Flächenquadrate einer Leiterbahn definiert. Ist W die Breite und L die Länge der Bahn, so gilt: R<sub>□</sub> = R ∪ R ∪ L.

gleich. Erst bei einer relativen Änderung der Eingangsspannungen ändert sich die Stromaufteilung in den Zweigen. Ist Vref > Vin, nimmt der Strom im rechten Zweig zu, im linken ab. Die Summe bleibt jedoch konstant gleich  $I_{D_4}$ . Damit sinkt  $I_{D_5} \sim V1 = V_{GS_5} = V_{GS_6}$ . Für M6 gilt  $R_{DS_6} \sim \frac{V_{DS_5}}{I_{D_6}}$ . Wenn  $V_{GS_6}$  sinkt, vergrößert sich  $R_{DS_6}$  und  $V2 = V_{dda} - V_{DS_6}$  sinkt. Die Spannung V2 regelt den Widerstand des Transistors M7, der als Drain-Verstärker

Die Spannung V2 regelt den Widerstand des Transistors M7, der als Drain-Verstärker arbeitet. Der Arbeitspunkt wird über den Widerstand des Transistors M8 eingestellt. Sinkt die Spannung V2 verringert sich der Widerstand von M7, was zu einer höheren Ausgangsspannung Vout führt.

Abbildung 3.8: Schaltplan des differentiellen Komparators [BG97].

Nachfolgend sollen die Spannungs- und Strom-Parameter des Komparators erläutert werden:

- Die Referenzspannung Vref bestimmt die Schaltschwelle des Komparators. Der Wert ist über die I<sup>2</sup>C-Schnittstelle im Bereich von −200 mV bis +200 mV mit einer Schrittweite von 1,5625 mV programmierbar. Die von den Bias-Generatoren erzeugte Spannung zwischen −2 V und +2 V wird durch einen Spannungsteiler um den Faktor 10 reduziert.

- Der Komparator-Biasstrom Icomp bestimmt den Referenzstrom für die beiden Konstantstromquellen. Ein grösserer Strom erhöht die Verstärkung und damit die Geschwindigkeit des Komparators.

Typische Werte für Vref und Icomp werden in Tabelle 6.2 in Kapitel 6 angegeben.

#### EXOR

Ein EXOR<sup>8</sup> kann als "optionaler" Inverter aufgefaßt werden: Liegt eine 0 am Steuereingang ist der Ausgang gleich dem Wert des Signaleingangs. Liegt eine 1 am Steuereingang nimmt der Ausgang den invertierten Wert des Signaleingangs an.

<sup>&</sup>lt;sup>8</sup>Exclusive OR:  $a \oplus b = \overline{a}b + a\overline{b}$

Im CIPix wird diese Eigenschaft eines EXORs dazu benutzt, Eingangssignale beider Polaritäten behandeln zu können. Durch die externe Spannung Vpol kann die invertierende oder nicht-invertierende Funktion des Gatters selektiert werden. Dabei entspricht ein Spannungswert von 3,3 V einer logischen 1 und ein Pegel von 0 V logisch 0.

## D-Flip-Flop

Das D-Flip-Flop dient zur Synchronisation des EXOR-Ausgangs mit der steigenden Flanke der Sampling-Clock Sclk. Für den Trigger ist es wichtig, daß ein Triggersignal zum Zeitpunkt der steigenden Flanke von Sclk anliegt. Ist das Komparatorsignal nicht zeitgleich mit der Sclk-Flanke, wird es bis zur nächsten aktiven Flanke im Fip-Flop zwischengespeichert.

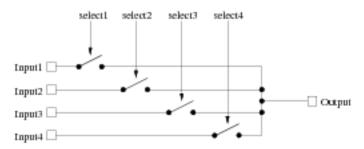

## 3.5 Der Multiplexer

Das Prinzip eines Multiplexers [SL98] besteht darin, mehrere Eingangssignale in einer zeitlichen Abfolge auf einen Ausgang zu führen (Abb. 3.9). Dadurch reduziert man die Anzahl der Signalleitungen.

Abbildung 3.9: Funktionsprinzip eines Multiplexers.

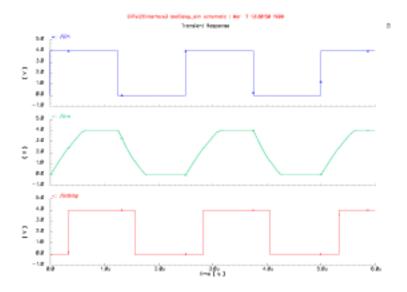

Im CIPix werden vier Komparatorausgänge periodisch auf einen Digitalausgang des Chips geführt. Die Periodendauer des Auslesetaktes Relk beträgt 25ns. Wichtig ist hierbei, daß der Takt Relk phasengleich mit Selk ist. Um einen ordnungsgemäßen Betrieb des Multiplexers zu gewährleisten, muß eine gewisse Anfangsbedingung erfüllt sein: Nach einem Reset-Signal (notReset geht auf 1) muß eine positive Flanke von Selk und Relk folgen (Abb. 3.10).

Der Multiplexer des CIPix ist zweistufig aufgebaut. In einer ersten Stufe werden aus dem Auslesetakt die Signale generiert, die einen der vier Eingänge selektieren. Abb. 3.10 stellt die zeiliche Abfolge der Selektionsleitungen select[3:0] dar. Es ist jeweils nur eines der vier Signale für die Dauer einer Periode aktiv. Im zweiten Teil der Schaltung erfolgt die eigentliche Aneinanderreihung der Eingangsignale (Abb. 3.11). Der Multiplexer-Ausgang wird zudem durch ein Flip-Flop mit der negativen Flanke des Taktes Rclk synchronisiert.

Die Zuordnung einer Kanalnummer zu einem Digitalausgang und einer Relk-Periode kann der Tabelle 3.1 entnommen werden.

Zusätzlich wird im Multiplexer ein weiteres Ausgangssignal des CIPix generiert. Das Signal EmptyDataSet soll nachfolgenden Stufen in der Auslesekette anzeigen, ob überhaupt ein Komparator ein Triggersignal erzeugt hat. Dazu wird eine ODER-Verknüpfnung aller 64 Komparator-Ausgänge gebildet. Wurde mindestens ein Triggersignal auf einem Kanal erzeugt, ist EmptyDataSet 1, ansonsten 0.

Abbildung 3.10: Multiplexer-Startbedingung und zeitliche Abfolge der Selektionsleitungen [SL98].

Abbildung 3.11: Schaltplan der Multiplexerstufe [SL98].

## 3.6 Der Analog-Ausgang

Der CIPix soll primär Triggerinformationen liefern. Deshalb werden die analogen Eingangssignale digitalisiert. Um die Arbeitsweise des Chips und Vorgänge in der Kammer besser überwachen zu können, wurde jedoch die Möglichkeit vorgesehen, einen der 64 analogen Eingangskanäle nach dem Frontend auszukoppeln und über einen Stromtreiber [WFB98] nach außen zu führen. Die Auswahl eines Kanals erfolgt durch Programmierung des Registers AnalogOut über die I<sup>2</sup>C-Schnittstelle. Entsprechend dem Registerwert wird einer der 64 Schalter, die als n-MOS Transistoren realisiert sind, geschlossen. Es ist vorgesehen die analogen Ausgänge mehrerer Chips über ein Kabel auszulesen. Ein zusätzlicher Schalter regelt deshalb den konfliktfreien Zugriff auf diesen analogen Bus. Der Schalter ist durch ein sogenanntes Transmission-Gate realisiert und wird vom MSB des Registers AnalogOut gesteuert.

| Digital-Ausgang | Rclk-Periode |    |    |    |

|-----------------|--------------|----|----|----|

|                 | 1            | 2  | 3  | 4  |

| 0               | 0            | 16 | 32 | 48 |

| 1               | 1            | 17 | 33 | 49 |

| 2               | 2            | 18 | 34 | 50 |

| 3               | 3            | 19 | 35 | 51 |

| 4               | 4            | 20 | 36 | 52 |

| 5               | 5            | 21 | 37 | 53 |

| 6               | 6            | 22 | 38 | 54 |

| 7               | 7            | 23 | 39 | 55 |

| 8               | 8            | 24 | 40 | 56 |

| 9               | 9            | 25 | 41 | 57 |

| 10              | 10           | 26 | 42 | 58 |

| 11              | 11           | 27 | 43 | 59 |

| 12              | 12           | 28 | 44 | 60 |

| 13              | 13           | 29 | 45 | 61 |

| 14              | 14           | 30 | 46 | 62 |

| 15              | 15           | 31 | 47 | 63 |

Tabelle 3.1: Zuordnung der analogen Kanäle (0–63) zu den Digitalausgängen (0–15) und Relk-Perioden.

## 3.7 Der Testpuls-Generator

Mit Testpulsen hat man ein Mittel zur Hand, unabhängig von den analogen Eingangssignalen, die Auslesekette des CIPix zu testen. Dazu wird über eine Kapazität auf dem Chip ein deltaförmiger Ladungsimpuls in den Vorverstärker eingekoppelt. Die Einkoppelstufe ist so konstruiert, daß auf vier benachbarte Kanäle jeweils unterschiedliche Ladungen gegeben werden. Bei einem Spannungshub von 4 V werden Ladungen von  $Q = +10^5 e^-$ ,  $Q = +5 \cdot 10^4 e^-$ ,  $Q = -10^5 e^-$  und  $Q = -5 \cdot 10^4 e^-$  eingekoppelt. Abb. 3.12 verdeutlicht das Schema, welches sich periodisch wiederholt.

Es wurden mehrere Modi der Testpulseinkopplung realisiert. Zum einen kann zwischen einer internen Generierung eines Pulses und der Einkopplung von außen über das Pad fcsTP gewählt werden. Zum anderen kann ein Testpuls auf alle 64 oder auf vier ausgewählte Kanäle (0, 21, 42, 63) gegeben werden. Die Einkopplung auf nur vier Kanäle hat den Vorteil, daß in Abhängigkeit der eingestellten Komparator-Schwelle, maximal ein weiterer Kanal neben dem gerade betrachteten schaltet. Somit kann ein Übersprechen von anderen Kanälen vermieden werden.

Die oben genannten Testpulsmodi lassen sich durch Programmieren des Registers TpReg über die I<sup>2</sup>C-Schnittstelle selektieren. Die internen Testpulse werden von einer Steuerlogik abgeleitet, die in Kapitel 5 ausführlicher erklärt wird.

Abbildung 3.12: Schema der Testpulseinkopplung.

## 3.8 Die Bias-Generatoren

Die Biasgeneratoren [UT99] haben die Aufgabe, die für die Regelung des Frontends, des Komparators und des analogen Ausgangstreibers notwendigen Spannungen und Ströme zu liefern. Der CIPix besitzt 5 Strom- und 4 Spannungsquellen. Die Ströme und Spannungen werden von 8-Bit DACs generiert, die über die I<sup>2</sup>C-Schnittstelle programmiert werden.

## Die Biasstrom-Quellen

Die Stromquellen arbeiten mit einer Auflösung von 2,5  $\mu$ A/LSB. Ein Registerwert von 0 entspricht einem Ausgangsstrom von 0 A. Um eine korrekte Arbeitsweise zu gewährleisten benötigen die Stromquellen einen Referenzstrom von 100  $\mu$ A, der in das Pad IrefIn fließen muß. Dieser Referenzstrom kann entweder extern zugeführt werden oder intern durch eine Referenzquelle generiert werden. Wird die interne Stromquelle benutzt, muß ein 20 k $\Omega$  Widerstand vom Pad Rref gegen Vssa (-2 V) gelegt werden und das Ausgangspad IrefOut direkt mit dem Eingangspad IrefIn verbunden werden (siehe Anhang B).

## Die Biasspannungs-Quellen

Die Spannungsquellen arbeiten mit einer Auflösung von 15 mV/LSB im Spannungsbereich von -2 V bis +2 V. Ein Registerwert von 0 entspricht einer Ausgangsspannung von -2 V.

## 3.9 Die Pads

Der CIPix arbeitet intern mit Spannungen von -2 V (Vss) bis +2 V (Vdd). Bei den Spezifikationen zum Chip wurde die Philosophie verfolgt, nach außen hin für digitale Signale

nur CMOS-Spannungspegel von 0 bis 3,3 V zu verwenden. Das macht eine Anpassung beider Pegelbereiche durch sogenannte Levelshifter notwendig. Insgesamt besitzt der CIPix vier verschiedene Typen von digitalen Anschlusspads, für die M. Feuerstack-Raible jeweils einen Levelshifter entwickelte [MFR98b]:

- Eingangs-Levelshifter f

ür die Pads ATI, ATIP, notReset, fcsTP, Pause und Vpol.

- Ausgangs-Levelshifter f

ür die Pads ATO, DigitalOut/15:0/ und EmptyDataSet.

- Bidirektionale Levelshifter f

ür die Pads SCL und SDA.

- LVDS<sup>9</sup>-Eingangs-Levelshifter f

ür die Pads Sclk, Sclk, Rclk und Rclk.

## Eingangs-Levelshifter

Ein Schaltplan des Eingangs-Levelshifter ist in Abb. 3.13 dargestellt. Man erkennt deutlich den zweiteiligen Aufbau. Die erste Stufe ist ein Differenzverstärker, in dem die Eingangsspannung mit dem Referenzwert vref verglichen wird. Das Ausgangssignal der Differenzstufe wird auf eine Inverterkette geführt, die die Pegel auf ±2 V anpaßt. Die Regelspannungen vbias und vref haben Werte von 2,5 V und 1,65 V und werden intern durch einen Spannungsteiler aus Vcc generiert.

Abbildung 3.13: Schaltplan des Eingangs-Levelsifters [MFR98b].

<sup>&</sup>lt;sup>9</sup>LVDS = Low Voltage Differential Signaling. Bei dieser Methode der Datentbertragung nutzt man die Amplitudendifferenz (Swing) zweier differentieller Signale als Information (Differentielle Signale besitzen entgegengesetzte Amplituden). Der Vorteil dieser Methode liegt in einem reduzierten Leistungsverbrauch und einer Unempfindlichkeit gegenüber Rauschen, da Störungen auf beiden Signalen in gleicher Weise induziert werden (common-mode noise).

3.9 Die Pads 33

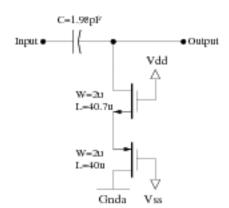

#### Ausgangs-Levelshifter

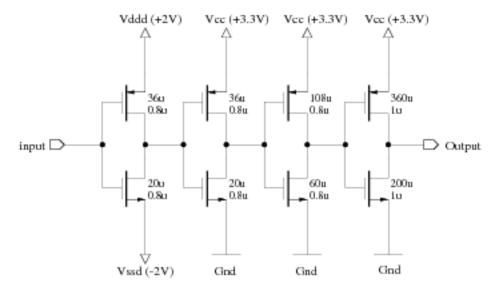

Der Ausgangs-Levelshifter besteht aus einer Kette von vier Invertern (Abb. 3.14). Der erste Inverter arbeitet zwischen  $\pm 2$  V, alle weiteren zwischen 0 und 3,3 V. Die Dimensionierung der Transistoren wird von Stufe zu Stufe größer.

Abbildung 3.14: Schaltplan des Ausgangs-Levelshifter. Die Zahlen an den Transistoren geben Breite (W) und Länge (L) an. Die Dimensionierung wird von Inverter zu Inverter größer [MFR98b].

#### Bidirektionale Levelshifter

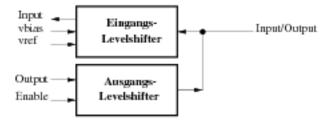

Die bidirektionalen Levelshifter werden für die beiden I<sup>2</sup>C-Leitungen SCL und SDA eingesetzt. Hierfür ist es notwendig, eine Tristate-Funktion<sup>10</sup> zu implementieren. Das bedeutet, daß durch ein Steuersignal der Ausgang in einen hochohmigen Zustand gebracht werden kann. Der Levelshifter ist eine Kombination der zuvor beschriebenen Eingangs- und Ausgangs-Levelshifter. Zusätzlich kann jedoch der Ausgang durch ein Steuersignal abgeschaltet werden (Abb.3.15).

Abbildung 3.15: Schematischer Aufbau der bidirektionalen Levelshifter [MFR98b].

<sup>&</sup>lt;sup>10</sup>Die Motivation hierfür wird in Kapitel 5 gegeben.

## LVDS-Eingangs-Levelshifter

Der LVDS-Eingangs-Levelshifter ist baugleich zu dem oben beschriebenen Eingangs-Levelshifter. Anstelle der Regelspannung vref wird jedoch das invertierte Eingangssignal auf den Differenzeingang geführt.

## 3.10 Die Spannungsversorgung

Die analogen und digitalen Spannungsnetze sind auf dem CIPix streng voneinander getrennt. Insgesamt existieren sieben verschiedene Spannungen, die in Tabelle 3.2 zusammengestellt sind.

| Symbol | Elektrischer Pegel | Beschreibung                          |

|--------|--------------------|---------------------------------------|

| Vdda   | +2V                | Positive analoge Versorgungsspannung  |

| Vssa   | -2V                | Negative analoge Versorgungsspannung  |

| Gnda   | 0V                 | Analoge Masse                         |

| Vddd   | +2V                | Positive digitale Versorgungsspannung |

| Vssd   | -2V                | Negative digitale Versorgungsspannung |

| Gnd    | 0V                 | Digitale Masse                        |

| Vcc    | 3.3V               | Digitale I/O Versorgungsspannung      |

Tabelle 3.2: Versorgungsspannungen des CIPix.

Der analoge Massenanschluß Gnda soll mit der Detektormasse verbunden werden, um so eine gemeinsame Potentialreferenz von Chip und Detektor zu gewährleisten. Durch die Trennung der Spannungen auf dem Chip will man ein Übersprechen von digitalen Schaltstörungen auf analoge Komponenten, vor allem auf den Vorverstärker, verhindern. Außerhalb des Chips können die analogen und digitalen Versorgungsspannungen gemeinsam zugeführt werden. Allerdings sind die einzelnen Leitungen durch Kapazitäten gegen Störungen abzublocken. Im Anhang B ist ein Plan für die externe Beschaltung des Chips mit Blockkapazitäten gezeigt.

## Kapitel 4

# Digital-Design

Im folgenden Kapitel sollen nach einer kurzen Einführung in die CMOS-Technologie Prinzipien und Methoden der Entwicklung eines digitalen Designs dargestellt werden. Anschließend wird die Schaltungsentwicklung mit Hilfe der Hardwarebeschreibungssprache Verilog und der CAD<sup>1</sup>-Software Cadence [Cad] beschrieben.