#### Helmut Klär

Triggerbare Signalgeneratoren für einen Pipeline TDC (Time Digital Converter)

> eingereicht als Diplomarbeit am 15.3.1989

Betreuer: Professor Dr. Peter Pernards Korreferent: Professor Dr. Specht

Fachhochschule Hamburg - Fachbereich Elektrotechnik

DESY behält sich alle Rechte für den Fall der Schutzrechtserteilung und für die wirtschaftliche Verwertung der in diesem Bericht enthaltenen Informationen vor.

DESY reserves all rights for commercial use of information included in this report, especially in case of filing application for or grant of patents.

"Die Verantwortung für den Inhalt dieses Internen Berichtes liegt ausschließlich beim Verfasser"

#### Abstract

The Flash-TDC can be regarded as an access to new methods of pipelined time measurements with an accuracy of some ten picoseconds. Conventional technics are limited either by a considerably worse time resolution, or by the small-scale range of measurements with comparable resolution combined with the inability to measure multiple signals. In this work the development is described which was needed for the test and analysis of a system of 16 parallel 100 MHz FTDC-channels.

The FTDC needs a generator which supplies a stable and linear ramp signal with a risetime of the clock period. Different circuits have been investigated producing a ramp signal with a risetime of about 10 ns. For application in the test measurements an integrator circuit has been chosen, which uses the line driver MC 10192 as a constant current source. This circuit is a kind of optimum with respect to stability and simplicity. It has been realized on a board with 16 parallel channels. This 16-channel system has been commissioned and analysed. Systematic errors due to digitization of the FADC and nonlinearity of the ramp signal have been determined and corrected for.

Time measurements carried out with the system gave resolutions in the range of 22-28 ps for the 16 different channels. Multiple signals on a single channel are measured if they differ by more than 40 ns. The depth of the pipeline was limited by the memory size to 2.5  $\mu$ s.

### Inhaltsverzeichnis

| 1 | Ein | leitung                          | a man hischetabile Takingeneratoren banen kom (* 10 $^{-\mu}_{\rm L}$ iss | :  |  |  |  |  |  |  |  |  |

|---|-----|----------------------------------|---------------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|

|   | 1.1 | Prinzi                           | pien der elektronischen Zeitmessungen                                     | :  |  |  |  |  |  |  |  |  |

|   |     | 1.1.1                            | Zeitmessung mit Zählern                                                   | :  |  |  |  |  |  |  |  |  |

|   |     | 1.1.2                            | Standard analog-digitale Verfahren (TDC)                                  | 2  |  |  |  |  |  |  |  |  |

|   |     | 1.1.3                            | Der Flash-TDC                                                             | (  |  |  |  |  |  |  |  |  |

| 2 | Ana | Analog-Digital-Umsetzer 1        |                                                                           |    |  |  |  |  |  |  |  |  |

|   | 2.1 | Fehler                           | von ADCs                                                                  | 1  |  |  |  |  |  |  |  |  |

|   |     | 2.1.1                            | Das F1001-System                                                          | 1: |  |  |  |  |  |  |  |  |

| 3 | Gri | mdsch                            | altungen für Rampengeneratoren                                            | 17 |  |  |  |  |  |  |  |  |

|   | 3.1 | Anforderungen an die Generatoren |                                                                           |    |  |  |  |  |  |  |  |  |

|   | 3.2 | Unter                            | suchte Generatoren                                                        | 18 |  |  |  |  |  |  |  |  |

|   |     | 3.2.1                            | Der Miller-Integrator                                                     | 18 |  |  |  |  |  |  |  |  |

|   |     | 3.2.2                            | Generatoren mit Konstantstromquellen                                      | 20 |  |  |  |  |  |  |  |  |

|   |     | 3.2.3                            | Generator mit dem MC10192                                                 | 2  |  |  |  |  |  |  |  |  |

|   |     | 3.2.4                            | Der diskrete Aufbau                                                       | 30 |  |  |  |  |  |  |  |  |

| 4 | Rea | lisiert                          | e Schaltung mit 16 Generatoren                                            | 30 |  |  |  |  |  |  |  |  |

|   | 4.1 | Die G                            | eneratorschaltung                                                         | 3  |  |  |  |  |  |  |  |  |

|   | 4.2 | Die S <sub>1</sub>               | Dannungsstabilisierungen                                                  | 3  |  |  |  |  |  |  |  |  |

|   |     | 4.2.1                            | Die Stabilisierung für $U_1$                                              | 38 |  |  |  |  |  |  |  |  |

|   |     | 4.2.2                            | Die Stabilisierung für $U_2$                                              | 35 |  |  |  |  |  |  |  |  |

|   |     | 4.2.3                            | Die Stabilisierung für $U_3$                                              | 40 |  |  |  |  |  |  |  |  |

|   |     | 4.2.4                            | Der Mechanische Aufbau der $16 \times$ Schaltung                          | 4: |  |  |  |  |  |  |  |  |

| 5 | Die | Trigg                            | erschaltung                                                               | 44 |  |  |  |  |  |  |  |  |

| 6 | Kal | ibratio                          | on und Testmessungen                                                      | 48 |  |  |  |  |  |  |  |  |

|   | 6.1 | Meßai                            | ılban                                                                     | 48 |  |  |  |  |  |  |  |  |

| 6.5 | Bestimmung der Zeitau |      |  |  |  |  |  |  |  |  |   |

|-----|-----------------------|------|--|--|--|--|--|--|--|--|---|

| 6.6 | Ergebnisse            | <br> |  |  |  |  |  |  |  |  | 5 |

# Kapitel 1

# Einleitung

Für viele Bereiche der Technik und Naturwissenschaften sind präzise elektronische Zeitmessungen von großer Bedeutung. Um den Zeitraum zwischen Signalen zu bestimmen sind zwei prinzipielle Ansätze gebräuchlich. Im folgenden werden diese beiden Verfahren kurz erläutert und bewertet. Anschließend wird ein neues Verfahren vorgestellt, das die Vorteile der beiden Ansätze vereinigt und ihre Nachteile weitgehend vermeidet.

# 1.1 Prinzipien der elektronischen Zeitmessungen

#### 1.1.1 Zeitmessung mit Zählern

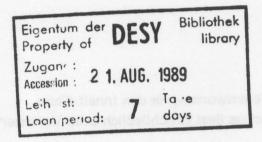

Bei diesem Verfahren (Abb.1.1) leitet das Startsignal die Zählung von Taktimpulsen eines möglichst stabilen Taktgenerators ein. Das Stopsignal beendet diesen Vorgang. Vom Zählerstand kann über die Taktfrequenz auf die Zeit zwischen den Signalen geschlossen werden.

Mit dieser Methode kann die Zeit bis auf etwa eine Taktperiode genau bestimmt werden. Da man hochstabile Taktgeneratoren bauen kann ( $\sim 10^{-10}$ ), ist für die Genauigkeit dieses Verfahrens die erreichbare Taktfrequenz des Zählers von entscheidender Bedeutung. Für eine Auflösung von 50ps wäre eine Frequenz von 20GHz notwendig. Zählerschaltungen für diesen Frequenzbereich sind jedoch nur mit unverhältnismäßig hohem Aufwand aufzubauen. Des weiteren ist es bei Verwendung dieser Methode kompliziert, Zeitmessungen an mehreren, dicht aufeinanderfolgenden Signalen durchzuführen.

Abstract

3

Abbildung 1.1: Zeitmessung mit Zählern

Abbildung 1.2: Funktionsweise eines TDC unter Verwendung eines Abtast-Haltegliedes

#### 1.1.2 Standard analog-digitale Verfahren (TDC)

<sup>1</sup> Bei diesem Verfahren startet das erste Signal einen Generator der ein rampenförmiges Signal erzeugt. Das Stopsignal hält den Generator an.

Zur Konversion des analogen Signals in eine Zahl sind die folgenden zwei Vorgehensweisen gebräuchlich.

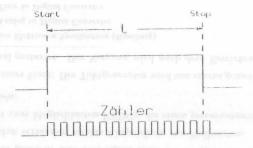

Abbildung 1.3: Funktionsweise eines TDC unter Verwendung einer abfallenden Rampe

- 1. In einem Abtast-Halteglied wird die Signalhöhe festgehalten (Abb.1.2). Danach startet ein zweiter Signalgenerator und ein Zähler. Dieser Generator hat eine weit geringere Steigung. Während diese Rampe nun hochläuft, vergleicht ein Komparator den momentanen Wert der Rampe mit dem Wert im Halteglied. Bei Gleichheit der Werte wird der Zähler angehalten. Aus dem Zählerstand, der Frequenz des Zählers und dem Verhältnis der Steigungen der beiden Rampen läßt sich die gemessene Zeit ermitteln.

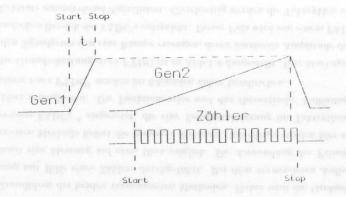

- 2. Bei der zweiten Methode (Abb.1.3) wird nach dem Stopsignal ein abfallendes Signal mit kleiner Steigung erzeugt <sup>2</sup>. Wie im vorhergehenden Fall wird ebenfalls ein Zähler gestartet. Der Zähler wird nun angehalten, wenn die abfallende Rampe den Anfangswert der ersten Rampe erreicht hat.

Diese Verfahren haben den Vorteil, daß Zähler mit weit geringerer Frequenz eingesetzt werden können, als dies bei Verwendung der ersten Methode notwendig ist.

Nachteilig bei diesen Verfahren ist die lange Totzeit zwischen zwei Messungen. Diese ist durch das Konversionsverfahren bedingt, da für das Erreichen einer guten Auflösung bei vorgegebener Zählerfrequenz eine langsam abfallende

Time to Digital Converter

<sup>&</sup>lt;sup>2</sup>In der Regel wird im ersten Schritt ein Kondensator mit hohem Strom geladen und im zweiten Schritt mit einer kleinen Stromstärke entladen

Rampe notwendig ist (z.B.: LeCroy 2228A, 190 $\mu s$  Konversionszent bei einer Auflösung von 11bit).

Ein weiterer Nachteil ist, daß eine Messung nicht schnell abgebrochen und eine erneute Messung gestartet werden kann. (z.B: LeCroy 2228A benötigt  $1,4\mu s$  nach Start des CLEAR-Signals um auf  $\pm 1$  Count abzuklingen)

Ebenfalls ist die Verarbeitung von mehr als einem Signal pro Kanal während der Umsetzung nicht möglich.

Zum Erreichen einer guten Auflösung ist eine große Signaländerung pro Zeiteinheit notwendig. Daraus ergibt sich jedoch eine Limitierung der Meßzeit durch die maximale Amplitude des Rampengenerators.

#### 1.1.3 Der Flash-TDC

Dieser neue Typ von TDC, der am DESY <sup>3</sup> entwickelt wurde [1], kombiniert die Grundideen der beiden vorgenannten Methoden. Dabei wird die Grobzeitmessung mit Hilfe eines Zählers durchgeführt. Bei dem verwendeten Aufbau ist damit eine Messung auf etwa 10ns möglich. Die Anwendung des Prinzips der zweiten Methode liefert die genauere Messung. Allerdings werden hier zur Konversion FADCs <sup>4</sup> eingesetzt, die eine Zeitdigitalisierung im Taktrythmus von 10ns ermöglichen. Die Funktionsweise und das theoretische Auflösungsvermögen eines FTDC<sup>5</sup> werden im folgenden näher beschrieben.

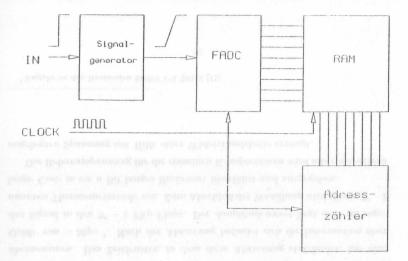

Die Grundschaltung eines FTDC ist in Abb.1.4 dargestellt. Das Startsignal läßt den Signalgenerator eine Rampe erzeugen, deren maximale Amplitude dem dynamischen Bereich des FADC's entspricht. Dieser Puls wird von einem FADC der Taktrate entsprechend digitalisiert. Gleichzeitig werden die Taktzyklen von einem Zähler gezählt. Dieser Zähler liefert die grobe Zeitmessung in Einheiten der Taktzyklen. Die genaue Zeitbestimmung erfolgt aus der Digitalisierung der Pulshöhe der Rampe. Die digitalen Zeitinformationen werden sodann in ein Register geladen. Das Startsignal kann zur Freigabe des Speichers genutzt werden. Man verhindert so das Abspeichern von Nullwerten.

Es gibt zwei Möglichkeiten FTDCs, die einen gemeinsamen Takt benutzen, zu betreiben:

Gemeinsamer Start: Der Taktgenerator wird von einem gemeinsamen START-Signal gestartet. Der Vorgang wird nach dem Erreichen des maximalen

Abbildung 1.4: Blockschaltbild des Flash-TDC

Zählerstandes abgebrochen. Die Register der FTDC-Kanäle enthalten dann die Zeitinformationen der Eingangs-Signale.

Gemeinsamer Stop: Der Taktgenerator läuft frei. Der Zeitpunkt der Eingangs-Signale wird digitalisiert, und ständig im Register gespeichert. Der Zeitpunkt des Stop-Signals wird ebenfalls digitalisiert bevor der Takt angehalten wird. Die Zeiten der Kanäle können dann untereinander und mit der Zeit des Stop-Kanals verglichen werden.

Geht man von einer idealen Elektronik aus (lineare Rampe, FADC mit einem Fehler von 1/2LSB), so ergibt sich der Fehler <sup>6</sup> nach [1] zu:

$$\sigma(t) = \frac{\Delta T}{2^n \sqrt{12} \frac{\Delta T}{t_{rise}} \sqrt{\frac{t_{rise}}{\Delta T}}} \quad mit \quad (t_{rise} \geq \Delta T).$$

Dabei sei  $\Delta T$  die Zeitdifferenz zwischen zwei Takten des FADC,  $t_{rise}$  die Anstiegszeit der Rampe und n die Breite der Ausgangsworte des FADC. Der zweite Wurzelterm berücksichtigt den Fall mehrmaliger Abtastung der Rampe  $(t_{rise} > \Delta T)$ . Die Bestimmung der Zeit aus diesen Werten ist dann mit Hilfe eines Prozessors möglich, der das Register ausliest.

<sup>&</sup>lt;sup>3</sup>Deutsches Elektronen Synchrotron (Hamburg)

<sup>&</sup>lt;sup>4</sup>Flash Analog to Digital Converter

<sup>&</sup>lt;sup>5</sup> Flash Time to Digital Converter

<sup>&</sup>lt;sup>5</sup>Als Fehler wird hier das zweite Moment der Verteilung (Varianz) angegeben

Abbildung 1.5: Blockschaltbild des modifizierten Flash-TDC, wie er verwendet wird

Die beste Auflösung wird bei einer möglichst kurzen Austiegszeit erreicht. Die kürzeste sinnvolle Anstiegszeit ist  $t_{rise} = \Delta T$ . Bei Wahl einer kürzeren Anstiegszeit kann nicht mehr gewährleistet werden, daß es während des Anstiegs der Rampe zu einer Digitalisierung kommt. Ein solcher Vorgang würde zu einer Fehlmessung führen.

Für ein 100MHz FADC System mit einer Auflösung von 8bit und einer Anstiegszeit von 20ns ergibt sich eine Auflösung von 20ps. Mit einem ersten Laboraufbau gelangen Messungen mit einer Genauigkeit von 28ps [1].

Zur Realisierung des Flash-TDC im H1-Experiment [2] wird eine modifizierte Schaltung verwandt (Abb.1.5). Der Taktzähler wurde durch den Addresszähler eines RAM ersetzt. In dem RAM werden nun die Abtastungen gespeichert. Die grobe Zeitmessung ist durch die RAM-Addresse der Abtastwerte gegeben. Diese Modifikation wurde gemacht um eine bereits existierende Schaltung mitverwenden zu können. Dieses System digitalisiert und speichert Analogsignale der Driftkammern des H1-Experiments ([2]) mit Hilfe von FADCs. Diese Schaltung wird in Kapitel 2 näher beschrieben.

Ein wesentlicher Punkt bei Zeitmessungen mit FTDCs ist die Möglichkeit der Auslese der digitalisierten Daten in einen direkt angeschlossenen Mikroprozessor. Dieser erlaubt eine sofortige Kontrolle, Kalibration, Korrektur, Analyse und Speicherung der Zeitinformationen. Diese Möglichkeit der weiteren Verarbeitung ermöglicht es, daß Abweichungen der Form der Rampe von einem linearen Anstieg leicht erkannt und rechnerisch korrigiert werden können [10].

Das größte Gewicht hegt daher auf der Stabilität des Signals.

Die hohe Präzision und die flexible, da rechnergestützte, Handhabung lassen ein breites Anwendungsspektrum erwarten, das nicht nur im wissenschaftlichen Bereich liegt. Die Vorteile des Systems werden hier noch einmal zusammengefaßt.

Der FTDC ermöglicht es, eine kontinuierliche Zeitdigitalisierung mit einer hohen Rate durchzuführen. Die Speicherung der digitalisierten Werte dient als Pipeline. Mit einem Kanal können mehrere aufeinander folgende Signale verarbeitet werden, da die Totzeit zwischen zwei aufeinanderfolgenden Eingangssignalen nur wenige Taktzyklen des FADC-Systems beträgt.

Es können auch große Zeitdifferenzen ohne Verlust an Genauigkeit gemessen werden, vorausgesetzt, es steht ein hinreichend stabiler Takt zur Verfügung und das Register ist tief genug.

Im Handel verfügbare Pipeline TDCs erreichen deutlich schlechtere Auflösungen (z.B. LeCroy Modell 1879 mit 2ns).

Konventionelle TDCs mit hoher Auflösung können nur innerhalb einer kurzen Zeitspanne sensitiv sein (z.B. LeCroy Modell 2228A mit 50ps Auflösung innerhalb von 100ns bei einer Konversionszeit von 100 $\mu sec$ ) und sind nicht in der Lage, mit einem Kanal mehrere, aufeinanderfolgende, Signale zu digitalisieren.

#### Inhalt und Gliederung der Arbeit:

In der vorliegenden Arbeit soll für den FTDC, wie er in Abb. 1.5 gezeigt ist, ein Rampengenerator entwickelt und nach einer Modifikation der FADC-Schaltung des H1-Experiments an diese angepasst werden.

- 1. Einleitung

- 2. Beschreibung der FADC Schaltung

- 3. Spezifikation des Rampengenerators

- 4. Die untersuchten Grundschaltungen für Rampengeneratoren.

- 5. Die realisierte 16× Schaltung.

- 6. Messungen mit der realisierten Schaltung und Ergebnisse.

- 7. Zusammenfassung und Ausblick.

# Kapitel 2

# Analog-Digital-Umsetzer

Da der zu entwickelnde Rampengenerator mit dem bereits bestehenden FADC-System arbeiten soll, wird ein Überblick über die Funktionsweise von FADCs gegeben. Eine Beschreibung des benutzten F1001-Systems folgt.

Die Aufgabe eines Analog-Digital-Umsetzers ist es, ein kontinuierliches Eingangssignal (Spannung) in ein diskretes, dazu proportionales Signal (Zahl) umzusetzen. Dazu sind zwei Operationen notwendig: Eine Quantisierung der Amplitude und eine Diskretisierung der Zeit (Abtasten). Die dazu entwickelten Verfahren lassen sich nach drei Grundprinzipien einteilen: dem Parallelverfahren, dem Wägeverfahren und dem Zählverfahren.

Die im vorliegenden System eingesetzten Wandler arbeiten nach dem Parallelverfahren, das im Folgenden näher beschrieben wird.

Ein FADC mit einer Auflösung von n Bit besteht aus  $2^n-1$  Komparatoren (Abb.2.1), die das Eingangssignal mit dem anliegenden Referenzsignal vergleichen. Der Zustand der Komparatoren wird dann zu einem bestimmten Zeitpunkt in ein, von der Clock getaktetes, flankengesteuertes Flip-Flop übernommen. Das Zeitfenster, in dem diese Abtastung stattfindet, hat eine Größe von  $\sim 50ps^{-1}$ . Nach der Abtastung befindet sich die Information über das Signal in den  $2^n-1$  Flip-Flops. Der Amplitudenwert liegt dort im sogenannten Thermometercode vor. Zum Abschluß der Wandlung wird dieser  $2^n-1$  lange Code in ein n Bit langes Binärwort überführt und ausgegeben.

Die Referenzspannung für die einzelnen Komperatoren wird aus einer extern angelegten Spannung mit Hilfe einer Widerstandskette erzeugt.

$^1\mathrm{Angabe}$ zu den Bausteinen SONY CX 20116 [15]

Abbildung 2.1: Prinzipieller Aufbau eines FADC Bausteins [12]

#### 2.1 Fehler von ADCs

Man unterscheidet statische und dynamische Fehler, die bei der Analog-Digital-Umsetzung auftreten.

#### Statische Fehler

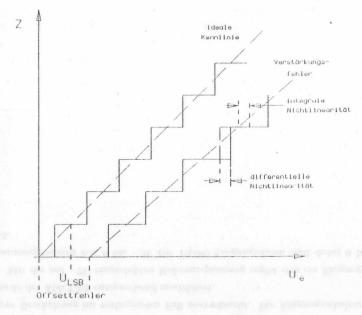

- Da ein AD-Umsetzer mit n Bit nur eine Auflösung von 2<sup>n</sup> Stufen hat, entsteht beim Abtasten, wie in Abb. 2.2 dargestellt, ein systematischer Fehler von ±1/2U<sub>LSB</sub>, der als Quantisierungsfehler bezeichnet wird.

- Verbindet man die Stufenmitten eines idealen AD-Umsetzers miteinander, so erhält man eine Gerade die durch den Ursprung geht und die Steigung eins hat. Bei einem realen AD-Umsetzer geht diese Gerade nicht durch Null, man spricht hier von einem Offsetfehler. Ist die Steigung nicht gleich eins, bezeichnet man dies als einen Verstärkungsfehler. Offsetfehler und Verstärkungsfehler lassen sich meist durch Abgleichmaßnahmen beheben.

- Sind die einzelnen Stufen nicht gleich breit, kommt es zu einem Linearitätsfehler. Bei einem AD-Umsetzer nach dem Parallelverfahren kann

dies durch unterschiedliche Größe der einzelnen Widerstände in der Referenzteilerkette entstehen. Die Abweichung der einzelnen Stufen vom Sollwert  $U_{LSB}$  wird als der differentielle Nichtlinearitätsfehler bezeichnet. Der totale oder integrale Nichtlinearitätsfehler gibt die maximale Abweichung der Stufenmitten von der idealen Geraden an. Die Linearitätsfehler der AD-Umsetzer werden in  $U_{LSB}$ , oder einfacher in LSB, angegeben.

Abbildung 2.2: Idealer und realer Verlauf der Übertragungskennlinie eines AD-Umsetzers

Dynamische Fehler

• Wenn die Abtastfrequenz zu niedrig ist, im Verhältnis zur höchsten Frequenzkomponente des Signals, wird die Signalanalyse fehlerhaft, weil die hohen Frequenzkomponenten nicht aufgelöst werden und sich daraus falsche Komponenten bei niedrigeren Frequenzen ergeben (Aliasfrequenzen). Fehler dieser Art sind auszuschließen, wenn das Abtasttheorem erfüllt ist:

Um ein Signal exakt aus den abgetasteten Werten wiedergewinnen zu können, muß man das Signal mit einer Rate abtasten, die größer als das doppelte seiner höchsten Frequenzkomponente ist. [14]

Also  $f_a > 2f_{max}$

Eine genaue Ableitung ist bei ([13]) nachzulesen. Für AD-Umsetzer mit 100MHz Taktfrequenz ergibt sich  $f_{max}$  demnach zu 50MHz. Da es bei dem Einsatz als Teil eines TDC nicht darauf ankommt, ein Signal vollständig zu erfassen, ist dieser Fehler in diesem Fall nicht von Bedeutung.

Weitere Fehler können durch die Unsicherheit des Abtastzeitpunktes auftreten (Aperturjitter). Diese Zeitunsicherheit darf den Wert nicht überschreiten, der durch die folgende Gleichung angegeben wird [12].

$$\Delta t_a < rac{U_{LSB}}{rac{1}{2}U_{max}\omega_{max}}$$

Wird dieser Wert überschritten, so wird der vom Aperturjitter herrührende Fehler größer als  $U_{LSB}$ . Für einen 8Bit,100MHz-AD-Umsetzer beträgt dieser Wert 25ps.

Für die eingesetzten FADC-Bausteine vom Typ Sony CX20116 wird ein Aperturjitter von 15ps angegeben [17].

#### 2.1.1 Das F1001-System

Bei dem F1001 System [3] handelt es sich um ein 16 Kanal FADC System das um FADC-Bausteine vom Typ SONY CX20116 aufgebaut ist. Die Bausteine ermöglichen eine Wandlungsrate von 100MHz und verfügen über eine Auflösung von 8-bit.

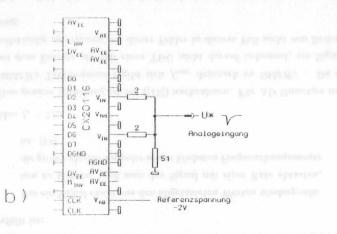

Zu jedem Kanal ist ein Speicher mit einer Tiefe von 256 Worten auf der Karte untergebracht, der über einen VME-Bus ausgelesen wird. Zusätzlich zu den beiden VME-Bus Steckern befindet sich an der Rückseite der Karte ein ebenfalls 96-poliger Stecker, über den die analogen Eingangssignale der FADC-Karte zugeführt werden. In der endgültigen Form sollen hier die Signalgeneratoren in Form einer Aufsteckplatine angeschlossen werden. Die Pinbelegung des Analogeingangs ist in Abb.2.4 dargestellt.

Zur Ermöglichung eines größeren dynamischen Bereichs wurde die Schaltung mit einer Eingangsbeschaltung versehen, die eine nichtlineare Kennlinie erzeugt [3] [11] siehe Abb.2.3.a. Dadurch werden die relativen Fehler bei der Digitalisierung kleiner Spannungen geringer. Bei größeren Spannungen nimmt jedoch der absolute Fehler der Abtastung zu. Beim Einsatz des FADC-Systems in einem FTDC ist jedoch nur der absolute Fehler der Messung entscheidend. Daher ist diese Beschaltung im vorliegenden Fall unerwünscht. Die Eingangsschaltung wurde der Abb.2.3.b entsprechend modifiziert.

Mit der auf -2V eingestellten Referenzspannung ergibt sich ein Eingangspannungsbereich von 0 bis -2V. Die FADC-Ausgangsdaten sind dabei 0 bis 255.

ines dansu musesamenten. Die Abweichung der einschen Sanken von Kennstellerkeite wistatelten. Die Abweichung der einschen Sanken von Koltwert P<sub>L</sub>zar wird als der differentielte Nichtline artigischeher bezeichnet. Der totale über integrale Nichtlinearitätsfähler gibt die maximale Abweichung der Stufenmitten von der idealen Geräden au. Die Limenritätsfehler her AD-Drimetzer werden in P<sub>L</sub>zze, oder einfacher in LSB, augegeben.

Abbildung 2.3: Eingangsbeschaltung des FADCs.

Dynambleche Pebler

| PIN | ROW        | ROW   | ROW    |

|-----|------------|-------|--------|

|     | itember C. | В     | A      |

| 1   | VGND       | VGND  | VGND   |

| 2   | X2         | VGND  | X0     |

| 3   | X2*        | VGND  | X0*    |

| 4   | VGND       | VGND  | VGND   |

| 5   | X6         | VGND  | X4     |

| 6   | X6*        | VGND  | X4*    |

| 7   | VGND       | VGND  | VGND   |

| 8   | Y2         | VGND  | Y0     |

| 9   | Y2*        | VGND  | Y0*    |

| 10  | VGND       | VGND  | VGND   |

| 11  | Y6         | VGND  | Y4     |

| 12  | Y6*        | VGND  | Y-4*   |

| 13  | VGND       | VGND  | VGND   |

| 14  | TPE.X      | +5V   | TPO.X  |

| 15  | TPE.X*     | +5V   | TPO.X* |

| 16  | VGND       | VGND  | VGND   |

| 17  | TPE.Y      | -5,2V | TPO.Y  |

| 18  | TPE.Y*     | -5,2V | TPO.Y* |

| 19  | VGND       | VGND  | VGND   |

| 20  | Х3         | VGND  | X1     |

| 21  | X3*        | VGND  | X1*    |

| 22  | VGND       | VGND  | VGND   |

| 23  | X7         | VGND  | X5     |

| 24  | X7*        | VGND  | X5*    |

| 25  | VGND       | VGND  | VGND   |

| 26  | Y3         | VGND  | Y1     |

| 27  | Y3*        | VGND  | Y1*    |

| 28  | VGND       | VGND  | VGND   |

| 29  | Y7         | VGND  | Y5     |

| 30  | Y7*        | VGND  | Y5*    |

| 31  | VGND       | VGND  | VGND   |

|     |            |       |        |

#### Abbildung 2.4: Pinbelegung des Analogeingangs

# Grundschaltungen für Rampengeneratoren

#### 3.1 Anforderungen an die Generatoren

Aus dem vorgeschenen Einsatzbereich ergeben sich für den zu konstruierenden Generator die folgenden Anforderungen:

- 1. Triggerbar mit einem möglichst kleinem Zeitjitter.

- Die Amplitudenhöhe muß zum FADC-System passend einstellbar sein (-1.8 bis -2.3V).

- 3. Die höchste Genauigkeit kann bei einer Abfallzeit von 10ns erreicht werden. Um eine Digitalisierung gewährleisten zu können, die im steilen, gut definierten, Teil der Rampe liegt, wurde eine Abfallzeit von etwa 11ns im linearen Bereich des Signals gewählt.

- Für die Vermessung kurz hintereinander auftretender Signale sollte die Anstiegszeit kleiner 30ns sein.

- Eine hohe Wiederholgenauigkeit der Signalform mit Schwankungen kleiner 1/2 LSB.

- Kleine Abweichungen von der Linearität des Signals können toleriert werden, da diese bei der Auswertung rechnerisch kompensiert werden.

- 7. Ein geringer Offset ( $\simeq 10 \to 40 mV$ ) <sup>1</sup> sollte am Ausgang einstellbar sein. Dies ermöglicht eine leichtere Überwachung der Schaltung.

<sup>&</sup>lt;sup>1</sup>Entspricht 1 bis 5 FADC Counts

- Für den Aufbau steht nur ein geringer Raum zur Verfügung, da die geplante Karte mit 16 Kanälen als Erweiterungskarte auf den Analogeingung des FADC-System gesteckt werden soll.

- 9. Aus der gleichen Bedingung ergibt sich die Forderung, daß nur die im System vorhandenen Versorgungsspannungen (+5V,-5.2V,±12V) verwendet werden sollen. Am Analogeingang der FADC Karte sind nur die Spannungen -5.2V und +5V verfügbar. Es wäre daher wünschenswert nur diese Spannungen zu verwenden.

10.Der Eingang ist für NIM-Pegel<sup>2</sup> vorzusehen

#### 3.2 Untersuchte Generatoren

In diesem Abschnitt werden Generatoren vorgestellt, die die erforderlichen Kriterien erfüllen könnten.

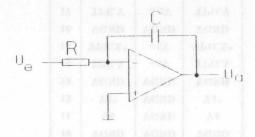

#### 3.2.1 Der Miller-Integrator

Abbildung 3.1: Funktionsschaltbild eines Miller-Integrators

Der einfachste Aufbau besteht aus einem Miller-Integrator [12] wie er in Abb. 3.1 dargestellt ist. Aus einer Sprungfunktion als Eingangssignal ergibt sich der folgende Spannungsverlauf für  $U_a$ , wobei man von idealisierten Bauelementen ausgeht.

$$U_a = \frac{U_{\epsilon} t}{RC}$$

Abbildung 3.2: Miller-Integrator mit Erweiterung, die das Ausgangssignal auf einen mit dem Spannungsteiler einstellbaren Wert begrenzt

Um die Bedingung einer einstellbaren Anstiegszeit und Amplitude zu erfüllen, muß das Triggersignal zu einem Signal bestimmter Amplitude und Länge aufbereitet werden.

Bei der in Abb.3.2 gezeigten Erweiterung der Schaltung reduziert sich die Aufbereitung des Eingangssignals. Es ist nur noch bei einem Signal mit einer Mindestlänge die Einstellung der Amplitude notwendig, denn bei einer bestimmten Ausgangsspannung wird der Transistor leitend und die Integration bricht ab. Die Signalhöhe bei der dies geschieht, wird über den Spannungsteiler  $R_4R_5$  eingestellt. Da über den Spannungsteiler ein Teil des Stromes fließt, verändert sich das Ausgangssignal. Der Signalanstieg verläuft nicht linear, sondern hat die Form einer e-Funktion.

Aus der Forderung nach einer Anstiegszeit der Rampe von 10-15ns folgt, daß der Operationsverstärker über eine Anstiegszeit von  $\leq 5ns$  verfügen muß. Für die verfügbaren Versorgungsspannungen und dem gesetzten Kostenrahmen von etwa 50DM pro Kanal, kamen nur die Bausteine CLC400 und CLC401 [8] in Betracht.

Mit diesen Bausteinen wurde eine Versuchsschaltung aufgebaut. Es zeigte sich jedoch, daß diese, intern als Transimpedanz-Verstärker aufgebauten Operationsverstärker bei kapazitiver Rückkopplung zum Schwingen neigen. Es gelang experimentell nicht, nut diesem Aufbau einen stabilen Zustand zu erreichen.

$<sup>^2</sup>$ NIM-Nuclear Instruments Module H=0V , L=-0 , 8V an  $50\Omega$  , negative Logik

Abbildung 3.3: Prinzipschaltung eines Rampengenerators unter Verwendung einer schaltbaren Stromquelle

#### 3.2.2 Generatoren mit Konstantstromquellen

Ein weiterer möglicher Ansatz ist in Abb. 3.3 gezeigt. Es handelt sich dabei um eine Konstantstromquelle, die einen Kondensator auflädt. Nach dem Abschalten der Quelle ermöglicht der Widerstand eine Entladung des Kondensators. Bei diesem Aufbau erhält man ein Ausgangssignal der folgenden Form [18]:

$$U_a = R I \left(1 - e^{-\frac{t}{RC}}\right)$$

Dieser Ansatz wurde auf zwei verschiedene Arten realisiert.

- 1. Die Schaltung wurde um einen integrierten Baustein (MC10192) aufgebaut.

Dieser enthielt die Konstantstromquelle (Abb.3.4).

- Es wurden diskrete Bauelementen eingesetzt. Diese Schaltungsvariante ist in Abb.3.12 dargestellt.

$$U_{e} = \frac{\frac{1}{16}}{\frac{1}{10}} \frac{\frac{1}{10}}{\frac{7}{10}} \frac{\frac{1}{10}}{\frac{7}} \frac{\frac{1}{10}}{\frac{7}}{\frac{7}} \frac{\frac{1}{10}}{\frac{7}}} \frac{\frac{1}{10}}{\frac{7}} \frac{\frac{1}{10}}{\frac{7}} \frac{\frac{1}{10}}{\frac{7}}} \frac{\frac{1}{10}}{\frac{1}}} \frac{\frac{1}{10}}{\frac{7}} \frac{\frac{1}{10}}{\frac{1}}} \frac{\frac{1}{10}}{\frac{1}}} \frac{\frac{1}{10}}{\frac{1}} \frac{\frac{1}{10}}{\frac{1}}} \frac{\frac{1}{10}}{\frac{1}}} \frac{\frac{1}{10}}{\frac{1}}} \frac{\frac{1}{10}}{\frac{1}} \frac{\frac{1}{10}}{\frac{1}}} \frac{\frac{1}{10}}{\frac{1}}$$

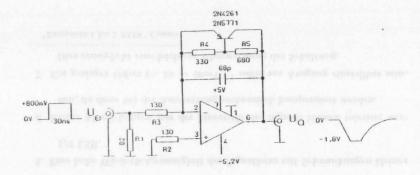

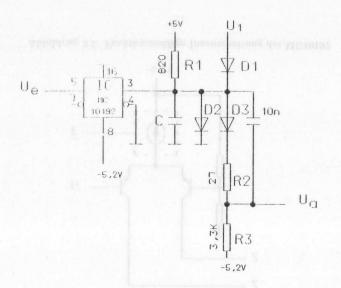

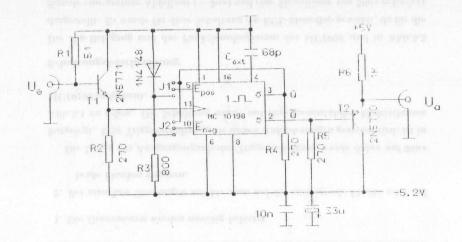

Abbildung 3.4: Schaltung eines Rampengenerators unter Einsatz des Bausteins MC10192 als Stromquelle

Abbildung 3.5: Pinbelegung und Funktionsdiagramm des MC10192

#### 3.2.3 Generator mit dem MC10192

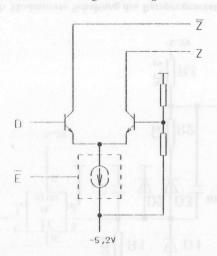

Für die erste Schaltung fand ein IC vom Typ MC10192 [6] Verwendung. Pin-Belegung und Funktionsdiagramm sind in Abb.3.5 dargestellt. Dieser Baustein wird normalerweise als 4×Leitungstreiber eingesetzt.

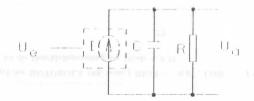

Abbildung 3.6: Funktionsmäßige Innenschaltung des MC10192

Das Verhalten eines Kanals dieses Bauelements läßt sich mit der in Abb.3.6 gezeigten Schaltung beschreiben.

Jeder Kanal verfügt über einen Dateneingang (D) und zwei komplementäre Treiberausgänge(Z und  $\overline{Z}$ ). Je zwei der Treiber haben einen gemeinsamen Enable Eingang ( $\overline{E}$ ). Abhängig vom Zustand des Dateneinganges fließt der Strom der Konstantstromquelle über einen der Transistoren zu dem entsprechenden Ausgang (Z bzw  $\overline{Z}$ ). Die beiden Transistoren arbeiten also als Stromschalter. Unbenutzte Ausgänge sind daher auf  $V_{CC}$  (Masse) zu legen. Die Eingänge sind für ECL-Pegel  $^3$  ausgelegt. Liegt der Dateneingang auf LOW, so ergibt sich am Z Ausgang eine Spannung von -800mV an einer Last von  $50\Omega$ . Der Strom am Ausgang des IC's beträgt also  $\sim -16mA$ . Größere Wiederstände sind bis  $150\Omega$  zulässig. Bei einem HIGH-Pegel am  $\overline{E}$  Eingang werden die dazugehörigen Ausgänge inaktiv. Unbeschaltet befindet sich der  $\overline{E}$  Eingang auf LOW-Pegel und wird somit im Aufbau nicht benutzt. Die Schaltzeiten der D-Eingänge betragen laut Datenblatt [6] 1.5-4.5ns, die der  $\overline{E}$  -Eingänge 2.0-6.0ns.

In der Generatorschaltung (Abb.3.4) wird dieses IC als schaltbare Konstantstromquelle eingesetzt. Die Abfallzeit des Ausgangssignals wird mit dem Kondensator eingestellt. Abweichend vom Funktionsbild Abb.3.3 wird in diesem Aufbau zusätzlich die schnelle Schottky Diode vom Typ Hewlett Packard HPA2900 eingesetzt. Ihre Anode liegt auf einem Gleichspannungspotential von -1.5–-2.0V. Überschreitet die Ausgangsspannung den Wert  $U_1 - U_F^{-4}$ , so wird die Diode leitend und übernimmt den Strom der Stromquelle. So kann die Ausgangsspannung begrenzt und wie gefordert, über  $U_1$  eingestellt werden.

Da im abgeschalteten Zustand der Reststrom der verwendeten Stromquelle bis zu -2mA betragen kann [6], tritt dadurch ein Problem auf. Der Kondensator wird nach der Abschaltung der Stromquelle nicht vollständig entladen. Er behält eine Spannung von  $U_a = RI_{Rest}$  bei. Dieser Reststrom ist von Treiber zu Treiber unterschiedlich und daher schlecht definiert.

Aus der Dimensionierung von R und C ergibt sich ein weiteres Problem.Um eine möglichst lineare Rampe zu erhalten, muß R möglichst groß sein. Ein großer Wiederstand führt jedoch zu einer zu langen Anstiegszeit.

Die in Abb.3.7 gezeigten Modifikationen lösen dieses Problem, wie die Schaltungsbeschreibung zeigt.

Abbildung 3.7: Modifizierte Schaltung des Rampengenerators mit MC10192

Das Netzwerk, bestehend aus der Diode  $D_2$  und dem Widerstand  $R_1$ , stellt sicher, daß sich im abgeschalteten Zustand am Kondensator C eine definierte Spannung von  $\sim 0.4V$  einstellt.

$R_1$  entspricht dem Widerstand paralell zum Kondensator in Abb.3.4. Er liegt nun jedoch nicht mehr auf Masse, sondern auf +5V. Über den Widerstand  $R_1$  fließt ein Strom durch  $D_2$  und in den Ausgang des IC's. Der Strom, der durch die Diode fließt, hängt wie folgt vom Reststrom  $I_{Rest}$  des  $IC_1$  ab.

$$I_{D_2} = I_{R_1} - I_{Rest} - I_{D_3}$$

Um den Einfluß der unterschiedlichen Restströme zu verringern, wird  $I_{R_1} >> I_{Rest}$  gewählt, so daß durch die Diode ein Strom von etwa 4mA fließt. Die Diode wird dann im steilen Bereich ihrer Kennline betrieben und die Flußspannung der Diode wird dadurch weitgehend unabhängig von  $I_{Rest}$ <sup>5</sup>. Eine Schwankung der Flußspannung tritt noch durch die Temperaturdrift auf  $(\Delta U/\Delta T \sim -2\frac{mV}{grad})$ . Die Flußspannung wird außerdem durch Schwankungen der positiven Versorgungsspannung beeinflußt, da dies eine Änderung des Stroms bewirkt, der durch

$<sup>^3</sup> Pegel der MOTOROLA 10K Serie ( HIGH <math display="inline">\sim -0.8 V, \, {\rm LOW} \sim -1.6 V)$

$<sup>^4</sup>U_F$  ist die Durchlaßspannung der Diode  $\sim 0.3 V$

$<sup>^5</sup>$ Bei einem Strom von 3-6mA stellt sich bei der Diode vom Typ HPA 2900 eine Flußspannung von  $U\sim 0.4V\pm 15mV$  ein.

$R_1D_2$  fließt. Diese Schwankung wird mit einer Spannungsstabilisierung minimiert. Returnt programme bernag zu 3203, genert gewegenen w

Im abgeschalteten Zustand wird eine Ausgangsspannung von 01 gefordert. Der positive Offset, der von der Flußspannung herrührt, muß daher kompensiert werden. Dies geschieht mit Hilfe der Diode  $D_3$ . Da diese Diode im System annähernd die gleiche Temperatur wie  $D_3$  hat, verringert sie die Temperaturdrift der Ausgangsspannung. Eine vollständige Kompensation kann nicht erreicht werden, denn der Temperaturkoeffizient der Dioden ist stromabhängig  $^6$ . Durch  $D_3$  fließt ein kleinerer Strom als durch  $D_2$  (  $\sim 1,6mA$ ), dementsprechend ist die Flußspannung an  $D_3$  etwas kleiner als an  $D_2$ . Dieser Unterschied wird mit  $R_2$  ausgeglichen. Da der zur Korrektur des Offsets notwendige Spannungsabfall  $D_3R_2$  von der negativen Spannungsversorgung abhängt, ist auch hier eine Stabilisierung notwendig. Die Abhängigkeit des Ausgangsstroms des IC von der negativen Versorgungsspannung macht es ebenfalls notwendig, diese Spannung zu stabilisieren. Paralell zu  $D_3$  und  $R_2$  liegt ein 10nF Kondensator, um den dynamische Innenwiderstand  $^7$  der Diode zu überbrücken.

Im eingeschalteten Zustand fließt in das IC ein Strom von 16mA. Der Kondensator C wird nun entladen und die Spannung am Kondensator sinkt solange, bis  $D_1$  leitend wird und den Strom übernimmt. Da die Spannung an der Diode schnell unter die Durchlaßspannung fällt, ist der Entladestrom des Kondensators

$$I_C = I - I_{R_0} + I_{D_0}$$

Zu Beginn der Rampe ( $U_C = 0, 4V$ ) beträgt der Strom 11mA, am Ende ( $U_C = -1, 6V$ ) ist  $I_C = 9mA$ . Wird ein Kondensator mit einem konstanten Strom geladen, ergibt sich folgende Gleichung.

$$U_C = \frac{I_C t}{C}$$

Nimmt man näherungsweise für  $I_C$  den mittleren Strom von 10mA, ergibt sich bei einer Abfallzeit von 13ns und einer Spannung von 2V für C ein Wert von 65pF. Dieser näherungsweise berechnete Wert entspricht in etwa dem experimentell ermittelten Wert von 56pF der nachstehend beschriebenen Versuchsschaltung.

Wird die Stromquelle abgeschaltet, wird der Kondensator über  $R_1$  aus der +5V Spannung geladen. Ohne Berücksichtigung des Stromes  $I_D$ , ergibt sich die Spannung am Kondensator zu: [12]

$$U(t) = U_r (1 - e^{-\frac{t}{RC}})$$

Für  $U_r=6,6V$  und U(t)=2V ergibt sich für die Anstiegszeit ein Wert von t=0,36RC. Mit  $R=820\Omega$  und C=56pF ist t=16,5ns. Dies ist jedoch eine Näherung, denn  $I_{D_3}$  verringert den Ladestrom des Kondensators und verlängert dadurch die Anstiegszeit. In der Versuchsschaltung wurde eine Anstiegszeit von 22ns gemessen.

#### Versuchsaufbau

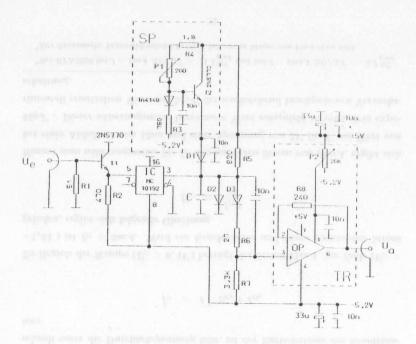

Mit der Schaltung aus Abb.3.7 und einigen zusätzlichen Bauelementen wurde die in Abb.3.8 dargestellte Versuchsschaltung aufgebaut. Die Funktion der Schaltungserweiterungen werden im nachfolgenden beschrieben.

Die Baugruppe SP erzeugt eine Spannung mit der, wie im letzten Abschnitt beschrieben, die maximale Amplitude der Rampe eingestellt wird. Der Transistor  $T_2$  mit seiner Beschaltung stellt einen einfachen Spannungsregler dar. Die Emitterspannung von  $T_2$  ist mit  $P_1$  von -1 bis -1,5V einstellbar. Die Diode an der Basis von  $T_2$  kompensiert die Temperaturdrift von  $U_{BE}$ .

Da die Schaltung Signale mit NIM-Pegel verarbeiten soll, das IC jedoch für ECL-Pegel ausgelegt ist, muß eine Pegelanpassung durchgeführt werden.

Dies geschieht mit dem Transistor  $T_1$ , der den Pegel des NIM-Signals auf ECL-Niveau um  $\sim 0.7V$  absenkt.  $T_1$  wird dazu als Emitterfolger betrieben.

Den Abschluß der Schaltung bildet die Treiberstufe TR. Sie ist mit einem Transimpedanz-Opereationsverstärker (OP) aufgebaut, der das Treiben der geforderten Ausgangslast von  $50\Omega$  erlaubt. Zum Einsatz kommt der Typ CLC400 von COMLINEAR mit einer Abfallzeit von 4.5ns für den Abfall von 0 bis -2V.

Der Operationsverstärker wird als Treiber mit einer Verstärkung von 1 betrieben.  $R_8$  muß in den Rückkopplungszweig eingefügt werden, da der invertierende Eingang des Transimpedanz-Verstärkers einen Eingangswiderstand von nur  $12\Omega$  hat. Der Wert von  $R_8$  entspricht dem vom Hersteller empfohlenen Wert für den Rückkoppelwiderstand.  $P_2$  ermöglicht eine Korrektur des Offsets um  $\pm 20mV$ .

<sup>&</sup>lt;sup>6</sup>Bei HPA 2900 bei I=1mA  $\Delta U/\Delta T=-1.3 \frac{mV}{grad}$  und bei I=10mA  $\Delta U/\Delta T=-0.7 \frac{mV}{grad}$

<sup>&</sup>lt;sup>7</sup>Der dynamische Innenwiderstand beträgt bei einem Strom von 1mA etwa 60Ω.

Abbildung 3.8: Realisierter Versuchsaufbau eines Rampengenerators unter Einsatz des Bausteins MC10192 als Stromquelle

In Abb.3.8 wurden, der Übersichtlichkeit wegen, die eingesetzten Block-Kondensatoren <sup>8</sup> nicht eingezeichnet. Sie liegen an allen Auschlußpunkten der Bauelemente an die Versorungsspannungen. Es wurden 5 Paare eingesetzt.

#### Testmessungen

Um die Schaltung unabhängig vom FADC-System überprüfen zu können, wurde der in Abb.3.9 abgebildete Aufbau benutzt. Das Eingangssignal für den Rampengenerator wird vom Signalgenerator (HP8082A) erzeugt. Für einen Test der Generatoren ohre die in Abschnitt 5 beschriebene Triggerschaltung wurde ein Signal mit NIM-Pegel erzeugt. Die Abfall und Anstiegszeit des Signals betrug 1.5ns, es hatte eine Länge von 40ns. Die beiden Versorgungsspannungen wurden einem einstellbaren Labornetzgerät (Rohde+Schwarz NGT25) entnommen. Das Oszilloskop wird mit dem Triggerausgang des Signalgenerators getriggert.

Abbildung 3.9: Testaufbau, wie er für die Durchführung der analogen Messungen benutzt wurde.

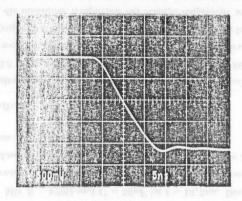

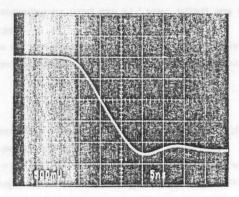

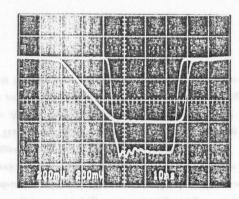

Testmessungen mit dieser Schaltung ergaben so gute Resultate (Abb.3.10 und 3.11), daß beschlossen wurde eine 16×Schaltung aufzubauen, die nach diesem Verfahren arbeitet. Die Abfallzeiten wurden zwischen 10ns und 30ns variert.

Abbildung 3.10: Schirmbild der erzeugten Rampe mit 10ns Abfallzeit. Erzeugt mit dem Generator aus Abb.3.8.

$$D(L) = D_r(1 - \pi^{-2D_r})$$

Spanning an Neudemater and [12]

Ward do Streampolly also choice, ward day Kondemator there My and at 54 Spanning prinches, Oline Berlicksichtigung des Straues In, ergibt sich i

<sup>&</sup>lt;sup>8</sup>10nF Keramik-Kondensatoren paralell zu 33μF Tantal-Kondensatoren

Die Abbildung 3.10 zeigt das Signal mit 10 ns Abfallzeit. Die Abfallzeit wurde gemessen zwischen dem 10 % und dem 90 % Punkt bezogen auf 2V. Der Kondensator C im Versuchsaufbau hatte eine Kapazität von 56pF.

Wie man sieht, handelt es sich bei der Signalform, wie erwartet, um einen exponentiellen Abfall. Der mittlere Teil der Flanke zeigt nur eine sehr geringe Krümmung und erfüllt die in Kapitel 3.1 aufgestellten Anforderungen. Damit das Signal bis 2V ein annähernd lineares, steiles Verhalten zeigt, wurde die maximale Amplitude auf  $\sim 2.2V$  eingestellt. Die Verschleifung und der Überschwinger am Ende der Rampe liegen dadurch außerhalb des Meßbereichs des FADCs und beeinflussen die Zeitmessung nicht.

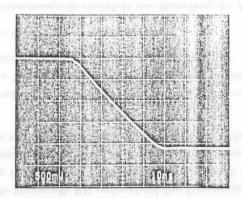

Abbildung 3.11: Schirmbild der erzeugten Rampe mit 30ns Abfallzeit. Erzeugt mit dem Generator aus Abb.3.8.

Abbildung 3.11 zeigt das Signal bei Einsatz eines Kondensators mit einer Kapazität von 180 pF. Die Abfallzeit beträgt nun 30 ns. Der Überschwinger geht zurück und das Signal zeigt relativ kleine Verschleifungen. Am Beginn des Signals fällt ein kleiner Knick auf. Dieser ist wahrscheinlich auf ein Übersprechen innerhalb des Schaltungsaufbaus zurückzuführen. Diese Störung des Signalverlaufes ist für die Zeitmessung nicht von Bedeutung, da sie im Bereich der ersten 10 % der Signalhöhe liegt. Dieser Bereich der Rampe wird in der Regel bei der Bestimmung der Zeit nicht berücksichtigt <sup>9</sup>.

Abbildung 3.12: Diskret aufgebauter Generator mit Konstantstromquelle

<sup>&</sup>lt;sup>9</sup> Es wird zur Vermeidung von Rauschdigitalisierungen ein Schwellwert benutzt

#### 3.2.4 Der diskrete Aufbau

Zur Erreichung einer höheren Linearität der Rampe wurde der im Folgenden dargestellte Aufbau entwickelt. Die in Abb.3.12 gezeigte Schaltung läßt sich in 6 Baugruppen unterteilen.

- 1: Der Eingangsschaltung (INP)

- 2: Dem Stromschalter (IS)

- 3: Der Rampenerzeugung (S)

- 4: Der Konstantstromquelle 1 (IQ1)

- 5: Der Konstantstromquelle 2 (IQ2)

- 6: Der Ausgangstreiber Stufe (TR)

INP: passt das NIM-Eingangssignal an die internen Pegel an.

- IS: Schaltet die Stromquelle IQ1 entsprechend dem Eingangssignal um. Beim Übergang von HIGH nach LOW wird am Ausgang der IS-Stufe ein definierter Pegelsprung von 0 nach 2V erzeugt. Die Eingangsspannung an der S-Einheit wird damit unabhängig von Schwankungen des Eingangssignals (U<sub>r</sub>).

- S: Abhängig von der Basisspannung au T<sub>5</sub> fließt der Strom von Quelle IQ2 durch den Transistor oder lädt den Kondensator und gibt so ein rampenförmiges Signal aus.

TR: Erlaubt es eine, 500-Leitung zu treiben.

IQ1: Die Konstantsromquelle ermöglicht eine Einstellung der Amplitude des Ausgangssignals.

IQ2: Mit dieser Quelle kann die Steigung der Rampe eingestellt werden.

Nach dieser groben Funktionsübersicht erfolgt eine Erläuterung der Schaltung entsprechend ihrem logischen Aufbau. Die Schaltung wurde als Aufsteckplatine für das F1001 FADC-System entwickelt. Da die negative Versorgungsspannung von -5,2V am Analogeingang nur noch einen Wert von -4.9V hat, wurde dieser Wert bei der Dimensionierung zugrunde gelegt.

Der zentrale Teil der Schaltung ist S in Verbindung mit der Konstantstromquelle IQ2 . Die lineare Rampe wird erzeugt, indem der Kondensator  $\mathcal C$  mit der

Konstantstromquelle 1Q2 aufgeladen wird. Es handelt sich also auch hier um einen Generator nach dem Prinzip "Konstantstromquelle mit Kondensator".

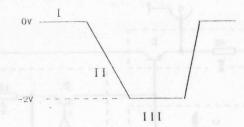

Die Schaltung S kann sich in drei Zustände befinden. Die Abb.3.13 stellt den Signalverlauf während dieser drei Phasen dar.

Abbildung 3.13: Ausgangszustände der Schaltung

- I: Stellt den Grundzustand der Schaltung dar. Der Transistor  $T_5$  ist leitend und überninmt den Strom der Quelle IQ2. Dies ist der Fall, wenn an der Basis eine Spannung von 0V anliegt. Am Kondensator liegt nun eine Spannung von  $-U_{BE}(T_5) \sim -0.75V$  an. Um die in diesem Zustand am Ausgang geforderten 0V zu erreichen, wird  $T_7$  eingesetzt. Er erhöht den Pegel um  $U_{BE}(T_7)$ . Die Temperaturdriften von  $U_{BE}(T_5)$  und von  $U_{BE}(T_7)$  sind entgegengesetzt und heben sich somit auf.

- II: Zu Beginn der Phase II wird die Basis von  $T_5$  auf -2V gelegt. Der Transistor ist nun gesperrt und der Strom der Quelle lädt den Kondensator. Die Spannung am Kondensator beginnt sich abzusenken. Die Geschwindigkeit mit der dies geschieht hängt, vom Strom von IQ2 und dem Kondensator ab .

- III: Erreicht die Spannung am Kondensator einen Wert von  $-2V U_{BE}(T_5)$ , so geht  $T_5$  wieder in den leitenden Zustand über und übernimmt den Strom der Quelle. Das Ausgangssignal bleibt dann auf konstanter Höhe.

Der Übergang zum Grundzustand erfolgt durch Wechsel der Basisspannung von -2V auf 0V. Der Kondensator entlädt sich nun über den Transistor  $T_5$ . Da die Entladung mit dem maximalen  $I_{CE}$  des Transistors erfolgt , ist die Entladezeit sehr kurz und liegt bei ca. 7ns. Damit ist die Bedingung der schnellen Abstellbarkeit der Rampe erfüllt.

Das Schaltsignal  $(0 \rightarrow 2V)$  wird von der Schaltung 15 aus dem Eingangssignal erzeugt. Die beiden Transistoren  $T_3$  und  $T_4$  werden als "Übersteuerter Differenz-Verstärker" betrieben. Die Basis von  $T_4$  wird mit dem Spannungsteiler  $R_6R_7$  auf ein Niveau von -2.45V gehalten. Die Dimensionierung der Widerstände ergibt sich aus der geforderten Spannung von -2.45V an der Basis von  $T_4$  und aus dem Mindeststrom, der durch den Teiler fließen soll. Dieser ergibt sich aus dem Kollektor-Emitter Strom von 15mA und der Stromverstärkung  $\beta$  des Transistors von  $\sim 10$ . Der Basisstrom hat also eine Größe von etwa 1.5mA, der Strom, der durch den Teiler fließt, sollte etwa 10mal größer sein, er wurde daher auf 16mA festgelegt. Der Keramikkondensator (10nF) gewährleistet eine bessere dynamische Stromversorgung der Basis.

Liegt die Basis von  $T_3$  mindestens 200mV höher als die Basis von  $T_4$ , so fließt der gesamte Strom der Quelle IQ1 durch den Zweig  $R_3T_3$ . Fällt die Basisspannung von  $T_3$  um mehr als 200mV unter die von  $T_4$ , so übernimmt der Zweig  $R_4T_4$  den Strom. Bei einem Strom der Quelle IQ1 von 15.5mA liegt an  $R_4$  die geforderte Spannung von 2V an.  $R_3$  wird wie  $R_4$  gewählt, damit in beiden Zweigen die gleichen Verhältnisse herrschen.

Die Schaltung soll von Signalen mit NIM-Pegeln angesteuert werden. Die internen Pegel der Schaltung sind durch den Arbeitspunkt des Stromschalters IS (-2,45V) gegeben. Die NIM-Pegel müssen daher um  $\sim 2V$  abgesenkt werden, was durch  $U_{BE}(T_1)$  und die beiden Dioden  $D_1D_2$  erreicht wird. Dem Widerstand  $R_2$  wurde ein Wert von  $200\Omega$  gegeben. Dieser niedrige Wert wurde gewählt, um die Zeitkonstante bei Abschaltvorgängen  $^{10}$  klein zu halten, diese ergibt sich aus  $C_{BE}(T_3)(\sim 3,5pF)$  und  $R_2$ . Damit ist eine schnelle Änderung von  $U_B(T_3)$  möglich.

Die beiden Stomquellen unterscheiden sich in ihrem Aufbau nur hinsichtlich der Dimensionierung.

Bei einer einfachen Stromquelle (Abb.3.14) hängt der Strom , ohne Berücksichtigung des Basisstromes , wie folgt von der Basis-Emitter-Spannung ab.

$$I = rac{U - U_{BE}}{R}$$

Würde man solch eine Stromquelle für IQ1 einsetzen, so ergäbe sich aus der verwendeten Versorgungsspannung und den Anforderungen der restlichen Schaltung für U ein maximaler Wert von 1.5V. Er liegt in der gleichen Größenordnung wie  $U_{BE}(0.7V)$ .

Abbildung 3.14: Einfache Stromquelle mit Transistor

Die Schwankungen von  $U_{BE}$  auf Grund der thermischen Drift ( $\sim 0.2V/grad$ ) ziehen demnach eine signifikante Änderung von I nach sich. Da die Amplitude des Ausgangssignals direkt proportional zu I ist, kann eine solche Schwankung nicht toleriert werden.

Daher wurde eine Präzisions-Stromquelle unter Verwendung eines Operationsverstärkers aufgebaut. Der Operationsverstärker regelt die Spannung am strombestimmenden Widerstand  $R_5$  unabhängig von  $U_{BE}(T_2)$ . Als Spannungsreferenz dient eine Referenzdiode vom Typ LM385-2.5 mit einem geringen Temperaturkoeffizient von 20ppm/grad. Bei den Operationsverstärkern handelt es sich um den Doppel-Operationsverstärker LM358, bei dem ein Betrieb mit einer asymetrischen Versorgungsspannung von 5V möglich ist.

Der Innenwiderstand der Stromquelle läßt sich nach [12] angeben:

$$R_{Innen} = \beta R_{CE}$$

Da der Innenwicderstand der Stomquelle von der Stromverstärkung abhängt "wurde hier ein Transistor mit hoher Stromverstärkung eingesetzt (BC548B , typ.  $\beta=330$ ).

Die Spannungsteiler  $R_9R_8$  und  $P_1$ , bzw.  $R_{12}R_{13}$  und  $P_2$  ermöglichen die Einstellung des Ausgangsstroms der Quellen. Der Strom der Stromquelle läßt sich nach [12] angeben

$$I = \frac{U_e}{R_E}(1 - \frac{1}{B})$$

$U_e$  ist hierbei die Eingangsspannung des Operationsverstärkers ,  $R_E$  der Emitterwiederstand der Transistors. Wegen B>100 läßt sich die Formel vereinfachen zu:

$$I = \frac{U_{\epsilon}}{R_{E}}$$

<sup>10</sup> Abschaltvorgang: HIGH → LOW

Mit  $P_1$  bzw.  $P_2$  läßt sich  $U_\epsilon$  von 0,625 bis 0,8V einstellen. Für IQ1 ergibt sich daraus ein Strom von 14,5 bis 18,6mA, der Strom von IQ2 beträgt 23,1 bis 29,6mA.

Da es sich um eine Schaltung handelt, die schnelle Schaltvorgänge verarbeitet, wurde für die Transistoren  $T_1, T_3, T_4, T_5$  ein schneller Schalttransistor vom Typ 2N5770 eingesetzt. Er zeichnet sich durch eine hohe Grenzfrequenz ( $f_T = 900MHz$ ) und kleine Basis-Emitter-, Basis-Kollektor-Kapazitäten ( $\sim 3, 5pF$ ) aus. für  $T_7$  wurde der Typ 2N5771 mit ähnlichen Daten eingesetzt.

Das Netzwerk  $R_{11}, P_3$  ermöglicht die Einstellung der Ausgangs-Offsetspannung. Der Offset hat folgende Ursachen:

1: Im ausgeschalteten Zustand, wenn  $T_5$  den Strom von IQ2 übernommen hat, fließt durch  $R_4$  der Basisstrom von  $T_5$ . Es ergibt sich daraus ein Offset von etwa  $\simeq 50 mV$ , der von der Stromverstärkung B des Trausistors  $T_5$  abhängt.

$$U_{Offset} = \frac{R_4 I_{IQ}}{B_{T_b}}$$

Der Offset durch diesen Effekt hat einen relativ großen Wert, da HF-Transistoren in der Regel nur kleine Stromverstärkungen erreichen. Um eine möglichst hohe Stromverstärkung zu erzielen, wurde der Kollektor von  $T_5$  auf +5V gelegt. Dies erhöht B, denn die Stromverstärkung hängt von der Kollektor-Emitterspannung ab.

2: Ein weiterer Beitrag zum Offset entsteht daraus, daß  $U_{BE}$  der Transistoren  $T_5$  und  $T_7$  nicht übereinstimmen. Die Größe dieses Offsets kann bis zu 200mV betragen und hängt zum einen von der Streuung der Transistoren ab, zum anderen fließen durch  $T_5$  und  $T_7$  unterschiedliche Ströme, was zur Folge hat, daß  $U_{BE}(T_5) > U_{BE}(T_7)$  ist.

Über  $R_{15}$  fließt durch  $T_7$  ein Strom von 4mA, denn der Emitter liegt auf einem negativen Potential von -20mV. Dieser Strom erhöht die Schaltgeschwindigkeit des Transistors und vergrößert  $U_{BE}(T_7)$ , was den Offset verringert.

#### Testmessungen

Mit dem gleichen Aufbau wie im vorhergehenden Abschnitt wurden mit dem diskret aufgebauten Signalgenerator Testmessungen durchgeführt. Die Abbildung 3.15 zeigt ein Signal mit 10 ns Abfallzeit. Das Signal hat in der Mitte der Rampe eine bessere Linearität (vergleiche Abb.3.10). Die Verschleifungen am Signal Anfang und am Ende sind jedoch deutlicher.

Da die Unterschiede zwischen den Signalen, die mit den beiden Generatoren erzeugt wurden, nur sehr gering waren, wurde der aufwendigere und großflächigere diskrete Aufbau nicht weiterverfolgt.

Abbildung 3.15: Schirmbild der erzeugten Rampe mit 10ns Abfallzeit. Erzeugt mit dem diskret aufgebaut Generator

# Kapitel 4

# Realisierte Schaltung mit 16 Generatoren

Für den Aufbau der 16×- Schaltung fiel die Wahl auf den Generator mit dem MC10192, da bei diesem der Schaltungsaufwand gering war, und die Testschaltung gute Ergebnisse zeigte. Durch den Operationsverstärker als Ausgangstreiber dieser Schaltung (Abb. 4.1) ergibt sich ein größerer Einstellbereich für die Amplitude des Signals, denn die Verstärkung des Operationsverstärkers ist einstellbar.

Abbildung 4.1: Der Generator wie er für die 16 fach Schaltung verwendet wurde

#### 4.1 Die Generatorschaltung

Ein Vergleich der Schaltung 4.1 mit dem Versuchsaufbau 3.8 zeigt folgende Änderungen:

Der Offset am Operationsverstärker ist nicht mehr einstellbar und der entsprechende Eingang wurde auf Masse gelegt. Auf die Nutzung der Offsetverstellung am Operationsverstärker wurde verzichtet, da eine Einstellung des Offsets auch über eine Veränderung der stabilisierten Versorgungsspannungen möglich ist. Diese Maßnahme reduzierte die Zahl der notwendigen Potentiometer deutlich 1, was einer sicheren Betriebsweise zu Gute kommt.

#### 4.2 Die Spannungsstabilisierungen

Die notwendigen drei stabilisierten Versorgungsspannungen (siehe Abschnitt 3.2.3) werden aus den Rohspannungen mit drei Spannungsstabilisierungen (Abb. 4.2.4.3.4.4) erzeugt.

An die Stabilisierungsschaltungen werden dabei besondere Anforderungen gestellt:

- $\bullet$  geringe Verlustspannung (0,3V) bei  $U_2$

- kleine Ausgangsspannung (-1 bis -1,5V bei  $U_1$ )

- geringe Temperaturabhängigkeit

Integrierte ,einstellbare Spannungsregler für diese Anwendung sind nicht erhältlich. Die Stabilisierungen wurden daher mit diskreten Transistoren und Ansteuerung durch Operationsverstärker aufgebaut.

Die 16 Generatoren nutzen diese Spannungsquellen gemeinsam. Individuell einstellbare Spannungen wären wünschenswert, um die unterschiedlichen Offsetspannungen kompensieren zu können. Sie rühren von den Exemplarstreuungen der Durchflußspannungen der Dioden ( $\sim \pm 50 mV$ ) her. Auf eine solche Einstellmöglichkeit wurde verzichtet, es würde zu einer wesentlich umständlicheren Handhabbarkeit und erhöhter Störanfälligkeit des Aufbaus führen (48 Potentiometer).

<sup>&</sup>lt;sup>1</sup>3 Potentiometer gegenüber 16

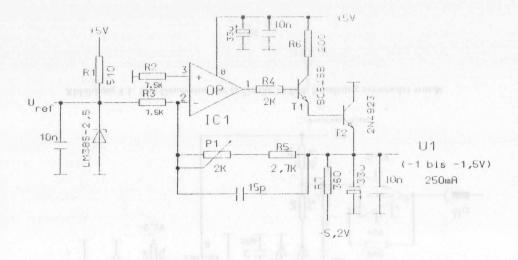

Abbildung 4.2: Die Spannungsstabilisierung für U 1

#### 4.2.1 Die Stabilisierung für $U_1$

Mit der stabilisierten Spannung U<sub>1</sub> (Abb.4.1 4.2) läßt sich, wie in Abschnitt 3.2.3 beschrieben, die Amplitude des Ausgangssignals einstellen.  $U_1$  wird mit der in Abb.4.2 gezeigten Schaltung aus der -5.2V Rohspannung erzeugt. U1 ist im Bereich von  $-1.5 \rightarrow -1V$  einstellbar. Die Stabilisierung ist mit dem Operationsverstärker OP 2 und der Darlington-Schaltung T<sub>1</sub>T<sub>2</sub> aufgebaut. Die Darlington-Schaltung ist erforderlich, um den geforderten Strom von max,~  $250mA (16 \times 16mA)$  liefern zu können. Die Ausgangsspannung wird am Emitter von T, entnommen und über den Spannungsteiler PR, R, an den invertierenden Eingang des Operationsverstärkers geführt. An R<sub>3</sub> wird die Referenzspannung  $U_{ref}(+2.5V)$  gelegt. Der nichtinvertierende Eingang des Operationsverstärker wurde über  $R_2$  auf 0V (Masse) gelegt.  $R_2$  mit der gleichen Größe wie  $R_3$  wurde eingeführt, um die Wirkung des Eingangsoffsetstroms zu kompensieren. Die Referenzspannung wird mit der Referenzspannungsdiode LM385/2.5 und dem Widerstand  $R_1$  erzeugt. Mit  $R_1$  wird der Strom, der durch die Diode fließt, auf 5mA festgelegt. Der Operationsverstärker regelt die Ausgangsspannung nun so, daß an seinem invertierenden Eingang 0V anliegt. Die Ausgangsspannung läßt sich mit dem Potentiometer zwischen -1V und -1.5V einstellen.

$$U_1 = \frac{U_{ref}(P+R_5)}{R_3}$$

Der Ausgang des Operationsverstärker wird über  $R_4$  an die Basis von  $T_1$  gelegt.  $R_4$  begrenzt den Basisstrom des Transistor auf einen Wert von  $\sim 1,5mA$ . Der Kollektor von  $T_1$  wurde über  $R_6$  mit +5V verbunden und begrenzt so den Basisstrom von  $T_2$  auf etwa 25mA. Diese beiden Widerstände dienen der Dämpfung des Regelkreises. Das Potentiometer P und der Widerstand  $R_5$  werden mit dem 15pF Keramikkondensator überbrückt, um hochfrequente Schwingungen zu verhindern. Für den Kondensator wurde experimentell der kleinstmögliche Wert ermittelt, was eine möglichst schnelle Regelung bedeuted. Der Kollektor von  $T_2$  liegt auf Masse. Das minimiert die Verlustleistung des Transistors.

Der Spannungsregler wird nur dann belastet, wenn einer der Generatoren ein Signal erzeugt. Während des größten Teils der Zeit liefert die Spannungsquelle nur den Strom, der in den Rückkoppelkreis fließt. Dieser Strom von 0.33mA ist zu gering um eine stabile Regelung zu gewährleisten. Durch  $R_7$  wird nun erreicht, daß eine Mindestlast von  $\sim 10mA$  vorhanden ist. Die Kondensatorpaare aus  $33\mu F$  Elektrolyt und 10nF Keramik Kondensatoren werden als Blockkondensatoren eingesetzt.

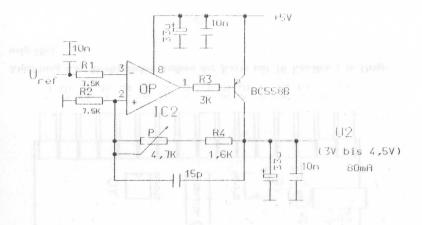

#### 4.2.2 Die Stabilisierung für $U_2$

Wie in Abb.4.1 zu sehen ist, wird mit  $U_2$  die positive Vorspannung eingestellt. Zusammen mit  $U_3$  efolgt so die Einstellung des Offsets. Für  $U_2$  wird eine stabilisierte Spannung im Bereich von  $3V \to 4,5V$  benötigt. Die in Abb. 4.3 gezeigte Spannungsquelle liefert diese Spannung, die aus der Rohspannung von +5V erzeugt wird. Wegen der Sättigungsspannung von  $T_1(\sim 300mV)$  ist eine Einstellung nur bis etwa 4.5V möglich, wobei eine Reserve von etwa 200mV mit einbezogen wurde. Die Ausgangsspannung wird über den Spannungsteiler  $PR_4$   $R_2$  an den nichtinvertierenden Eingang des Operationsverstärker gelegt. Der invertierende Eingang wird über  $R_1$  mit der Referenzspannung  $U_{ref}$  verbunden. Alle drei eingesetzten Spannungsquellen nutzten die selbe Referenzspannungsdiode. Der Operationsverstärker regelt die Ausgangsspannung num so, daß der invertierende Eingang auf +2.5V liegt.

$$U_2 = U_{ref} \frac{R_2 + R_4 + P}{R_2}$$

Der Ausgang des Operationsverstärker liegt über  $R_3$  an der Basis des Transistors. Die Basisspannung des Transistors liegt bei  $\sim 4,3V$ .

<sup>&</sup>lt;sup>2</sup>1/2 MC34002

Abbildung 4.3: Die Spannungsstabilisierung für U 2

Die maximale Ausgangsspannung des Operationsverstärkers liegt in dieser Schaltung bei  $\sim \pm 3,5V$ . Bei einer Kollektor-Emitter-Spannung von 0,5 bis 1,5V und einem Emitterstrom von 80mA, ist ein Basisstrom von etwa 0,5 bis 1mA notwendig. Durch den Spannungsabfall an  $R_3$  von 1,5 bis 3V kann der Operationsverstärker den Transistor zuverlässig steuern. Zudem begrenzt  $R_3$  den Basisstrom des Transistors und trägt so zur Dämpfung des Regelkreises bei. Der 15pF Kondensator hat hier die gleiche Funktion wie im vorher beschriebenen Regler.

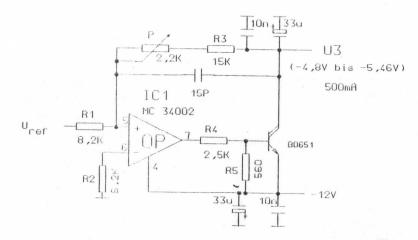

#### 4.2.3 Die Stabilisierung für $U_3$

Die dritte stabilisierte Spannungsquelle stellt die Spannung  $U_3$  bereit, die zur Versorgung des MC10192 (siehe Abb. 4.1) dient und zusammen mit  $U_2$  die Einstellung des Ausgangsoffsets erlaubt.  $U_3$  liegt zwischen -4.8V und -5.46V und wird aus der -12V Rohspannung mit der Schaltung aus Abb. 4.4 erstellt.

Die Spannungsquelle arbeitet mit einem Operationsverstärker (1/2MC34002) und dem Darlington-Transistor BD651. Die Quelle muß einen Strom von etwa 0,5A liefern, was den Einsatzt eines Leistungstransistors erforderlich macht.  $U_3$  liegt am Kollektor des Transistors und wird über den Spannungsteiler  $R_3PR_1$  an den nichtinvertierenden Eingang des Operationsverstärkers gelegt. Über  $R_1$  wird die Referenzspannung angeschlossen. Der invertierende Eingang liegt über  $R_2$  auf 0V (Masse). Der Widerstand wurde eingesetzt, um den Einfluß des Eingangsoffset Stroms zu vermindern. Der Operationsverstärker regelt die

Ausgangsspannung nun so, daß am nichtinvertierenden Eingang eine Spannung von 0Vanliegt.

Abbildung 4.4: Die Spannungsstabilisierung für U 3

Die Basisspannung des Transistors liegt bei ca. -10.5V. Die Ausgangsspannung des Operationsverstärkers  $U_A$  liegt jedoch im Bereich  $-10V \to +3V$ . Am günstigsten ist es , den Operationsverstärker in der Mitte seines Aussteuerbereiches ( $U_A = -3, 5V$ ) zu betreiben Der Spannungsteiler  $R_4R_4$  bewirkt nun, daß die Basis an der Spannung  $U_B$  liegt:

$$U_B = \frac{(U_A + 12)R_5}{R_4 + R_5} - 12$$

Der Basis-Emitter Strom des Transistors wurde bei der Berechnung von  $U_B$ nicht berücksichtigtn, da er klein gegenüber dem Strom im Spannungsteiler ist. Dies liegt an der großen Stromverstärkung ( $\sim 3000 \rightarrow 5000$ ) des Transistors. Der 15pF Kondensator und die Blockkondensatoren erfüllen in dieser Schaltung die gleiche Funktion wie in den vorhergehenden.

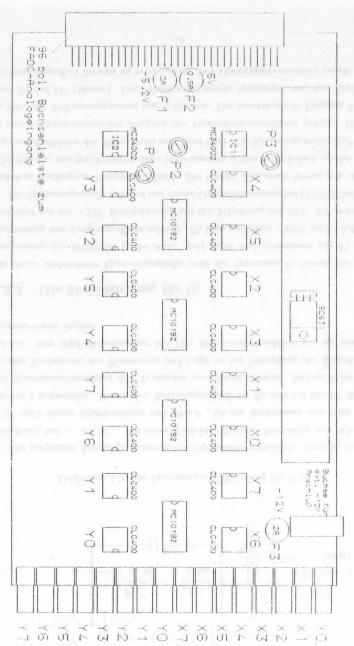

Abbildung 4.5: Mechanischer Aufbau der Karte mit 16 Kanälen ( in Originalgröße)

#### 4.2.4 Der Mechanische Aufbau der 16× Schaltung

Abbildung 4.5 zeigt den Aufbau der Schaltung. Der 16-Kanal Rampengenerator wurde auf einer HF Experimentierplatine der Größe  $21cm \times 12,5cm$  aufgebaut. Die Eingangssignale werden an die Koaxialbuchsen  $X_0$  bis  $Y_7$  angelegt. Die Ausgangssignale werden über eine 96-polige Buchsenleiste an die FADC-Karte weitergegeben. Die Verbindungen zwischen den Eingängen und den Eingangstransistoren wurde mit  $50\Omega$  Koaxialleitungen durchgeführt. Für die Verbingung der Ausgangstreiber mit der Buchsemeiste wurde das gleiche Verfahren gewählt. Die Spannungsversorgung mit -12V wird dem Aufbau über eine Bananenbuchse zugeführt. Mit den Potentiometern  $P_1$   $P_2$   $P_3$  können die stabilisierten Spannungen  $U_1, U_2$  und  $U_3$  eingestellt werden. Für alle Versorgungsspannungen wurden Sicherungen eingebaut  $(F_1 \rightarrow F_3)$ . Der Transistor  $T_3$ , der zur Stabilisierung von  $U_3$  notwendig ist, wurde auf ein Kühlblech aus Aluminium befestigt. Das erlaubt die Abführung der Wärme, die durch die hohe Verlustleistung von  $\sim 3.5W$  entsteht.

Um einen induktivitätsarmen, HF-gerechten Aufbau zu gewährleisten, wurden die zu einem Kanal gehörenden Komponenten mit möglichst kurzen Verbindungen positioniert.

43

# Kapitel 5

# Die Triggerschaltung

Die in den beiden vorhergehenden Abschnitten beschriebenen Generatoren benötigen zur Einhaltung einer hohen Wiederholgenauigkeit des Ausgangssignals möglichst steile Eingangssignale ( $t_{Abfall} \leq 5ns$ ). Ebenso müssen für die Pegel (0V und -8V) eine Toleranz von  $\pm 100mV$  eingehalten werden. Um eine vollständige Rampe zu erzeugen, muß die Länge der Eingangssignale mindestens der gesamten Abfallzeit der Rampe entsprechen. Signale, die vermessen werden sollen, erfüllen nicht immer diese Kriterien. Es ist daher erforderlich, eine Triggerschaltung zu entwerfen.

Beim Entwurf einer Triggerschaltung ging man vom Verhalten der Generatoren aus. Die Generatoren erzeugen nur auf abfallende Flanken hin die definierte Rampe. Das Signal bleibt dann bis zum Rückgang des Eingangssignals auf seinem maximalen Wert. Dies ist aus mehreren Gründen nicht immer erwünscht.

- 1. Die Generatoren werden unnötig belastet.

- Bei manchen Messungen möchte man auf die ansteigende Flanke oder auf beide Flanken triggern.

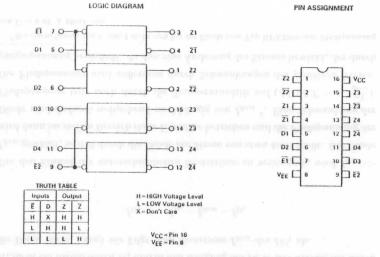

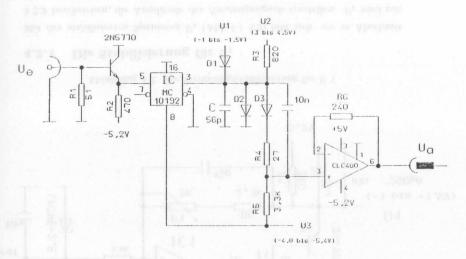

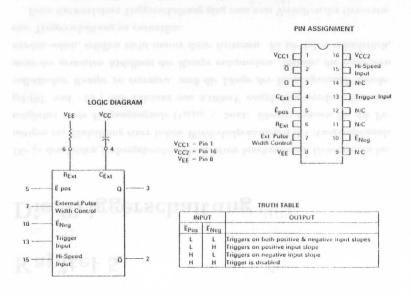

Die Länge des Ausgangssignals der Triggerschaltung wurde daher auf 30ns festgelegt. Eine Triggerschaltung, die diesen Anforderungen gerecht wird, ist in Abb.5.1 zu sehen. Die Schaltung wurde mit dem monostabilen Multivibrator MC10198 aufgebaut.

#### Schaltungsbeschreibung

Die Pin-Belegung und das Funktionsdiagramm des MC1098 sind in Abb.5.2 dargestellt. Es wurde für diese Schaltung ein ECL-Monoflop gewählt, da für die Signale eine geringe Abfallzeit ( $\sim 3ns$ ) und eine Signallänge von 30ns gefordert

wurden. ECL-Pegel lassen sich auch mit geringem Aufwand an NIM-Pegel anpassen.

Die Länge des Ausgangssignals kann mit einem externen Kondensator an Pin 4 und einem externen Widerstand an Pin 8 in einem Bereich von  $10ns \rightarrow \sim 1ms$  eingestellt werden. Da intern bereits ein Widerstand von  $240\Omega$  vorhanden ist, konnte auf einen externen Widerstand an Pin 8 verzichtet werden. Die für eine Signallänge von 30ns geforderte Kapazität ergibt sich gemäß [6] zu 68pF.

Das IC vefügt über zwei Eingänge. Einen flankengesteuerten Eingang mit Schmitt-Trigger und einen sogenannten schnellen Eingang. Hier findet der flankengesteuerte Eingang Verwendung. Durch die Beschaltung der Eingänge  $\overline{E}_{neg}$  und  $\overline{E}_{pos}$  läßt sich die Triggerart wählen (siehe Funktionsdiagramm).

Abfallende Flanke:  $\overline{E}_{pos}$  wird auf HIGH und  $\overline{E}_{neg}$  wird auf LOW gelegt.

Ansteigende Flanke:  $\overline{E}_{pos}$  wird auf LOW und  $\overline{E}_{neg}$  wird auf HIGH gelegt.

Beide Flanken:  $\overline{E}_{pos}$  wird auf LOW und  $\overline{E}_{neg}$  wird auf LOW gelegt.

Die gewünschte Triggerart wird mit den beiden Jumpern J1 und J2 eingestellt.

Liegen beide Eingänge auf HIGH, so ist der Eingang verriegelt. Diese Eigenschaft wird genutzt um ungewollte Verlängerungen des Ausgangssignals durch dicht aufeinander folgende Trigger zu verhindern. Der Ausgang Q wird zu diesem Zweck auf den entsprechenden Eingang gelegt. Diese Rückkopplung sperrt den Triggereingang für die Dauer des Ausgangssignals.

Die Transistoren  $T_1$   $T_2$  dienen zur Pegelverschiebung ( $NIM \rightarrow ECL$  und  $ECL \rightarrow NIM$ ). Mit der Diode wird ein HIGH-Pegel (-0.7V) erzeugt. In Abb.5.3 ist ein Schirmfoto des Ausgangssignals der Triggerstufe gezeigt. Die Abfallzeit beträgt etwa 3ns, das Signal hat eine Länge von  $\sim 30ns$ .

Abbildung 5.1: Triggerschaltung mit dem MC10198

Abbildung 5.2: Pin-Belegung und Funktionsdiagramm des MC10198

Abbildung 5.3: Schirmbild des Ausgangssignals der Triggerschaltung. Abfallzeit  $\sim 3ns$ , Signallänge  $\sim 30ns$  Das Signal mit der großen Abfallzeit und geringen Amplitude ist das Eingangssignal. Ohne die Triggerschaltung ist dieses Signal nicht in der Lage, die Signalgeneratoren zuverlässig anzusteuern.

# Kapitel 6

# Kalibration und Testmessungen

#### 6.1 Meßaufbau

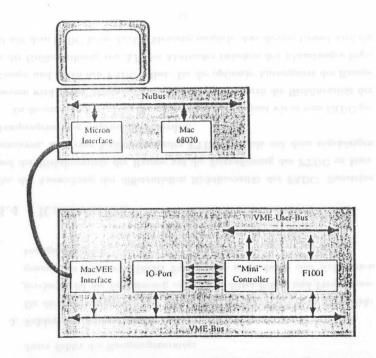

Zum Test des 16-fach Rampengenerators wurde ein VME- System mit einer F1001-FADC Karte benutzt. Die Steuerung der Messung und der Auslese wurde mit einem Macintosh II Computer vorgenommen, der auch zur graphischen Darstellung der Meßergebnisse diente. Der Testaufbau bestand im einzelnen aus folgenden Komponenten:

#### F1001-FADC Karte

VME-Karte mit 16 FADC Kanälen in 8-Bit Auflösung und Zwischenspeicher für 256 Abtastungen.

#### FADC-Controller

Hilfslogik zur Steuerung der FADC-Karte und 100MHz Generator zur Erzeugung des FADC-Abtasttaktes.

#### IO-Port

Schnittstelle des FADC-Controller zum VME-Bus.

#### MacVEE/Micron Interface

zwei Interface-Karten, die einen Zugriff vom Macintosh auf den VME-Bus ermöglichen.

#### Macintosh II Computer

Steuerrechner zur Kontrolle der Messung und zur Auslese der digitalisierten Daten. Mit diesem Rechner wurde auch die Kalibration und graphische Darstellug der Daten vorgenommen.

Abbildung 6.1 zeigt den Meßaufbau schematisch.

Abbildung 6.1: schematischer Aufbau des FTDC-Testsystemes

#### 6.2 Meßprinzip des FTDC

Um den FADC zur Zeitmessung mit hoher Auflösung, also als Flash Time to Digital Converter zu verwenden, wird neben der hohen Abtastrate von 100MSample besonders der geringe Jitter-Fehler dieser Bausteine von  $\sim 15ps$  ausgenutzt.

Das zu messende Eingangsignal wird bei dieser Meßmethode nicht direkt mit dem FADC digitalisiert, sondern startet einen Rampengenerator, der nach einer Anstiegszeit  $t_{rise}$  eine maximale Amplitude  $A_{max}$  in der Größenordnung der Vollaussteuerung des FADC erreicht. Diese Rampe wird durch den FADC abgetastet. Bei einer Anstiegszeit von  $t_{rise} > \Delta T$ , der Zeit, zwischen zwei Abtastzyklen des FADC, erhält man mindestens einen Abtastwert im Anstieg der Rampe. Eine grobe Zeitinformation über den Startzeitpunkt der Rampe ergibt sich durch Abzählen der Abtastungen bis zur ersten Digitalisierung des Rampenanstiegs. Die genaue Phasenlage dieser Digitalisierung zum Startpunkt der Rampe  $t_A$  wird aus der gemessenen Rampenamplitude A bestimmt. Der

Fußpunkt der Rampe und damit der zu messende Zeitpunkt ergibt sich also aus:

$$t = n\Delta T - t_A.$$

Zur Bestimmung von  $t_A$ , der Phase des Meßsignales zum Abtasttakt, kann im einfachsten Fall ein linearer Anstieg der Rampe von Null bis  $A_{max}$  angenommen werden. In diesem Falle ergibt sich die Rampenphase aus der gemessenen Amplitude A zu:

$$t_A = \frac{t_{rise}}{A_{max}} A$$

Die theoretisch erreichbare Zeitauflösung des FTDC wird in [1] mit

$$\sigma_t = \frac{t_{rise}}{2^n \sqrt{12} \sqrt{\frac{\Delta T}{t_{rise}}}}$$

angegeben, wobei n die Bitbreite der Digitalisierung des FADC angibt. In der Ableitung dieser Auflösung wurde nur der Quantisierungsfehler des FADC's berücksichtigt und von einer ansonsten idealen Elektronik ausgegangen. Für das benutzte Testsystem mit einem 100MHz, 8bit FADC und einer Rampenanstiegszeit von  $t_{rise} \sim 11ns$ , ergibt sich hieraus eine Auflösung von  $\sigma_{th} \sim 13ps$ . Ein realer Aufbau kann diese Auflösung jedoch wegen verschieder anderer Fehler des FADC und der Steuerelektronik nicht erreichen.

#### 6.3 Meßfehler

Die mit dem benutzten Testaufbau erzielbare Zeitauflösung wird vor allem durch folgende Fehler begrenzt.

#### 1. FADC-Fehler

Die durch den FADC digitalisierten Daten sind selbst fehlerbehaftet. Erstens wird der analoge Meßwert durch die Abtastung in ein Raster von  $2^n$  möglichen Abtastwerten gepreßt(n Bit-Breite der Digitalisierung). Dieser sogenannte Quantisierungsfehler von 1/2LSB ist durch eine Kalibration nicht kompensierbar.

Weiter treten, wie unter 2 beschrieben, durch Toleranzen bei der Herstellung von Flash ADCs ungleiche Widerstände in der Referenzteilerkette des Bausteins auf, die zu verschieden großen Digitalisierungsstufen führen. Diese differentielle Nichtlinearität führt bei der Bestimmung der Rampenphase zum Abtasttakt zu einem systematischen Fehler, da die Rampe bei linearem Anstieg verschiedene Zeitspannen benötigt, um verschiedene Digitalisierungsstufen der FADC-Kennlinie zu durchqueren. Dieser Effekt führt zu einer Verschlechterung der Zeitauflösung des FTDC. Da dieser Fehler für ein FADC-Exemplar als konstant angenommen werden kann, ist bei genauer Kenntnis der Stufenbreiten ein Ausgleich dieses Fehlers bei der Berechnung von  $t_A$  möglich.

#### 2. Rampenfehler

Zur Bestimmung der Rampenphase wurde die Linearität der Rampe angenommen. Der verwendete Rampengenerator erzeugt jedoch eine Rampe, die insbesondere bei kleinen Amplituden nichtlinear ist und damit zu Fehlern bei der Bestimmung der Rampenphase  $t_A$  führen würde. Auch in diesem Fall ist durch eine Kalibration eine Korrektur der aus einer Amplitude berechneten Rampenphase möglich. Nicht korrigierbar ist der Jitter-Fehler des Rampengenerators.

#### 3. Fehler des Abtasttaktes

Da die Zeitbestimmung mit dem FTDC immer relativ zum Abtasttakt geschieht, ist die Zeitmessung mit dessen Jitter-Fehler und Frequenzungenauigkeit behaftet. Dieser Fehler kann nicht durch eine Kalibration korrigiert werden.

#### 6.4 Kalibration

Um die Auswirkung der differentiellen Nichtlinearität der FADC- Bausteine und der Nichtlinearität der Rampe auf die Zeitauflösung des FTDC zu kompensieren, muß eine Kalibration jedes FTDC- Kanals mit dem zugehörigen Rampengenerator vorgenommen werden.

Zu diesem Zweck wird der Rampenverlauf so bestimmt wie er vom FADC gemessen wird. Diese Messung beinhaltet die Fehler durch die Nichlinearität der Rampe und durch den FADC selbst. Da die optimale Anstiegszeit der Rampe in der Größenordnung von  $\Delta T$ , des Abstandes zwischen den Abtastungen liegt, ist mit dem FADC keine direkte Messung möglich. Aus diesem Grund wird ein

statistisches Verfahren benutzt, um die Rampenform durch viele Einzelmessungen zu bestimmen. Man betrachtet hierfür die relative Häufigkeit  $n_i/N$  mit der in N FADC-Messungen der Rampe, die Amplitude i digitalisiert wurde. Falls die Rampe zufällig, mit zeitlich gleichverteilter Phase zum FADC-Takt gestartet wird, ist dieser Wert ein direktes Maß für die Zeit  $\Delta t_i$ , die die Rampe benötigt, um am FADC eine Änderung des Ausgabewertes von der Digitalisierung i nach i+1 zu bewirken. Es gilt :

$$\lim_{N \to \infty} \frac{n_i}{N} = \frac{\Delta t_i}{\Delta T}$$

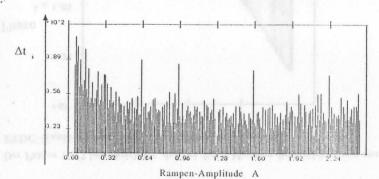

Um die Bedingung der Gleichverteilung zu erfüllen, wird die Rampe bei der Messung von einem "Zufallsgenerator" gestartet, der aus einer radioaktiven Quelle und einem Diskriminator aufgebaut ist. Abbildung 6.2 zeigt eine so aufgenommene Verteilung von Rampenamplituden. Das Histogramm, das mit der 16- fach Rampenschaltung in  $\sim 10000$  Messungen aufgenommen wurde, zeigt deutlich die oben beschriebenen Nichtlinearitäten. Am Beispiel der Amplituden  $31=2^5-1$  und  $32=2^5$  ist in diesem Histogramm die ungleiche Breite der Digitalisierungstufen des realen FADC's zu errkennen. Der große Unterschied in den Historamm-Einträgen dieser beiden Amplituden kann nicht durch die Form der Rampe, sondern nur durch die differenzielle Nichtlinearität des FADC erklärt werden. Der große Verlauf des Histogramms zeigt einen Abfall der Häufigkeiten mit steigender Rampenamplitude, der auf eine niedrigere Steigung der Rampe bei kleinen Amplituden hinweist.

Abbildung 6.2: Häufigkeitsverteilung der gemessenen Rampenamplituden

Aus diesem Histogramm kann die Kalibrationsfunktion durch Summation über die Einzelzeiten gewonnen werden.

$$t_A = \Delta T \sum_{i=A_0}^{A} \Delta t_i$$

Da bei der Messung die Anstiegszeit der Rampe  $t_{rise}$  kleiner als der Abtasttakt gewählt wurde, sind bei einem Teil der Messungen zwei Messpunkte auf der Rampe digitalisiert. Für diese Punkte ist der zeitliche Abstand zwischen beiden Messungen als  $\Delta T$  genau bekannt. Diese Information kann zu einer Skalierung der Einzelzeiten verwendet werden. Für die gemessenen Amplituden  $A_1$  und  $A_2$  gilt:

$$t_{A_1} + \Delta T = \Delta T \left\{ 1 + \sum_{i=A_0}^{A_1} \Delta t_i \right\} = \Delta T \sum_{i=A_0}^{A_2} \Delta t_i = t_{A_2}.$$

Aus diesem Ausdruck erhält man den Skalierungsfaktor:

$$S = \frac{1}{\sum_{i=A_1+1}^{A_2} \frac{n_i}{N}},$$

mit dem die Zeiten  $\Delta t_i$  skaliert werden.

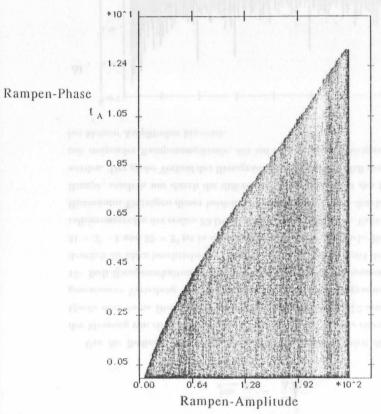

Die auf diese Weise bestimmte Kalibrationsfunktion ist in Abbildung 6.3 zu sehen. Auch in dieser Darstellung sind noch Stufen durch die Nichtlinearität des FADC erkennbar. Wenn mit dieser Methode ein FTDC-Kanal kalibriert wurde, können alle weiteren Kanäle relativ zu diesem Referenz-Kanal kalibriert werden.

#### 6.5 Bestimmung der Zeitauflösung

Um die Zeitauflösung mit der durch die Kalibration gewonnenen Kalibrationsfunktion zu bestimmen, wird folgendes Verfahren benutzt:

Der oben erwähnte Zufallsgenerator erzeugt ein Triggersignal, das auf zwei kalibrierte FTDC-Kanäle gegeben wird. Berechnet man die, Differenzzeit  $t_{2-1}=t_2-t_1$ zwischen beiden Kanälen, sollte diese bis auf den Meßfehler konstant sein. Die Zeitauflösung des FTDC's  $\sigma_t$ ergibt sich unter der Bedingung, daß die Meßfehler normalverteilt sind, aus dem zweiten Moment der Differenzzeitverteilung

21

$$\sigma_t = \frac{\lim_{N \to \infty} \sigma_{t_{2-1}}}{\sqrt{2}}$$

Der Faktor  $1/\sqrt{2}$  berücksichtigt, daß bei dieser Messung die Zeitfehler von zwei FTDC-Kanälen in den Fehler der Differenzzeit eingehen.

Abbildung 6.3: Aus der Kalibration gewonnene Korrekturfunktion

#### 6.6 Ergebnisse

Mit der oben angegebenen Methode wurden von den 16 FADC-Kanälen der F1001-FADC Karte, jeweils zwei Kanäle zusammengefasst und deren Auflösung bestimmt. In Abbildung 6.4 ist die Differenzzeitverteilung für ein solches Kanalpaar dargestellt. Die bei dieser Messung bestimmte Auflösung  $\sigma_t$  lag im Bereich von 22–28ps. Die genauen Werte sind der Tabelle 6.6 zu entnehmen.

| FTDC-Kanal | Zeitauflösung                 |  |  |  |  |

|------------|-------------------------------|--|--|--|--|

| 1-2        | 22.43ps                       |  |  |  |  |

| 3-4        | 28.32ps                       |  |  |  |  |

| 5-6        | 24.38ps                       |  |  |  |  |

| 7-8        | 25.82ps<br>23.16ps<br>24.13ps |  |  |  |  |

| 9-10       |                               |  |  |  |  |

| 11-12      |                               |  |  |  |  |

| 13-14      | 25.91ps                       |  |  |  |  |

| 15-16      | 26.16ps                       |  |  |  |  |

Diese gemessenen Zeitauflösungen lassen auf eine sehr gute Rampenkonstanz schließen, wenn man berücksichtigt, daß die theoretisch erreichbare Zeitauflösung für die benutzte Konfiguration bei  $\sim 13ps$  liegt. Der Unterschied von 10-15ps ist für einen Testaufbau im Labormaßstab ein gutes Ergebnis und bestätigt die bei der oszillagraphischen Untersuchung beobachteten Ergebnisse.

$t_A = \Delta T \sum_{i=1}^{A}$

Abbildung 6.4: Verteilung der Differenzeit zwischen zwei FTDC-Kanälen

# Kapitel 7

# Zusammenfassung und Ausblick

Für die kontinuierliche schnelle Zeitmessung mit dem Flash-TDC wird ein Signalgenerator benötigt, der ein besonders stabiles, möglichst lineares Rampensignal liefert.

Für eine hohe Auflösung soll die Anstiegszeit von der Größenordnung der Zykluszeit des FADC- Taktes, im vorliegenden Fall etwa 10ns,sein.

In dieser Arbeit wurden verschiedene Schaltungen für einen derartigen Signalgenerator aufgebaut und ausgetestet. Darüberhinaus wurde eine 16-Kanal FADC-Karte (F1001) mit einer Zusatzkarte mit 16 Signalgeneratoren ausgerüstet, um so 16 FTDC-Kanäle zu erhalten.