# UNIVERSITE LIBRE DE BRUXELLES FACULTE DES SCIENCES

A VMEbus-Based Data Acquisition System for the Multiwire Proportional Chambers of the H1 Detector at the HERA Collider

> Dissertation présentée en vue de l'obtention du titre de Docteur en Sciences

Philippe HUET

Mai 1993

### UNIVERSITE LIBRE DE BRUXELLES

#### FACULTE DES SCIENCES

## A VMEbus-Based Data Acquisition System for the Multiwire Proportional Chambers of the H1 Detector at the HERA Collider

Dissertation présentée en vue de l'obtention du titre de Docteur en Sciences

Philippe HUET

Mai 1993

## A VMEbus-Based Data Acquisition System for the Multiwire Proportional Chambers of the H1 Detector at the HERA Collider

#### Remerciements

Mes remerciements vont tout d'abord à Monsieur le Professeur Jean Sacton pour m'avoir offert la possibilité de travailler au sein de l'Institut Inter-universitaire des Hautes Energies pendant plus de 5 ans. Je lui suis très reconnaissant de m'avoir proposé un sujet qui m'a permis de m'initier aux techniques instrumentales et aux systèmes d'acquisition des données au sein d'un laboratoire de pointe. Son enthousiasme, ses conseils toujours pertinents, ainsi que la confiance dont il m'a toujours témoignée m'ont été d'un grand apport et m'ont encouragé à mener à terme ce travail.

Je tiens à exprimer ma plus grande reconnaissance au Dr. Robert Roosen dont l'intérêt constant pour mon travail a été une source continue de stimulation. Son soutien empreint d'amitié, ses conseils et suggestions, ainsi que l'aide qu'il m'a continuellement apportée ont été essentiels pour son bon aboutissement. Les nombreuses discussions que nous avons eues au cours de notre découverte de la gastronomie hambourgeoise ont été un divertissement apprécié et indispensable en certaines circonstances. Je tiens également à le remercier pour avoir bien voulu commenter et critiquer le manuscrit de cette thèse, bien que son contenu soit fort éloigné des sujets traditionnellement traités au laboratoire. Pour tout ceci, merci.

Mes remerciements vont aussi au Dr. Johan Morecls qui a développé le logiciel sans lequel aucune acquisition des données ne serait possible. En me faisant profiter de son expérience et de ses comaissances en programmation et en électronique il m'a beaucoup aidé. Sa persévérance a vouloir comprendre et résoudre les problèmes a été en particulier fort utile.

La réalisation d'une expérience de physique des hautes énergies est bien entendu le fruit d'un travail d'équipe. Au sein de l'IIHE, les Docteurs M. Barth, G. Bertrand-Coremans, D.P. Johnson et P. Marage n'ont jamais hésité à me donner une explication ou à m'apporter l'aide que je leur demandais. Je tiens également à remercier Erik Evrard qui connaîtra aussi très prochainement les joies de l'écriture. Pendant plus de trois ans, il a développé des logiciels permettant de tester le détecteur et les systèmes électroniques. Sa disponibilité et son ardeur au travail ont été grandement appréciés.

I would like also to express my gratitude to all my colleagues at DESY. It has been a pleasure working with them. I have benefited greatly from the advice and cooperation of too many engineers, physicists and technicians to list them individually. However I would thank by name Claire Bourdarios, Albrecht Leuschner, Katarina Müller and Stanislaw Mikocki who have actively participated in the installation and the tests of the MWPCs. Their friendship contributed greatly to the pleasant atmosphere within the group.

I also reserve special thanks for John Coughlan, Eckhard Elsen, Bill Haynes and Manfred Zimmer for their helpful advice and assistance during the implementation of the readout system. I am also indebted to Hanns Krehbiel, A. Hrisoho and Gisèle Martin for the many fruitful discussions about the front-end components.

Je n'aurais rien pu réaliser sans la collaboration efficace et toujours prompte de l'équipe d'électroniciens du laboratoire. Leur travail consciencieux, souvent sous-estimé, a été d'une importance cruciale à plusieurs moments. J'aimerais en particulier adresser mes plus vifs remerciements à Christian Wastiels et Rik Turtelboom pour leur très grand savoir faire tant dans leur travail que dans l'art de divertir au bon moment.

Enfin, ce document ne serait pas ce qu'il est sans le travail remarquable de Mesdames Danielle Luypaert et Myriam Pins. La qualité de la mise en page et des illustrations leur est entièrement due. Je tiens à les remercier très sincèrement pour l'aide qu'elles m'ont ainsi apportée et pour la patience dont elles ont fait preuve. Un très grand merci.

Pour terminer, j'aimerais citer quelqu'un qui a tout compris :

"Vous savez que j'ai un esprit scientifique.

Or récemment, j'ai fait une découverte bouleversante!

En observant la matière de plus près...j'ai vu des atomes...qui jouaient entre eux...et qui se tordaient de rire! Ils s'esclaffaient!

Vous vous rendez compte de conséquences incalculables que cela peut avoir?

Je n'ose pas trop en parler, parce que j'entends d'ici les savants: "Monsieur, le rire est le propre de l'homme!"

Eh oui!... Et pourtant! Moi, j'ai vu, de mes yeux vu, des atomes qui: "Ha, ha, ha!" Maintenant de qui riaient-ils?

Peut-être de moi? Mais je n'en suis pas sûr! Il serait intéressant de le savoir. Parce que si l'on savait ce qui amuse les atomes, on leur fournirait matière à rire... Si bien qu'on ne les ferait plus éclater que de rire.

Alors, me direz-vous, que deviendrait la fission nucléaire? Une explosion de joie!"

Raymond Devos

# Contents

| In | itrod | uction  |                                          |   |     | 1               |

|----|-------|---------|------------------------------------------|---|-----|-----------------|

| 1  | H1    | at HE   | RA: The Collider and the Experiment      |   |     | 3               |

|    | 1.1   |         | luction                                  |   |     | 3               |

|    | 1.2   |         | IERA Collider                            |   |     | 4               |

|    |       | 1.2.1   | Introduction                             |   |     | 4               |

|    |       | 1.2.2   | The Injection Systems                    |   |     | 5               |

|    |       | 1.2.3   | The HERA Rings                           |   |     | 7               |

|    |       |         | 1.2.3.1 The Electron Ring                |   |     | 7               |

|    |       |         | 1.2.3.2 The Proton Ring                  |   |     | 7               |

|    | 1.3   | Exper   | imentation at HERA                       |   |     | 7               |

|    | 2.0   | 1.3.1   | Kinematics                               |   |     | 7               |

|    |       | 1.3.2   | Event Signatures                         |   |     | 10              |

|    |       | 1.3.3   | Determination of the Bunch Crossing Time |   |     | 11              |

|    | 1.4   |         | If Detector                              |   |     | 12              |

|    |       | 1.4.1   | Detector Scheme                          |   |     | 12              |

|    |       | 1.4.2   | Tracking Detectors                       |   |     | 15              |

|    |       | 1.4.2   | 1.4.2.1 Introduction                     |   |     | $\frac{15}{15}$ |

|    |       |         | 1.4.2.2 Central Tracker                  |   |     | , 16            |

|    |       | •       | 1.4.2.3 Forward Tracker                  |   |     | 18              |

|    |       |         | 1.4.2.4 Backward MWPC                    |   |     | 21              |

|    |       | 1.4.3   | The Outer Proportional Chambers (COP)    |   |     | 21              |

|    |       | 1.4.0   | The Other Proportional Chambers (COI)    | • | • . | 1 ک             |

| 2  | The   |         | ata Acquisition System                   |   |     | 27              |

|    | 2.1   | Introd  | uction                                   |   |     | 27              |

|    | 2.2   | Basic 1 | Design Features                          |   |     | 28              |

|    |       | 2.2.1   | Bunch Crossing Rate                      |   |     | 28              |

|    |       | 2.2.2   | Event and Background Rates               |   |     | 29              |

|    |       | 2.2.3   | Detector and Front-End Electronics       |   |     | 30              |

|    |       | 2.2.4   | Consequences                             |   |     | 31              |

|    | 2.3   | Overvi  | iew of the H1 Trigger System             |   |     | 32              |

|    |       | 2.3.1   | Introduction                             |   |     | 32              |

|    |       | 2.3.2   | Level 1                                  |   |     | 33              |

|    |       | 2.3.3   | Level 2                                  |   |     | 38              |

|   |     | 2.3.4  | Level 3                                                       |

|---|-----|--------|---------------------------------------------------------------|

|   |     | 2.3.5  | Level 4                                                       |

|   | 2.4 | Logic  | al Structure of the Data Acquisition Chain                    |

|   |     | 2.4.1  | Front-end Signal Storage                                      |

|   |     | 2.4.2  | Front-end Freeing                                             |

|   |     | 2.4.3  | Front-end Event Building                                      |

|   |     | 2.4.4  | Central Event Building and Mass Storage 42                    |

|   | 2.5 | Hardy  | vare Implementation                                           |

|   |     | 2.5.1  | Introduction                                                  |

|   |     | 2.5.2  | The VMEbus                                                    |

|   |     |        | 2.5.2.1 General VMEbus Features                               |

|   |     |        | 2.5.2.2 The VSBbus                                            |

|   |     |        | 2.5.2.3 Multi-Crate Systems                                   |

|   |     | 2.5.3  | Examples of Front-end Electronics                             |

|   |     |        | 2.5.3.1 Drift Chamber Readout                                 |

|   |     |        | 2.5.3.2 LAr Calorimeter Readout                               |

|   |     | 2.5.4  | Central Data Acquisition                                      |

|   |     | _,,,,  | 2.5.4.1 Full Event Building                                   |

|   |     |        |                                                               |

|   |     | 2.5.5  |                                                               |

|   |     | 2.0.0  | Overall Experiment Control                                    |

| 3 | Det | ection | and Signal Processing in the MWPC System 57                   |

| - | 3.1 | Introd | uction                                                        |

|   | 3.2 | Funda  | mentals of Particle Detection in Multiwire Proportional Cham- |

|   | ٠.٠ | bers   |                                                               |

|   | 3.3 |        | Detection in the Central and Forward Chambers 61              |

|   |     | 3.3.1  | Readout Cell                                                  |

|   |     | 3.3.2  |                                                               |

|   | 3.4 |        | 10: 15:                                                       |

|   | 3.5 | Ampli  |                                                               |

|   | 5.0 | 3.5.1  |                                                               |

|   |     | 3.5.2  | The Preamplifier 65                                           |

|   |     | 3.5.3  | The Preamplifier                                              |

|   |     | 3.5.4  | 77 · C · · · · · · · · · · · · · · · · ·                      |

|   | 3.6 |        | • • •                                                         |

|   | 0.0 | 3.6.1  | C( 137)                                                       |

|   |     | 3.6.2  | Threshold and Discriminator Circuitm                          |

|   |     | 3.6.3  | Threshold and Discriminator Circuitry                         |

|   |     | 3.6.4  | The Sync. Gate Array                                          |

|   |     | 3.6.5  | Pattern Simulation                                            |

|   |     | 5.0.0  | The Monitoring Circuits                                       |

|   |     |        | 8 6                                                           |

|   |     |        | 0                                                             |

|   |     |        | 3.6.5.3 Voltage Measurements                                  |

iii

| 4 | Im  | plemer | ntation of the MWPC Readout System             | 85   |

|---|-----|--------|------------------------------------------------|------|

|   | 4.1 |        | luction                                        | 85   |

|   | 4.2 |        | m Overview                                     | 85   |

|   |     | 4.2.1  | The Front-end Electronics                      | 86   |

|   |     | 4.2.2  | The Master Crate                               | 87   |

|   |     | 4.2.3  | The Subsystem Trigger Controller               | 89   |

|   |     | 4.2.4  | The Monitoring System                          | 90   |

|   | 4.3 | Data   | Flow                                           | 91   |

|   |     | 4.3.1  | Front-end Freeing                              | 91   |

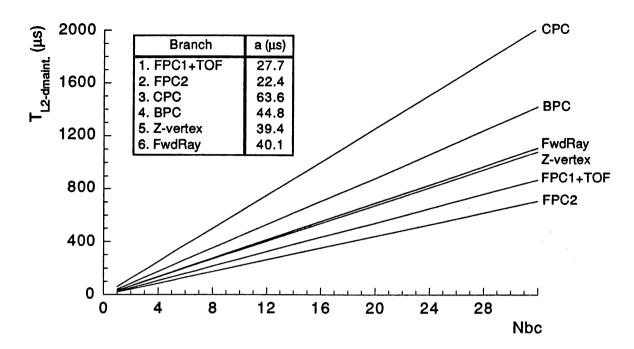

|   |     | 4.3.2  | Front-end Event Building                       | 93   |

|   | 4.4 | The E  | Branch Driver Card                             | 94   |

|   |     | 4.4.1  | Introduction                                   | 94   |

|   |     | 4.4.2  | Block Diagram Description                      | 94   |

|   |     | 4.4.3  | The Bus Interfaces                             | 96   |

|   |     |        | 4.4.3.1 The VME Slave Interface                | 96   |

|   |     |        | 4.4.3.2 The Vertical Bus Master Interface      | 96   |

|   |     |        | 4.4.3.3 The STC interface                      | 96   |

|   |     | 4.4.4  | The Static RAM Memory                          | 97   |

|   |     | 4.4.5  | The FIFO Buffer                                | 97   |

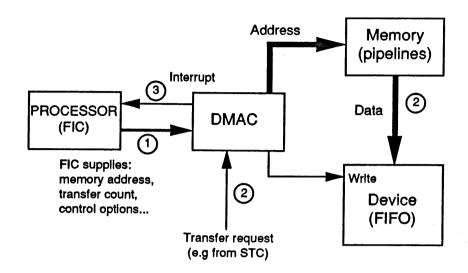

|   |     | 4.4.6  | The DMA Controller                             | 98   |

|   | 4.5 | The C  | Controller Card                                | 100  |

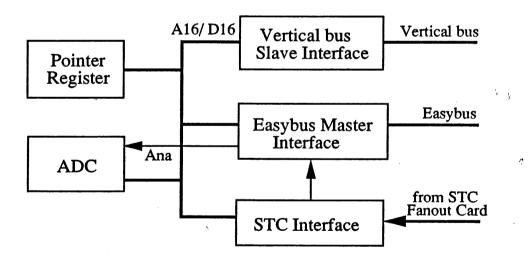

|   |     | 4.5.1  | General Description                            | 100  |

|   |     | 4.5.2  | Data Transfer and Easybus                      | 101  |

|   |     |        | 4.5.2.1 Mechanics                              | 101  |

|   |     |        | 4.5.2.2 Signal Lines                           | 102  |

|   |     |        | 4.5.2.3 Electrical Specifications              | 103  |

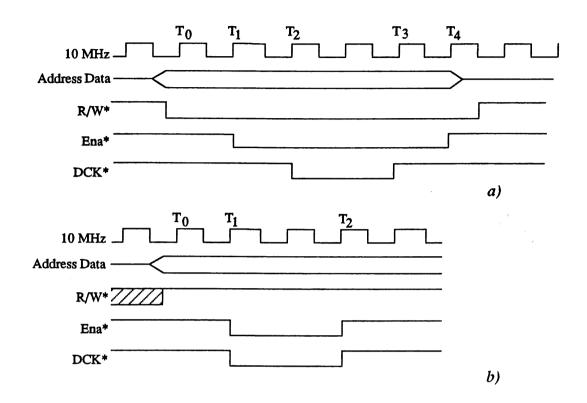

|   |     |        | 4.5.2.4 Timing                                 | 103  |

|   |     |        | 4.5.2.4.1 Write cycle                          | 103  |

|   |     |        | · · · · · · · · · · · · · · · · · · ·          | 105  |

|   |     | 4.5.3  |                                                | 106  |

|   |     | 4.5.4  |                                                | 106  |

|   | 4.6 |        | ubsystem Trigger Controller                    | 107  |

|   |     | 4.6.1  |                                                | 107  |

|   |     | 4.6.2  |                                                | 107  |

|   |     | 4.6.3  |                                                | 109  |

|   |     | 4.6.4  |                                                | 110  |

|   |     | 4.6.5  |                                                | 110  |

|   | 4.7 |        |                                                | 111  |

|   |     | 4.7.1  |                                                | 111  |

|   |     | 4.7.2  | ·                                              | 113  |

|   |     | 4.7.3  |                                                | 113  |

|   | 4.8 | -      |                                                | 114  |

|   |     | 4.8.1  |                                                | 114  |

|   |     | 482    | Front-end Synchronization and Pineline Control | 11.1 |

| 4.8        | 3.3 Readout  | t Synchronization                     | . 117 |

|------------|--------------|---------------------------------------|-------|

|            | 4.8.3.1      | MWPC DAQ Software                     |       |

|            | 4.8.3.2      | Interrupt Structure                   |       |

|            | 4.8.3.3      | Readout Cycle                         |       |

|            | 4.8.3.4      | Monitoring Interface                  |       |

| 4.9 Sy     | stem Perforn | nance                                 |       |

| 4.9        |              | $\operatorname{ction}$                |       |

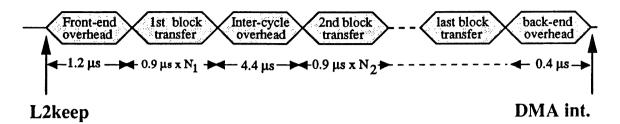

| 4.9        |              | nd Freeing Time                       |       |

|            | 4.9.2.1      | DMA transfer Time                     | 124   |

|            | 4.9.2.2      | L3keep Cycle Acknowledgment           | 126   |

|            | 4.9.2.3      | L3reject Cycle Acknowledgment         | 127   |

| 4.9        |              | uilding Time                          |       |

| 4.9        |              | offering and Dead Time Considerations |       |

| 4.9        | .5 Summar    | у                                     | 134   |

| Conclusion | ns           |                                       | 137   |

| Bibliograp | hy           |                                       | 139   |

# List of Figures

| 1.1  | Layout of HERA and its preaccelerators                              |

|------|---------------------------------------------------------------------|

| 1.2  | Feynman diagrams for neutral and charged current e-p interactions 8 |

| 1.3  | Topology of deep inelastic e-p scattering events                    |

| 1.4  | Experimentally accessible regions at HERA                           |

| 1.5  | The H1 detector                                                     |

| 1.6  | The H1 tracking system                                              |

| 1.7  | Central tracker                                                     |

| 1.8  | Schematic blowup of a radial wire drift chamber                     |

| 1.9  | Planar drift chambers of the FTD                                    |

| 1.10 | View of the cathodes of the forward MWPC                            |

| 1.11 | Arrangement of pads in the forward MWPC                             |

| 1.12 | Cross section of the COP end structure                              |

| 1.13 | COP HV plateau curve                                                |

|      | Time resolution measured with the COP detector                      |

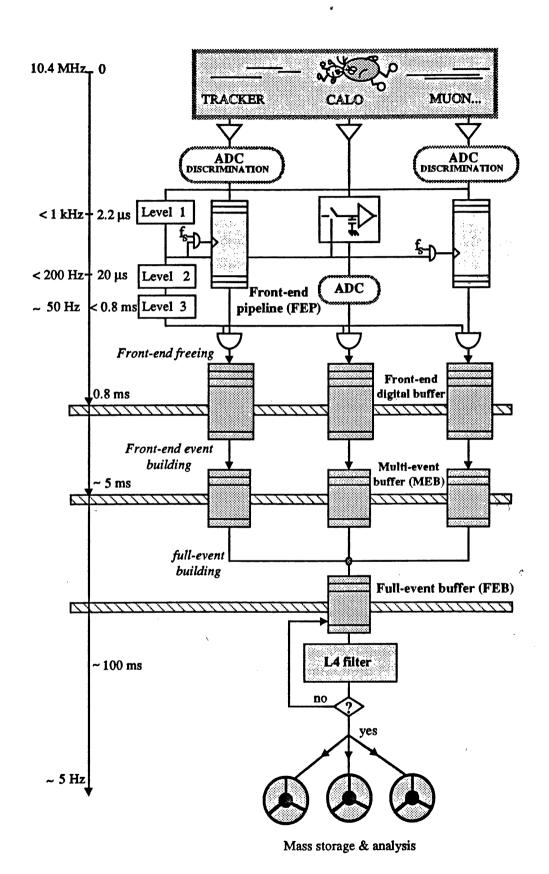

| 2.1  | Triggering and filtering levels                                     |

| 2.2  | Pipelined trigger for the decision level 1                          |

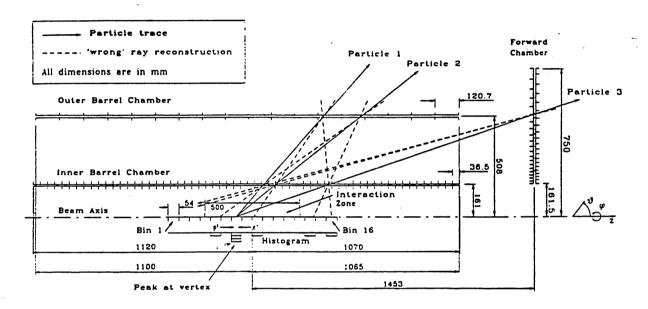

| 2.3  | Z-vertex reconstruction using the MWPC pad signals                  |

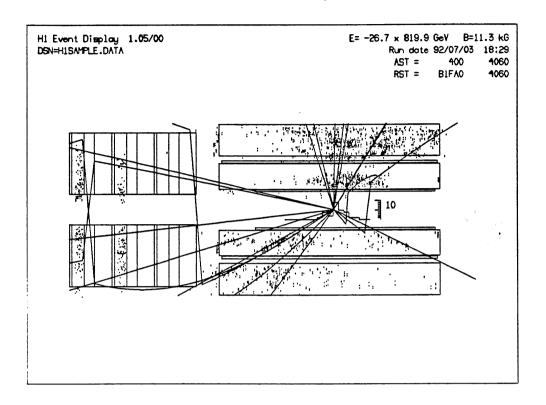

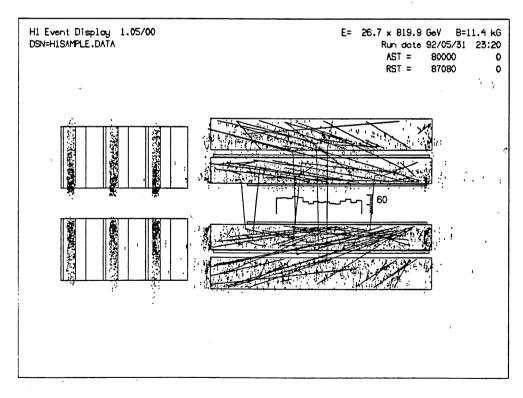

| 2.4  | Examples of Z-vertex histograms                                     |

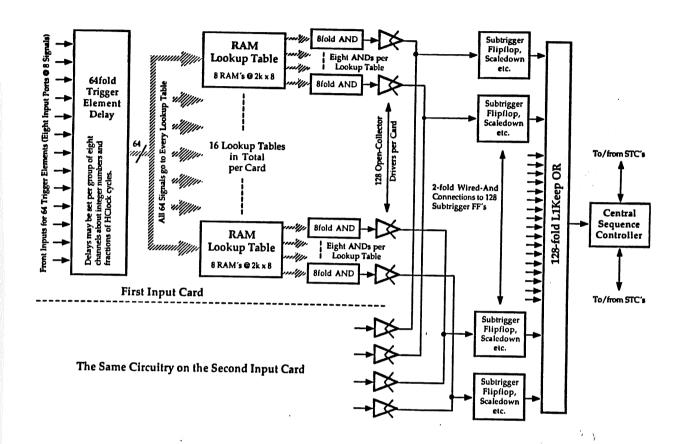

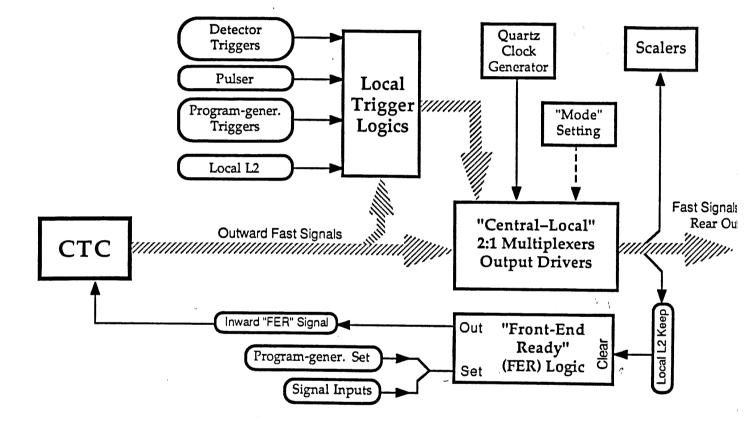

| 2.5  | Schematic overview of the L1 Central Trigger Decider                |

| 2.6  | Schematic view of the data flow through the acquisition chain 40    |

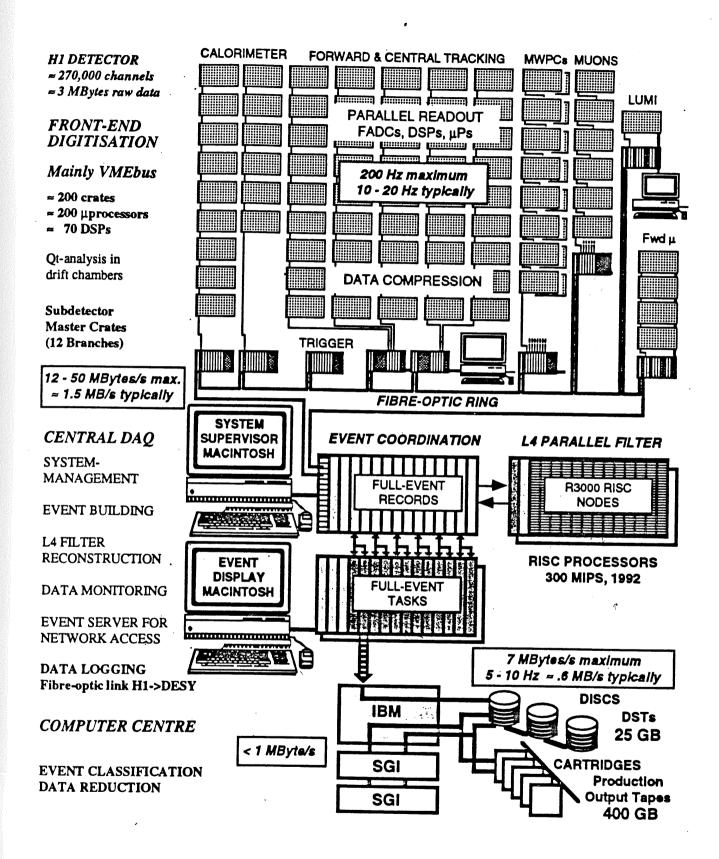

| 2.7  | Physical layout of the H1 data acquisition system                   |

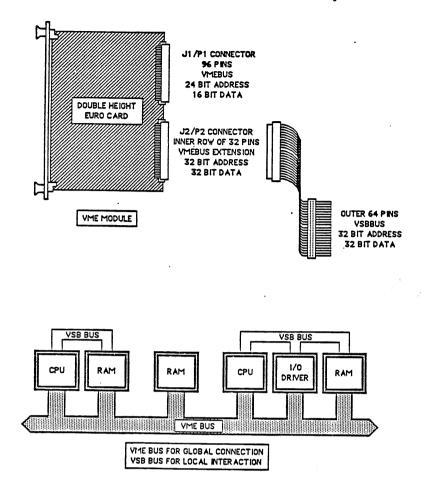

| 2.8  | VME bus architecture                                                |

| 2.9  | Reconstruction of CIZ signals with FADC 49                          |

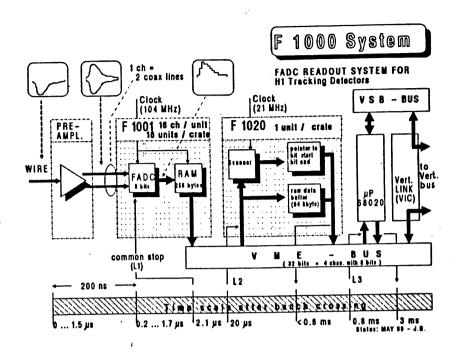

| 2.10 | Readout system of the H1 drift chambers                             |

| 2.11 |                                                                     |

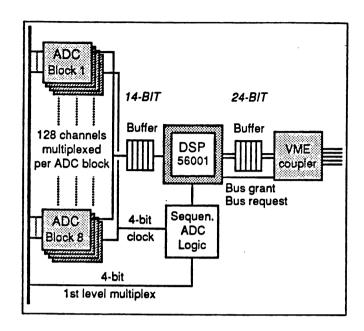

| 2.12 | Schematic of the H1 calorimeter ADC readout                         |

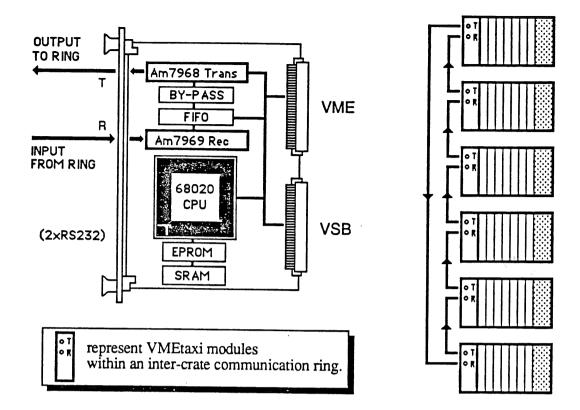

| 2.13 | VMEtaxi philosophy                                                  |

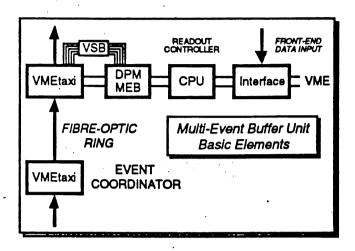

| 2.14 | Multi-event buffer readout                                          |

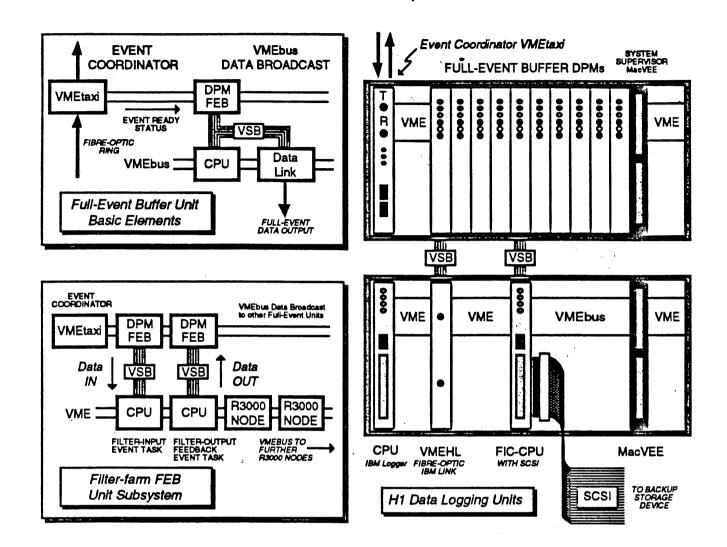

|      | Full-event buffer units                                             |

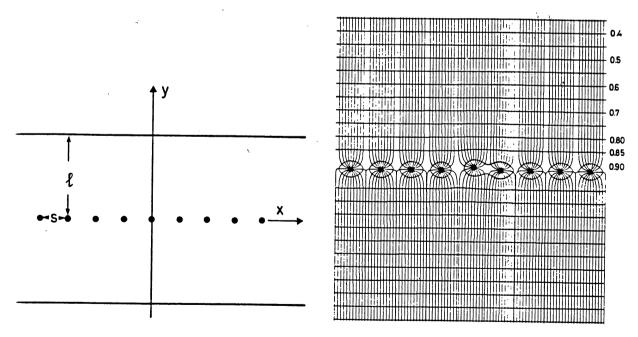

| 3.1  | Electric field equipotentials and field lines in a MWPC 58          |

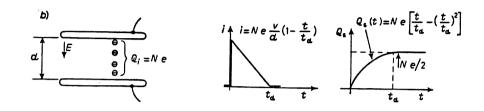

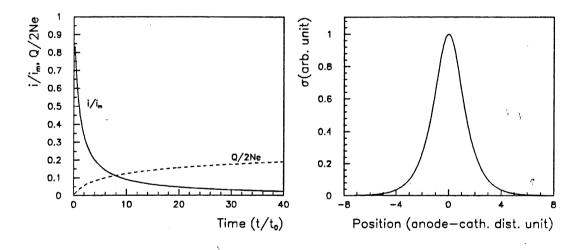

| 3.2  | Approximated induced current and charge waveforms 60                |

| 3.3  | Transversal view of the COP readout structure                       |

| 3.4  | Overview of the MWPC front-end electronic chain 64                  |

| 3.5          | Time distribution of the MWPC signals                                | 65          |

|--------------|----------------------------------------------------------------------|-------------|

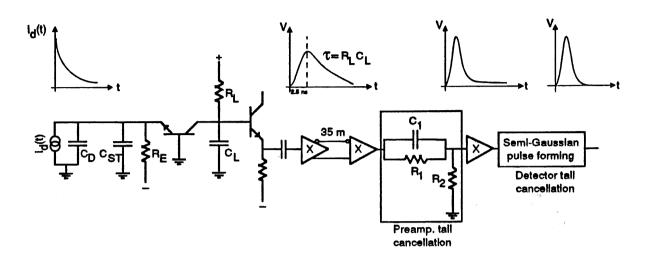

| 3.6          | MWPC analog signal processing chain                                  | 60          |

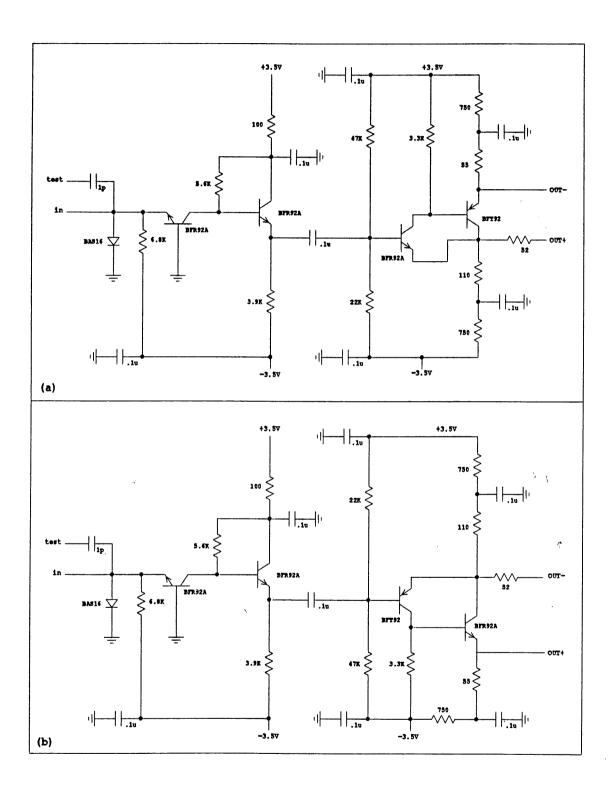

| 3.7          | Circuit diagrams of the MWPC preamplifiers                           | 68          |

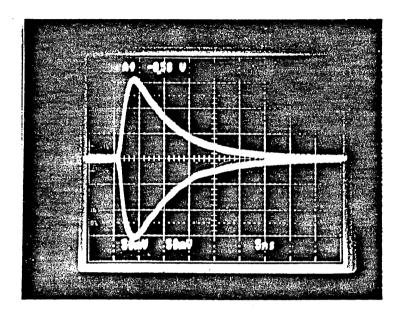

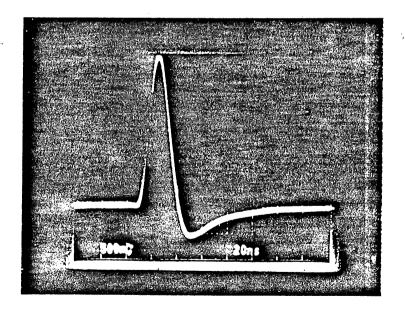

| 3.8          | Preamplier response                                                  | 69          |

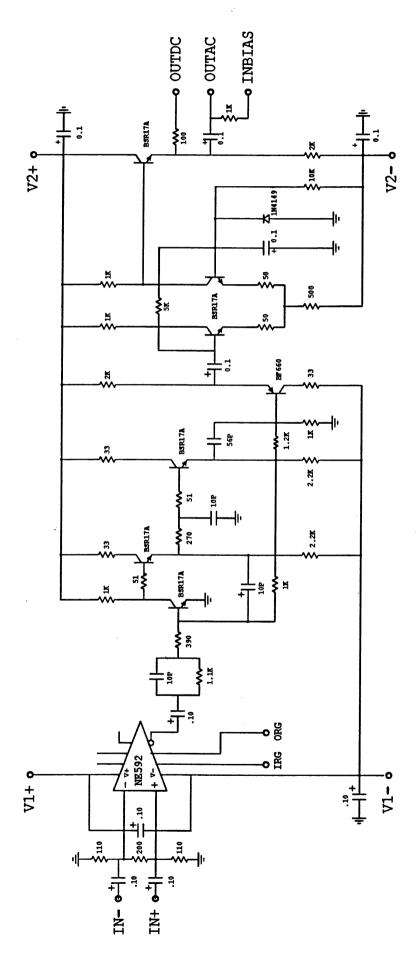

| 3.9          | Circuit diagram of the MWPC shaper                                   | 71          |

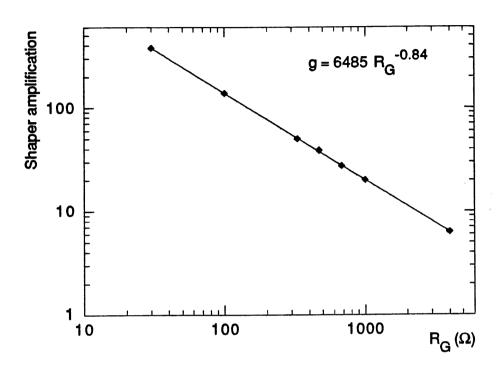

| 3.10         |                                                                      | 72          |

| 3.11         | Shaper response                                                      | 72          |

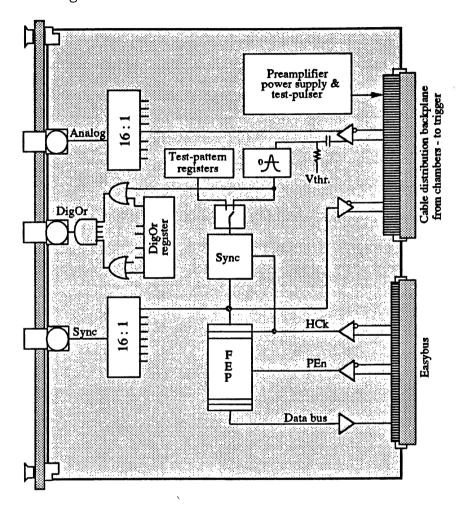

|              | Schematic overview of the Receiver Card                              | 74          |

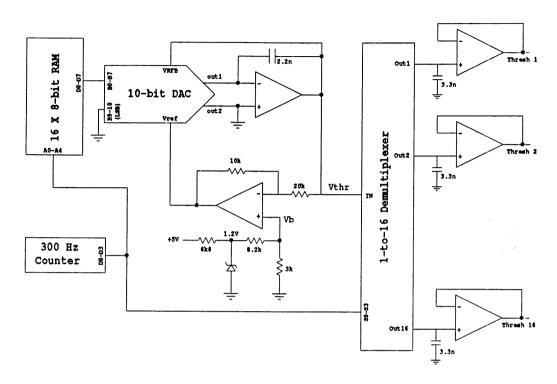

| 3.13         | Threshold circuitry                                                  | 70          |

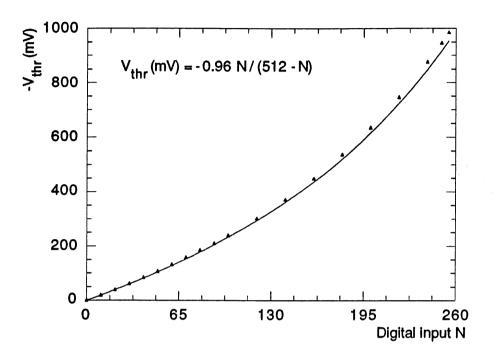

| 3.14         | Threshold voltage vs digital input                                   | 77          |

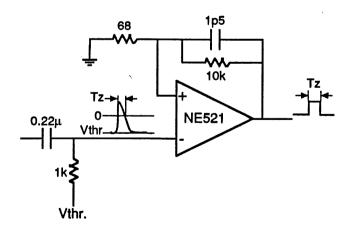

| 3.15         | Discriminator                                                        | 77          |

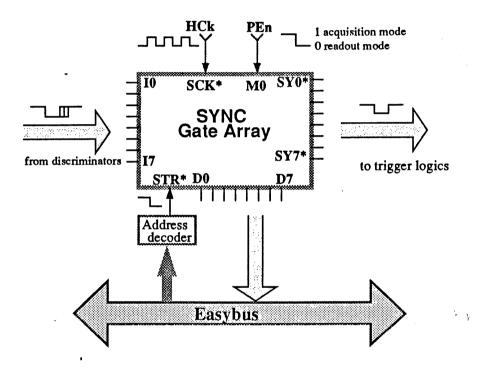

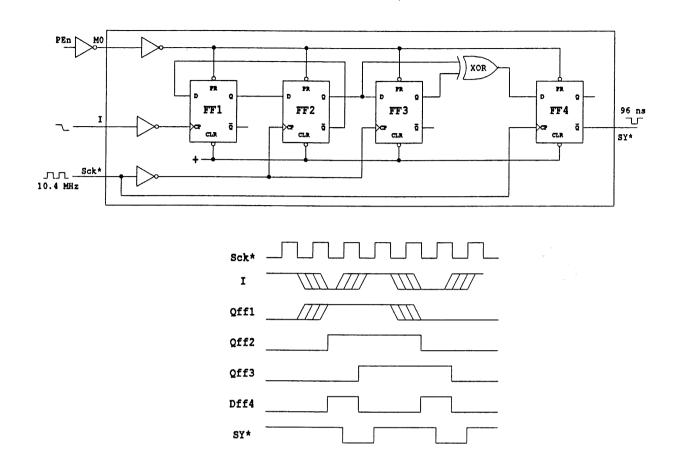

| 3.16         | Bloc diagram of the Sync GA                                          | 78          |

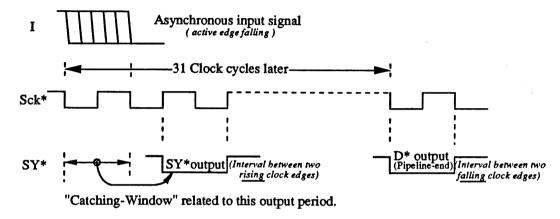

| 3.17         | The Sync GA - Basic relations between input and output               | 79          |

| <b>3</b> .18 | The Sync GA - Synchronization part                                   | 80          |

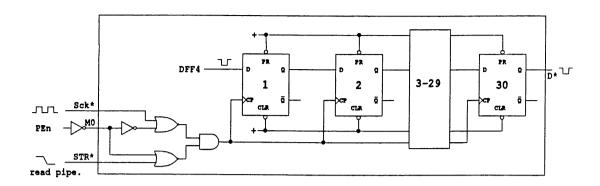

| 3.19         | Sync GA - Pipeline part                                              | 81          |

|              |                                                                      |             |

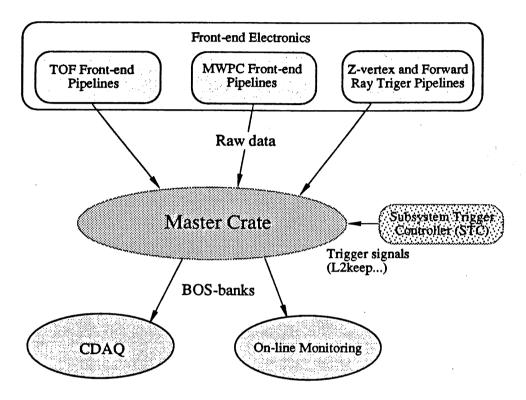

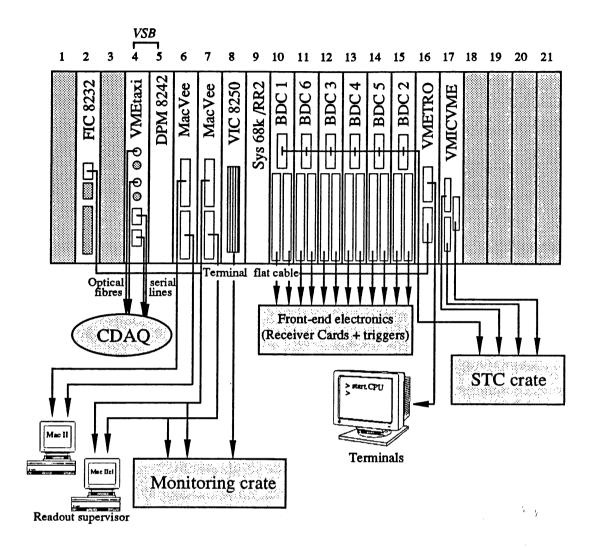

| 4.1          | MWPC readout system                                                  | 80          |

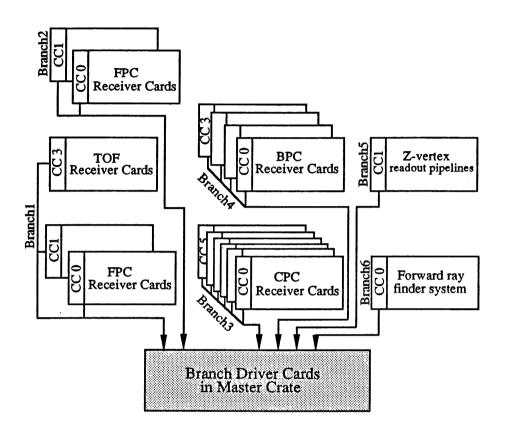

| 4.2          | Front-end crate configuration                                        | 87          |

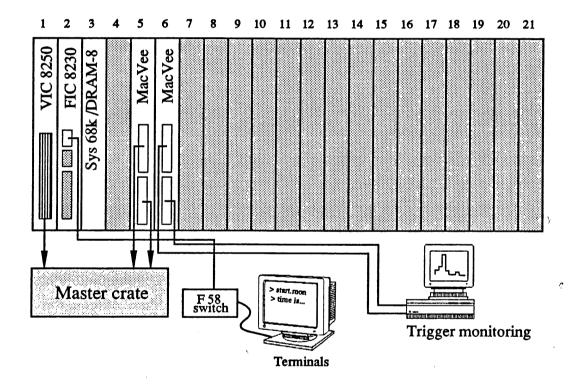

| 4.3          | Master Crate configuration                                           | 89          |

| 4.4          | Monitoring harware set-up                                            | 90          |

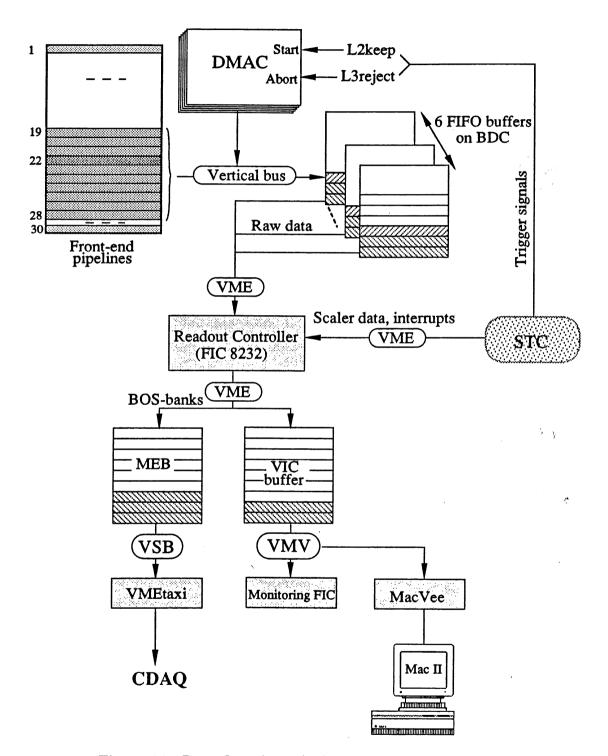

| 4.5          | Data flow through the MWPC readout system                            | 92          |

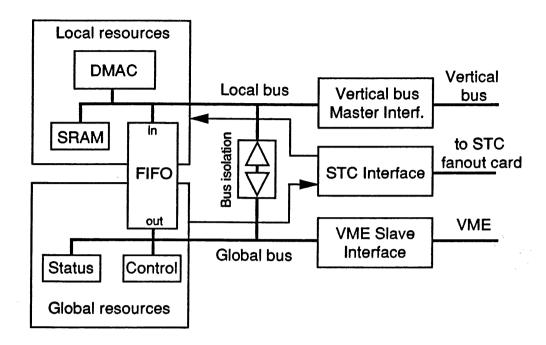

| 4.6          | BDC block diagram                                                    | 95          |

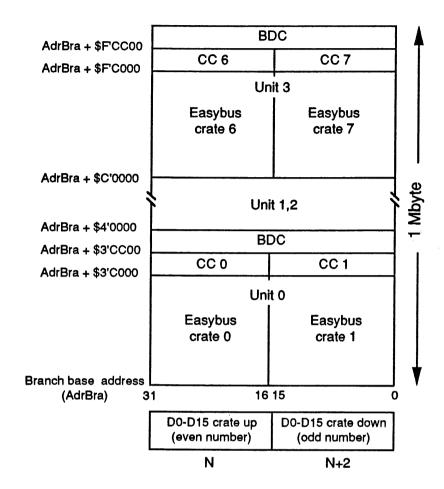

| 4.7          | Data organization in a branch                                        | 97          |

| 4.8          | DMAC configuration                                                   | <b>9</b> 9  |

| 4.9          | Controller Card block diagram                                        | 100         |

| 4.10         | Easybus data transfer                                                | 105         |

| 4.11         | Schematic overview of the Fast Card                                  | 108         |

| 4.12         | Block diagram of the FIC 8232                                        | 112         |

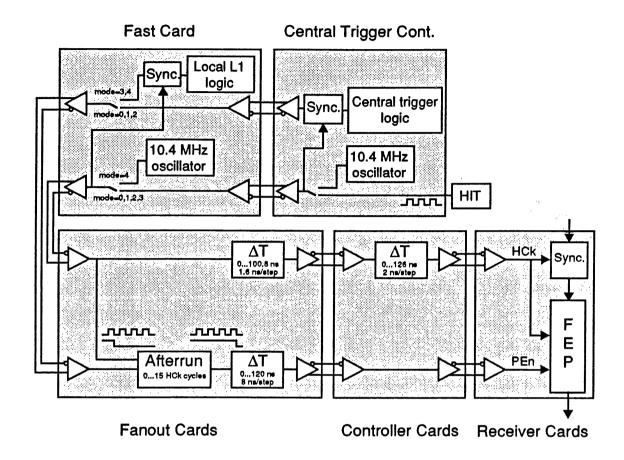

| 4.13         | Front-end pipeline control layout                                    | 115         |

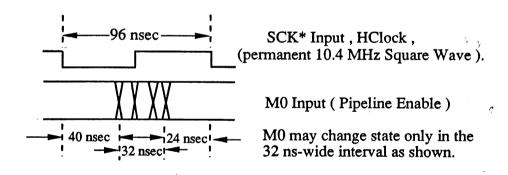

|              | Timing of M0 transitions relative to HCk                             | 116         |

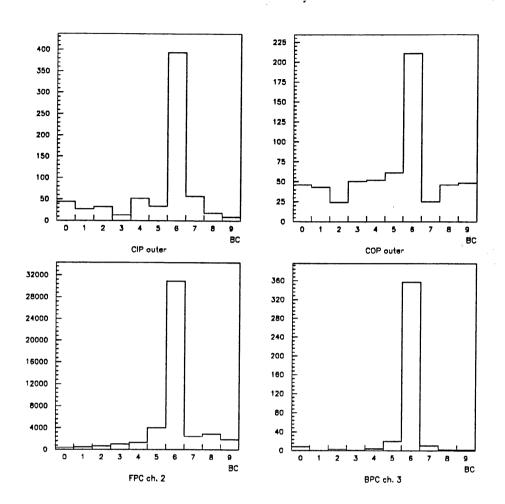

| 4.15         | Hit distribution in the front-end pipelines                          | 117         |

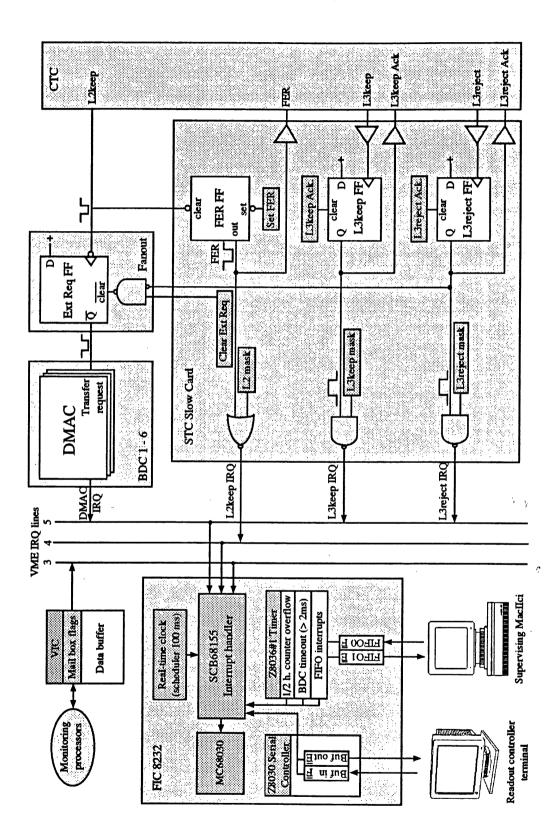

|              | Interrupt structure in the MWPC readout system                       | 119         |

|              | Time diagram of a readout cycle                                      | 121         |

|              | Single address DMAC read cycle timing diagram                        | 125         |

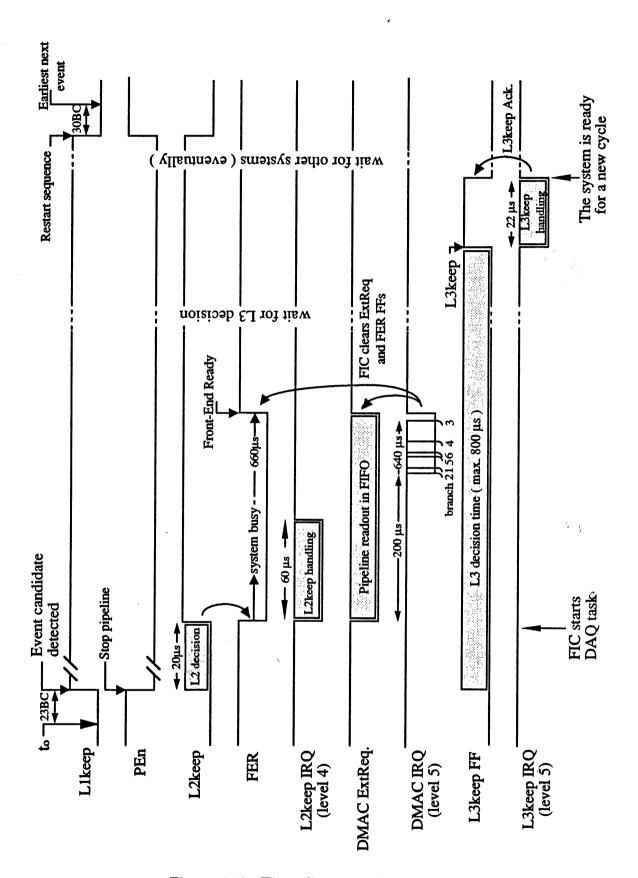

| 4.19         | DMA operation timing                                                 | 126         |

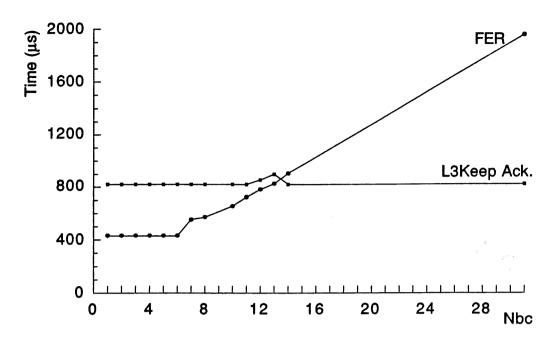

| 4.20         | Front-end freeing time                                               | 127         |

| 4.21         | L3keep cycle acknowledgment                                          | 128         |

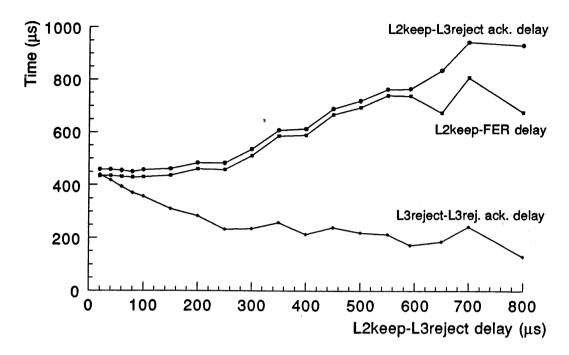

|              | L3reject cycle acknowledgment                                        | 129         |

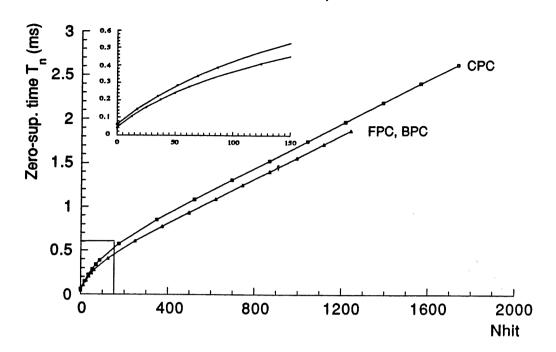

|              | Zero-suppression time of one data block                              | <b>13</b> 0 |

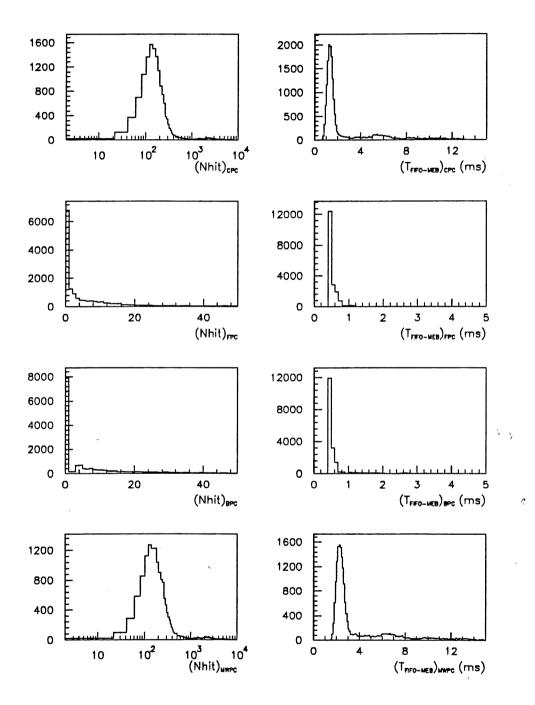

|              | Hit multiplicity and event building time in the MWPC readout         |             |

|              | partitions                                                           | 131         |

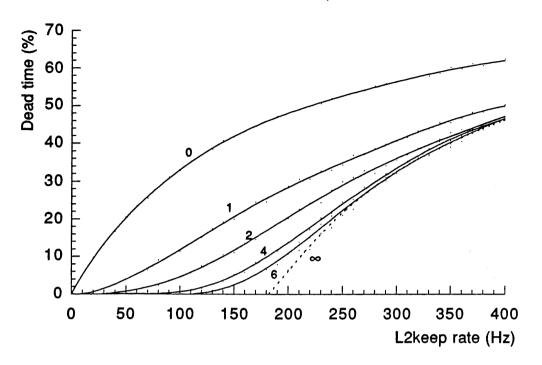

| 4.25         | Variation of fractional dead time with L2keep rate                   | 134         |

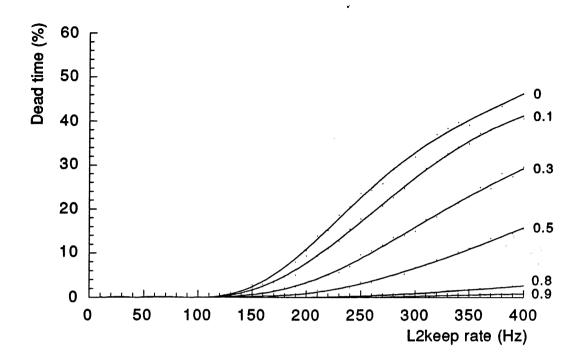

|              | Variation of fractional dead time for various L3reject/L3keep ratios | 135         |

# List of Tables

| 1.1 | Time between bunch crossings at existing and futur colliders | 5          |

|-----|--------------------------------------------------------------|------------|

| 1.2 | General parameters of HERA                                   | 6          |

| 1.3 | Dimensions and other specification of COP                    | <b>2</b> 2 |

| 2.1 | Expected event and background rates                          | 29         |

| 2.2 | H1 components and data partition                             | <b>3</b> 0 |

| 2.3 | Branch partition of the H1 data acquisition system           | 43         |

| 3.1 | MWPC system                                                  | 57         |

| 3.2 | Characteristics of the MWPC preamplifier                     | 67         |

| 3.3 | Characteristics of the MWPC shaper                           | 70         |

| 3.4 | Amplification in the different readout partitions            | 70         |

| 4.1 | Distribution of the front-end crates                         | 88         |

| 4.2 | Easybus pin assignments                                      | 104        |

| 4.3 | Interrupts on the Slow Card                                  | 109        |

| 4.4 | Fanout Card partition                                        | 111        |

| 4.5 | Event building in the MWPC readout chain                     | 132        |

| 4.6 | Buffer length in the readout branches as function of Nbc     | 133        |

#### Introduction

The last two decades have seen the construction of large particle accelerators providing collisions between leptons (LEP, SLC) or hadrons (Sp $\bar{p}$ S, TEVATRON). In 1991, the world's first lepton-hadron collider has been commissioned at the Deutsches Elektronen-Synchrotron (DESY) in Hamburg. The Hadron Elektron Ring Anlage - HERA - is designed to collide 820 GeV protons and 30 GeV electrons resulting in a center of mass energy of  $\sqrt{s} = 314$  GeV. The design luminosity is 1.5  $10^{31}$  cm<sup>-2</sup>s<sup>-1</sup>. This new collider offers the possibility to greatly extend our knowledge in the field of deep inelastic lepton-nucleon scattering. HERA increases the accessible kinematic range to values of  $Q^2 \sim 4 \cdot 10^4$  GeV<sup>2</sup> both for neutral and charged current scatterings, i.e. 2 orders of magnitude higher than at previous fixed target experiments.

At the present time, two general purpose detectors are operational at HERA: H1 and Zeus. A third experimental apparatus, the HERMES detector, is proposed to measure the spin dependence of the nucleon structure functions with longitudinally polarised electrons. The H1 and Zeus experiments have collected their first data during the period from June through November 1992. At that time the accelerators collided beams of 26.7 GeV electrons with 820 GeV protons at about 2 permile of the design luminosity. The next run is currently scheduled to begin in June 1993.

HERA presents a technical challenge for both the detectors and the data acquisition systems that is unique within the High Energy Physics environment. To operate at the design luminosity, 210 electron and proton bunches are used, providing a new crossing every 96 ns, i.e. approximately 100 times more frequent than at LEP. For the first time, data have to be tested for possible triggers at an input rate of 10<sup>7</sup> MHz without impeding the system with a large dead time. This requires a novel approach to data acquisition and trigger processing. For instance, the first level trigger has to work in a pipelined mode and storage elements have to be provided for every detector channel before hardware and software processing. Synchronization between the various system components is a major issue that deserves special consideration. In this context, the experience gained at HERA regarding triggering techniques and data processing certainly forms an important input to the design of front-end data acquisition systems for the next generation high rate hadron colliders.

The work presented in this thesis concerns the data acquisition system used to readout the data of all the multiwire proportional chambers (MWPC) in the H1 detector. As a member of the H1 collaboration since 1987, I took an active part in the design, the development and the commissioning of this system. My main responsibilities consisted in the conception and the development of the front-

end data acquisition system based on an inter-crate connection which transfers the buffered front-end data into a memory accessible to the central DAQ system. These transfers are executed by a DMA controller without processor intervention making use of on-board FIFO buffers. I furthermore designed the printed circuit boards that hold the preamplifiers for the Central Outer Proportional chamber and was deeply involved in the tests of the front-end electronics. During the commissioning phase, I was responsible for the implementation of the MWPC readout system at the DESY laboratory.

Chapter 1 describes the experimental framework. An overview of the HERA collider and its injection system is first given. Next, the major criteria that must be taken into account when designing an experiment at HERA are considered. The kinematics of e-p interactions are briefly reviewed followed by a short discussion of event signatures. The problem of the determination of the bunch crossing time is introduced. The last section describes the H1 detector with special focus on the tracking system.

Chapter 2 describes the H1 data acquisition system in general. An overview of the principal parameters which have determined the system architecture is first presented. In particular the bunch crossing rate, the event rate, background rates and the data volume are discussed. Furthermore, an overview of the H1 trigger system is presented followed by a description of the consecutive steps of the acquisition procedure. Hardware details are outlined in the last section with an introduction to the VMEbus specification as well as a description of the major front-end systems and of the central data acquisition.

Chapter 3 describes the analog signal processing in the MWPC system. The principles of particle detection in multiwire proportional chambers are first reviewed together with a description of the pad readout technique used for the central and forward MWPC detectors. Subsequently, the front-end electronic chain is outlined including in particular a description of the preamplifier, the shaper and the Receiver Card.

Chapter 4 is devoted to the Receiver Card readout system. Its general structure is first presented together with a description of the data flow through the different buffering stages. Then, the data acquisition modules are reviewed. The custom-built components are described in some detail with a particular attention to those related to the inter-crate connection. The synchronization mechanisms are then presented. The logic used to control the front-end synchronizer and pipeline is first described followed by the interrupt protocol used for controlling the readout tasks. The performance of the system is analysed in terms of its data transfer rate dead time.

Finally, a summary of the main characteristics of the system is given and the general conclusions are drawn.

# Chapter 1

# H1 at HERA: The Collider and the Experiment

#### 1.1 Introduction

High energy lepton-nucleon scattering has played an essential role in our understanding of the constituents of matter and their interactions. The early deep inelastic electron scattering experiments at SLAC revealed the parton structure of the nucleon. Since then many further insights have been provided by experiments using neutrino and muon beams. For instance, the existence of the weak neutral current interaction was first demonstrated in 1973 at CERN in  $\nu_{\mu}p$  scattering processes. These observations were the experimental foundation of quantum chromodynamics (QCD), the gauge theory of strong interactions.

This line of research is now continued at the new and first electron-proton collider HERA at DESY that allows collisions between 820 GeV protons and 30 GeV electrons. This facility opens a new kinematical region for physics measurements inaccessible to fixed target experiments. At HERA, the momentum transfer squared between the electron and the proton can reach a value as large as  $Q^2 \sim 4 \cdot 10^4 \, GeV^2$ , i.e. about 2 orders of magnitude higher than at the CERN and FNAL fixed target experiments. For the first time, lepton-nucleon scattering events are studied at momentum transfers comparable with the rest masses of the  $W^{\pm}$  and  $Z^0$  gauge bosons, where the weak and electromagnetic interactions are of comparable strength. The simultaneous measurement of charged current and neutral current cross sections offers the possibility to perform precision tests of the Standard Model and to eventually establish deviations from the theory. With HERA, it will be possible to probe the electron and the quarks down to distances of  $\sim 10^{-18}$  m and search for possible sub-structures at dimensions which are an order of magnitude smaller than possible with present-day accelerators. A detailed

view of the physics program at HERA is presented in [1] and [2].

To study e-p interactions at HERA, two large complex detectors, called H1 and ZEUS, have been installed at two interaction points. In these detectors, the reaction products from head-on collisions between electrons and protons circulating in opposite directions in the storage rings are measured and recorded. The design and construction of these two devices result from a common effort of about 550 physicists and engineers from 16 countries. The Interuniversity Institute for High Energies ULB/VUB figures as one of the participating institutes of the H1 collaboration. Its hardware contribution consists in the construction of the Central Outer Proportionnal Chamber (COP), one of the components of the H1 track detector, and the development of the readout electronics of the MWPC detection system.

In this chapter, an overview of the HERA collider and the H1 experiment is presented. In the first section, the HERA rings and the preaccelerator complex are described. Next, experimentation at an e-p collider is discussed, before describing the H1 detector. We will then focus on the tracking devices and more particularly on the COP detector.

#### 1.2 The HERA Collider

#### 1.2.1 Introduction

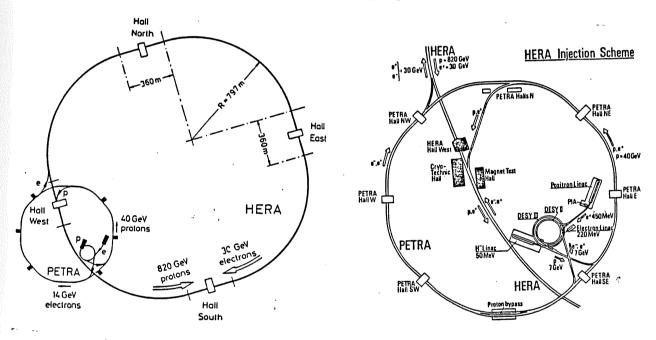

The Hadron Elektron Ring Anlage (HERA) consists of two separate 6.3 km long rings, designed to accelerate and to store respectively 820 GeV protons and 30 GeV electrons (positrons) and to allow the collision of the two counterrotating beams head on in four interaction points [3]. The layout of HERA with its injection system is shown in Fig 1.1. The main parameters are listed in table 1.2.

At the nominal beam energies, the center of mass energy is

$$\sqrt{s} \simeq \sqrt{4E_{\epsilon}E_{p}} = 314 \ GeV$$

(1.1)

equivalent to an electron beam of 51 TeV incident on a stationary target. The design luminosity is  $1.5 \, 10^{31} \, \text{cm}^{-2} \, \text{s}^{-1}$  leading to data samples of typically  $100 \, \cdot 200 \, pb^{-1}/\text{year}$ . To obtain this luminosity, both beams are bunched in 220 equidistant buckets, out of which 210 are filled with particles, providing a crossing every 96 ns. This time is much shorter than the beam crossing time at the present day accelerators and approaches the bunch separation at the future hadron colliders (see table 1.1.).

| Collider | Type                 | $\Delta t$             |

|----------|----------------------|------------------------|

| LEP      | $e^+e^-$             | $11~\mu \mathrm{s}$    |

| TEVATRON | ${ m p}\overline{p}$ | $3.2~\mu \mathrm{s}$   |

| HERA     | e-p                  | $96~\mathrm{ns}$       |

| LHC/SSC  | рp                   | $15/16 \; \mathrm{ns}$ |

Table 1.1: Time between bunch crossings at existing and futur colliders.

HERA will provide the possibility to collide the protons with longitudinally polarized electrons or positrons. This offers the opportunity to do experiments with predominantly left or right handed  $e^{\pm}$  and opens new possibilities in the investigation of the chiral structure of the gauge interactions.

Figure 1.1: Layout of HERA and its preaccelerators

#### 1.2.2 The Injection Systems

The electron injection system of HERA is based on the rebuilt Deutsches Elektronen-Synchrotron (DESY) and the modified storage ring PETRA previously used for  $e^+e^-$  collisions. The electrons from a 500 MeV linear accelerator are injected into a small storage ring where they are accumulated into a 60 mA single bunch. They are then injected into the synchrotron DESY II, accelerated to 7 GeV, and transferred to the PETRA ring. After accumulating up to 70 bunches with the final

bunch spacing of 28.8 m, the PETRA energy is ramped up to 14 GeV and at that energy, the bunches are transferred to HERA. This process is repeated until HERA is filled with 210 bunches.

|                             | p-ring                      | e-ring     | units                             |

|-----------------------------|-----------------------------|------------|-----------------------------------|

|                             |                             |            |                                   |

| Nominal energy              | 820                         | <b>3</b> 0 | ${ m GeV}$                        |

| Polarization time           |                             | <b>2</b> 8 | min                               |

| Luminosity                  | 1.5 ×10                     | $0^{31}$   | $cm^{-2} s^{-1}$                  |

| Space between IR Quad       | 15                          |            | m                                 |

| Interaction points          | 4                           |            |                                   |

| Crossing angle              | 0                           |            | mrad                              |

| Circumference               | 6336                        | ;          | m                                 |

| Magnetic field              | 4.68                        | 0.165      | $\mathbf{T}$                      |

| Number of particles         | 2.1                         | 0.8        | 10 <sup>13</sup>                  |

| Number of bunches           | 210                         |            |                                   |

| Injection energy            | 40                          | 14         | ${ m GeV}$                        |

| Filling time                | 20                          | 15         | min                               |

| $\sigma_x/\sigma_y$ at I.P. | 0.29/0.07                   | 0.26/0.02  | min                               |

| $\sigma_z$ at I.P.          | 110                         | 8.0        | ının                              |

| Energy loss / turn          | $6.24 \times 10^{-6}$       | 127        | ${ m MeV}$                        |

| Circumferential RF Voltage  | 0.2/2.4                     | 260        | ${f MV}$                          |

| RF-Frequency                | 52.033/208.13               | 499.776    | $\mathbf{MHz} \rightarrow \gamma$ |

| RF-power                    | 1                           | 13.2       | MW                                |

| Refrigerator                | 21.0 kW (isothermal at 4.K) |            |                                   |

|                             | 60 g/s Liq. He              |            |                                   |

| •                           | 60 kW (40 K -               | 80 K)      |                                   |

|                             |                             | •          |                                   |

Table 1.2: General parameters of HERA

The proton injection complex is based on a whole new chain of preaccelerators. Negatively charged hydrogen ions are first accelerated to 750 KeV and then injected into a 50 MeV linear accelerator. The  $H^-$  ions are stripped upon entering into the synchrotron DESY III where they are captured into 11 RF buckets with the final bunch spacing. The protons are then accelerated to 7.5 GeV and transferred to PETRA. After filling with at most 70 bunches, the protons are accelerated to 40 GeV and the train of bunches transferred to HERA.

The total filling time is expected to be 15 min. for the electrons and 20 min. for the protons.

#### 1.2.3 The HERA Rings.

#### 1.2.3.1 The Electron Ring.

For 30 GeV electrons, a modest bending field of 0.165 T is required and can be achieved with conventional magnets. The energy lost by synchrotron radiation (127 MeV/turn at E = 30 GeV) is compensated by 500 MHz RF cavities located along the electron beam. HERA is equipped with 83 such cavities, previously used at PETRA, and 8 additional superconducting cavities to reach the nominal energy of 30 GeV.

#### 1.2.3.2 The Proton Ring.

To keep the 820 GeV protons on orbit, a bending field of 4.68 T and a quadrupole gradient of 90 T/m are required. For this purpose, a new design of superconducting Nb-Ti magnets was devised in which the iron is at liquid He temperature. To obtain the required field uniformity, a mechanical precision of 20  $\mu$ m on the conductor location had to be maintained over the 9 m dipole length. The quadrupole and sextupole correction magnets are also superconducting, whereas normal conducting magnets are used to guide the protons in the four straight sections. The quality of the magnets is such that at 4.6 K, the quench occurs at 5.8 T and operation at 1 TeV is not out of the question. As the energy loss due to synchrotron radiation is negligible for protons, conventional RF cavities and klystrons are used.

#### 1.3 Experimentation at HERA

To study e-p interactions at HERA, two general purpose detectors, H1 and Zeus, have been built. Before describing the H1 detector, let us consider the major criteria that have to be taken into account when designing experiments at HERA.

#### 1.3.1 Kinematics

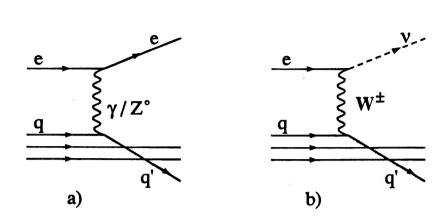

The dominating interactions at HERA are the neutral current (NC) scattering process  $\epsilon p \to \epsilon X$  and the charged current (CC) process  $\epsilon p \to \nu_{\epsilon} X$ . Figure 1.2 shows the relevant Feynman diagrams that describe, at the lowest order, these classes of interactions.

In the parton model of the proton, the incoming electron interacts directly with one of the quarks inside the proton via a spacelike neutral  $(\gamma/Z^0)$  or charged

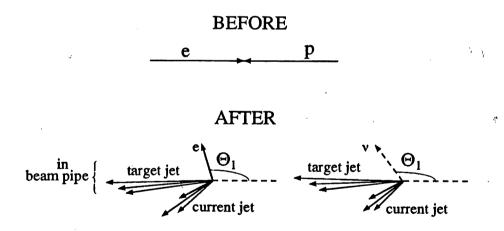

Figure 1.2: Feynman diagrams for neutral (a) and charged (b) current e-p interactions

$(W^{\pm})$  current. The struck quark will materialize as a jet (current jet) of hadrons whose transverse momentum  $p_t$  is balanced by the scattered lepton. Occasionally, the quark will radiate a high energy gluon that gives rise to a well separated two jet structure (gluon jet and quark jet) in the current fragmentation region. The remainder of the proton will appear as a sharply collimated jet (target jet) of hadrons leaving the interaction region in a narrow cone ( $\sim 10$  mrad) around the proton beam direction (see figure 1.3).

Figure 1.3: Topology of deep inelastic e-p scattering events

To give the basic kinematical expressions, let  $p_{\epsilon}$ ,  $p_{l}$ ,  $E_{\epsilon}$ ,  $E_{l}$  be the four-vectors and the energies of the incoming and scattered leptons, P the four-vector of the incoming proton, and  $\Theta_{l}$  the scattering angle of the outgoing lepton. The total mass squared is

$$s = (p_e + P)^2 \simeq 4E_e E_p \tag{1.2}$$

where the sign " $\simeq$ " means that the lepton and proton masses are neglected with respect to energies in the laboratory frame [4].

The  $Q^2$  variable is defined to be minus the square of the four-vector  $q = p_e - p_l$  of the exchanged boson :

$$Q^{2} \equiv -q^{2} = -(p_{e} - p_{l})^{2} \simeq 4 E_{e} E_{l} \sin^{2} \frac{\Theta_{l}}{2}$$

(1.3)

The energy transferred to the hadronic final state in the proton rest frame, defined as  $\nu$ , is given by the relation :

$$m_p \nu \equiv P \cdot q \simeq 2E_p (E_e - E_l \cos^2 \frac{\Theta_l}{2})$$

(1.4)

Let us now define the convenient dimensionless Bjorken - x and y variables:

$$x \equiv \frac{Q^2}{2P \cdot q} \simeq \frac{E_{\epsilon} E_l \sin^2 \frac{\Theta_l}{2}}{E_p (E_e - E_l \cos^2 \frac{\Theta_l}{2})}$$

(1.5)

$$y \equiv \frac{P \cdot q}{P \cdot p_l} \simeq \frac{E_{\epsilon} - E_l \cos^2 \frac{\Theta_l}{2}}{E_{\epsilon}} \tag{1.6}$$

with

$$Q^2 = sxy \tag{1.7}$$

These variables are always in the range  $0 \le (x, y) \le 1$  and are independent of any proton or electron model assumption. By assuming the quark-parton model, where the current couples to a quark, and assuming the initial and final quark to be massless, the Bjorken-x variable can be interpreted as the momentum fraction of the proton carried by the struck quark. However, taking QCD corrections into account this interpretation no longer holds [5].

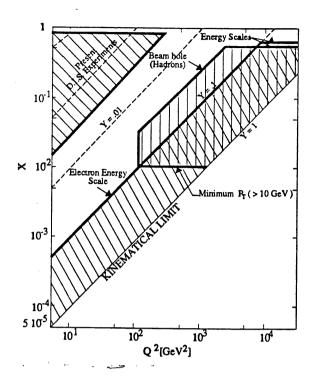

Any two of the above variables can be used as independent variables to describe the phenomenology of the e-p interactions. The couples (x, y) and  $(x, Q^2)$  are most commonly used. Figure 1.4 shows the experimentally accessible regions at HERA and in the present fixed target experiments. There is about an order of magnitude in  $Q^2$  between the end points of both domains. Some overlap may be established by running the HERA accelerators at lower energies. HERA extends the kinematical range by two orders of magnitude down to values of  $x = 10^{-4}$ . This small x region may be viewed as the fixed target region of HERA where the struck quarks are almost at rest. There is a strong interest to investigate these events because at very low values of x and large values of  $Q^2$ , the parton density in the nucleon is expected to grow rapidly leading to possible interactions between the partons. New physics phenomena are therefore expected in this domain which could lead to corrections in the perturbative QCD theory.

Figure 1.4: Experimentally accessible regions for structure function measurements at HERA nominal beam energies of 30 GeV electrons and 820 GeV protons. The domains covered by vertical and 60° hatched lines specify the regions where differential cross-sections are expected to be measurable with less than 10% systematic errors from the reconstruction of the visible hadron flow and the scattered electron, respectively. Taken from [6].

#### 1.3.2 Event Signatures

From the experimental point of view, the variables x, y and  $Q^2$  can be determined in neutral current events from the energy  $E_l$  of the outgoing lepton and its scattering angle  $\theta_l$  by using equations 1.3, 1.5 and 1.6. These events are characterised by an isolated high energy electron ( $E \ge 30 \text{ GeV}$ ) balanced in  $p_t$  by the jet(s). On the other hand, a charged current event is signaled by high  $p_t$  jet(s) with missing transverse energy due to the non detection of the emitted neutrino. In that case, only the information from the hadron system can be used. The above variables must then be expressed in terms of the total current jet energy  $E_j$  and of the polar angle  $\theta_j$ . This method requires that one disentangles particles of the current jet from particles of the target jet, which in practice may well be impossible. To overcome this problem, A. Blondel and F. Jacquet have proposed a method to determine the kinematical variables in charged current events based on measured quantities summed over the complete hadron system [7]:

$$y = \sum_{h(all\ hadrons)} \frac{(E_h - p_{zh})}{2E_e}$$

(1.8)

$$Q^{2} = \frac{P_{t}^{2}}{(1-y)} = \frac{|\sum \vec{p}_{th}|^{2}}{(1-y)}, \quad x = \frac{Q^{2}}{sy}$$

(1.9)

where  $P_t$  is the total transverse momentum of the hadron flow,  $p_{zh}$  the longitudinal momentum component and  $\vec{p}_{th}$  the transverse momentum of the hadron h. In these equations, the contribution of particles going into the beam hole is small relative to the contribution of particles with larger  $\Theta$ . For x < 0.5 and  $Q^2 > 100 GeV^2$ , the relative errors in x and  $Q^2$  remain below 10% [8].

The physics topics outlined above demand the following main detector components:

- a high quality hadron calorimetry for precise energy flow measurement, combined with an electromagnetic calorimeter to identify and to measure the scattered electrons. A high degree of hermiticity is needed to minimize any missing energy.

- a track detector operating in a magnetic field for particle emission angle and momentum measurements and for particle identification by a dE/dx measurement.

- a muon detector for a correct determination of the total visible energy since muons deposit only a fraction of their energy in the calorimeter. With the electrons, the muons are expected to provide signatures for new phenomena involving heavy flavours and new particle production. They will be identified by their penetration through the absorption materials of the detectors and measured by tracking chambers situated outside of the other detector subcomponents.

#### 1.3.3 Determination of the Bunch Crossing Time

The 96 ns time separation between bunch crossings imposes several constraints on the design of a detector at HERA. Most of the usual detector components have a charge collection time which is much larger than 96 ns. For instance, the signals from the H1 calorimeter have a length of about 500 ns and the maximum drift time in the tracking chambers approaches  $2\mu$ s. This means that the signal processing time for a particular event has to be at least of this duration to measure all deposited charge. As a consequence, events arising from consecutive interactions may overlap during the resolving time of the detector. It is therefore essential to be able to determine uniquely to which HERA beam crossing each detector signal is associated. An erroneous bunch-event association would result in wrong drift distances and particle energies.

The determination of the beam crossing time requires devices which can correlate the data from the different parts of the detector with a specific bunch crossing.

For this purpose, multi-wire proportional chambers may be used. Provided a small wire spacing (typically 2 mm) and a suitable gas are chosen, the drift time will be much smaller than 96 ns and simple discrimination on the chamber pulses will define uniquely the bunch crossing time  $t_{\theta}$ . Bunch crossing identification is also possible with detector components which do not have single bunch crossing response times. For instance, the arrival time of liquid ionization calorimeter signals can be derived from the zero-crossing of their predictable pulse shape [9].

#### 1.4 The H1 Detector

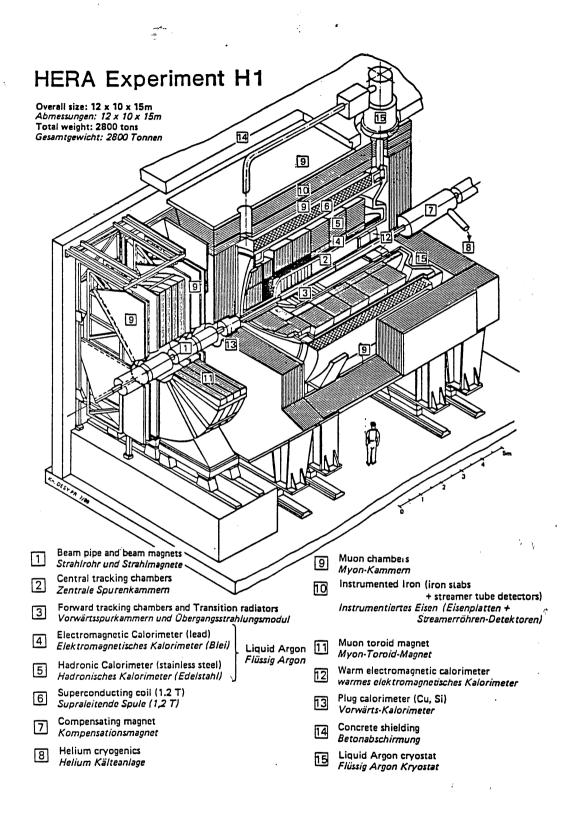

H1 is a general purpose detector for HERA designed to measure with high precision particles and jets with energies up to 820 GeV. The detector has been optimized for the study of neutral and charged current interactions and, in particular, for the measurement of the energy and momentum of single electrons. The overriding design goal has been a large, finely grained, calorimeter covering nearly  $4\pi$ , enhanced by tracking and particle identification elements. As in e-p interactions, the track densities and particle momenta are much larger in the forward (proton) direction than in the barrel and backward (electron) regions, the detector has an asymmetric shape. A view of the detector is presented in figure 1.5. A brief overview of the detector components is given below, followed by a more detailed description of the tracking detector which includes the multiwire proportional chambers.

#### 1.4.1 Detector Scheme

The heart of the H1 detector [9] is a liquid argon (LAr) calorimeter covering the forward ( $4^{\circ} < \Theta < 20^{\circ}$ ) and central ( $20^{\circ} < \Theta < 152^{\circ}$ ) detector regions. It is composed of an electromagnetic section (4), with 2.4 mm thick lead absorber plates and 2.35 mm argon gaps, and a hadronic section (5) with stainless steel plates of 19 mm thick combined with a double gap of 2 × 2.3 mm argon. The depth of the electromagnetic section varies between 19 and 30 radiation lengths while the hadron containment is obtained with 4.7 to 8 absorption lengths of LAr stacks. Both parts are welded together within a single vacuum insulated cryostat.

The liquid argon technique allows for a fine readout segmentation both transverse and longitudinal to the beam axis. Transversely, the granularity varies between 10 and  $100 \ cm^2$  in the electromagnetic calorimeter and between 50 and  $2000 \ cm^2$  in the hadronic part. Longitudinally, the electromagnetic shower is sampled 43 to 119 times, the hadronic shower 16 to 36 times. This fine segmentation allows to correct for the different electromagnetic and hadronic responses and consequently improve the energy resolution. This is done by a weighting algorithm applied to the individual longitudinal and transverse energy distribu-

Figure 1.5: The H1 detector

tions which equalises the relative responses of electrons and photons with the hadron one. After this correction, an energy resolution for hadronic showers of  $\sigma(E)/E = 0.50/\sqrt{E({\rm GeV})}$  is achieved. The electromagnetic energy resolution is  $\sigma(E)/E = 0.12/\sqrt{E({\rm GeV})}$ .

The LAr calorimeter is completed in the backward direction by an electromagnetic calorimeter (BEMC) which covers the angular range  $151^{\circ} < \Theta < 176^{\circ}$  (12). It is a lead-scintillation sampling calorimeter with photodiode readout. The energy resolution for the electrons is approximately the same as for the liquid argon calorimeter. In the forward region, a plug calorimeter (13) covers the angular range  $12.5 \ mr. \leq \Theta \leq 60 \ mr.$  and measures the hadronic energy flow which escapes the LAr calorimeter. It is made of copper absorber plates sandwiched with silicon detectors.

Charged particle tracking is provided by a set of drift chambers inside the calorimeter. In the central region, the tracker (2) consists of a central jet chamber interleaved with 2 layers of z-drift chambers and multiwire proportional chambers (MWPC). In the forward region, a series of radial and planar drift chambers, interleaved with MWPCs and transition radiators, are installed (3). In the backward region, four layers of MWPCs close the tracking detector. This system is described in more detail in the next section.

A Time of Flight (TOF) device consisting of a double wall of scintillators is installed inside the tracker tank immediately behind the BEMC. It is used to generate a veto on background particles travelling with the beam (halo, beam-gas or beam-wall collisions).

The detector components discussed so far are installed inside a superconducting coil (6) and operate in a longitudinal magnetic field of 1.2 T. Around the solenoid, an iron structure (10) acts as the return yoke for the magnetic field. It is fully instrumented with gas counters, operating in the limited streamer mode, to measure the hadronic energy leaking out the main calorimeter (tail catcher) and to detect the muons. This system is supplemented in the proton direction by a muon spectrometer composed of a iron toroid (11), with a field of 1.2 T, and four layers of drift chambers.

In the electron direction, two large VETO walls made of scintillator counters are placed at z=-6.5 m and z=-8 m from the interaction point. They are used to identify penetrating particles produced upstream in the proton beam line in beam-gas and beam-wall interactions and the shower leakage in the beam pipe from the e-p interactions.

In the same direction, a photon and an electron detector are placed at small angles located at distances of about 107 m and 37 m. These detectors measure the luminosity and tag interactions with small momentum transfer. Each com-

ponent consists of a crystal calorimeter with an energy resolution of  $\sigma(E)/E = 0.12/\sqrt{E(GeV)}$ . The luminosity is determined using the Bremsstrahlung process  $e + p \rightarrow e + p + \gamma$  in which the energy of the electron and the photon are measured. As the electron beam-gas interaction produces also Bremsstrahlung, a subtraction is made by measuring this component with noncolliding electron bunches.

#### 1.4.2 Tracking Detectors

#### 1.4.2.1 Introduction

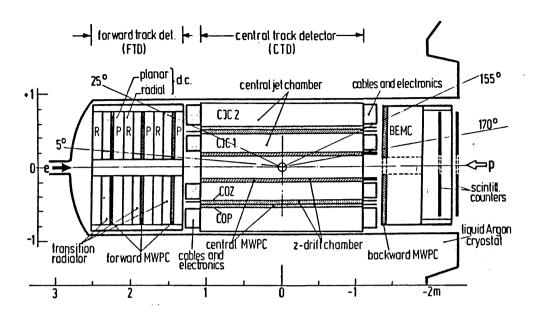

The tracking system of the H1 detector is located within the cryostat of the LAr calorimeter. Its layout is shown in figure 1.6. Due to the particular event topology of e-p collisions, the tracker is subdivided into two parts, the central track detector (CTD) and the forward track detector (FTD):

- The CTD covers the angular region 25° < Θ < 160°. It consits of two jet chambers (CJC1, CJC2) interleaved with 2 sets of z-drift chambers (CIZ, COZ) and MWPCs (CIP, COP).</li>

- The FTD occupies a cylindrical volume in the proton direction ( $5^{\circ} < \Theta < 25^{\circ}$ ) where over 50% of the particles are expected to enter. It is constructed as a set of 3 identical subunits (supermodules) which repeat along z. Starting from the interaction point, each supermodule contains one planar, drift chamber, followed by a MWPC plane, then a transition radiator and finally a radial drift chamber.

The drift chambers of the tracking system have been designed to reconstruct jets with high particle densities. A double-track resolution of about 2.5 mm is obtained and momenta and angles of scattered electrons are measured to a precision of  $\sigma_{p_t}/p_t^2 \leq 0.003~GeV^{-1}$  and  $\sigma_{\Theta} \sim 1$  mrad. They also improve the  $e/\pi$  separation of the calorimeter by providing electron identification by means of ionisation loss (dE/dx) measurement and detection of transition radiation.

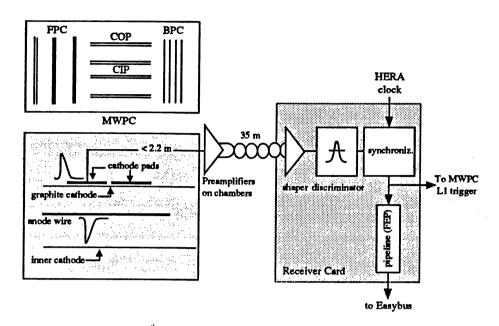

The system of MWPCs is used for fast timing and to provide prompt track information for building customized ray triggers. It is the only large solid angle subdetector which has a charge collection time shorter than the 96 ns interval between beam crossings. The chambers provide for each event a precise determination of the interaction time  $t_{\theta}$ . They have a two dimensional pad readout and consequently provide genuine space points of the charged particle tracks which are used to define rough trajectories. The dimension of the pads along the beam axis and the circumferential segmentation have been optimized to ensure a vertex

Figure 1.6: The H1 tracking system

resolution along the beam of 5 cm and to allow coincidences between the MWPC rays and the corresponding calorimeter signals. The use of the MWPCs in the trigger system is described in chapter 2.

The backward region is covered by an additional MWPC (BPC) with 4 wire planes rotated by 45° with respect to one another. The wire readout of this chamber provides one space point per track up to angles of  $\Theta = 175^{\circ}$ . This information is used to measure, with the central inner track detectors, the  $\Theta$ -coordinate of particle tracks hitting the backward electromagnetic calorimeter, e.g. electrons from low x neutral current events, and for  $e/\gamma$  separation in the BEMC.

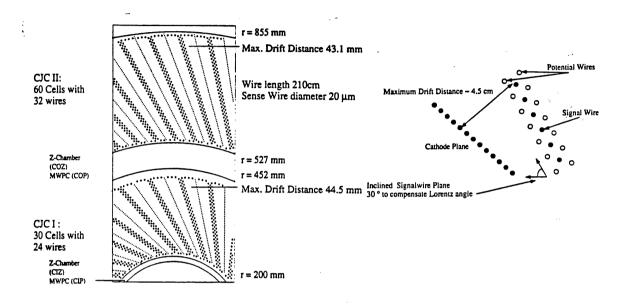

#### 1.4.2.2 Central Tracker

The central tracker is based on two jet chambers (CJC1 and CJC2) that provide for charged particles an accurate measurement of the  $r\phi$ -coordinates ( $\sigma_{r\phi}=210~\mu\mathrm{m}$ ) and a moderate measurement of the z-position ( $\sigma_z\sim25~mm$ ). The CJC detectors [10] are cylindrical drift volumes centered around the beam pipe with the wires running parallel to the beam axis. They are divided respectively in 30 and 60 jet cells separated by planes of cathode wires (fig. 1.7). Each cell consists of 24/32 sense wires alternating with two potential wires. The maximum drift distance is 44.5 mm which results in a drift time of about 1.2  $\mu$ s, assuming a drift velocity of 40  $\mu$ m/ns. The jet cells are tilted by  $\pm$  30° with respect to the radial direction in order to compensate the deflection of the electron drift trajectory in the magnetic field of 1.2 T. As a consequence, the secondary electrons drift approximately perpendicular to the high momentum tracks so that the resolution is

optimized. Another advantage is that all tracks above a minimum transverse momentum ( $\geq 100~{\rm MeV/c}$ ) traverse at least one sense wire plane which means that at least one drift time is shorter than 96 ns. This allows a separation of tracks coming from different bunch crossings and the use of the drift chamber information in a fast trigger logic.

Figure 1.7: Central tracker, section perpendicular to the beam with details of the CJC cell structure

All sense wires of the CJCs are read out independently on both sides by a chain of preamplifiers and analog-to-digital converters (see 2.5.3). On average 56 space points are measured on a track over a length of  $\sim$  650 mm. The total number of channels is 5280.

A precise determination of the z-coordinate is obtained from two z-drift chambers located at radii of 200 mm (CIZ) and 470 mm (COZ). These chambers [11], [12] are made of rings along the z-axis divided axially into rectangular drift cells. In each ring there are four layers of sense wires alternating with guard wires which are strung around the circumference of the chamber. In the cells, the electrons drift along the z-axis in the electric field produced by a series of cathode strips. The drift lengths are confined to 5.9 cm (CIZ) and 4.5 cm (COZ) which limit the drift time to about 1-2  $\mu$ s. Both sense wire ends are read out providing a  $\phi$ -measurement via charge division, in addition to the z-position from the driftime measurement. An accuracy of 250  $\mu$ m (CIZ) and 340  $\mu$ m (COZ) is achieved on the z-coordinate.

The z-drift chambers are mechanically linked to the central MWPCs. The part of the CTD which lies closest to the beam contains the inner proportional chamber (CIP) whereas the outer chamber (COP) is situated between COZ and CJC2. Both detectors consist of two layers of multiwire chamber formed by three self-supporting cylinders made of a sandwich of Kapton/Aluminium foils and Rohacell foam. The anode wires are strung along the beam axis. They are not readout. In each chamber, one of the cathodes is divided into rectangular strips (pads) with a regular segmentation in  $\phi$  and z. The readout of the charges induced on these strips provides space points which are used to define the direction of the tracks. Both detectors have a charge collection time below the bunch crossing time and provide an independent determination of the bunch crossing at which an event occurred.

The construction of the CIP and COP chambers are very similar. The COP detector, developed by the IIHE, is described in the next section. A detailed description of CIP can be found in [13].

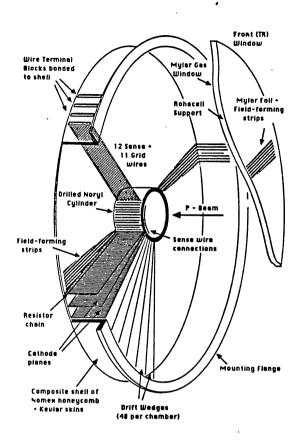

#### 1.4.2.3 Forward Tracker

The radial chambers [14] form the core of the FTD. They have been designed to provide an accurate measurement of the track space point  $\phi$ -coordinate as well as an electron identification by means of transition radiation detection. Each chamber consists of 48 wedges with 12 sense wires and segmented cathodes radiating outwards from the beam pipe (see figure 1.8). The cathode potential varies linearly with radius so that the electric drift field is uniform and perpendicular to the wire planes. An array of field-forming electrodes closes the electrostatic field cage on the faces of the chamber. As a result of the radial geometry, the drift cell is smallest near the beam pipe tending to compensate the increase in particle rate. Each sense wire is connected at the inner radius to its partner 105° away in  $\phi$ . At the outer circumference, both wire ends are amplified and recorded by a readout chain. An accuracy of 110-150  $\mu$ m on the drift distance and a charge division resolution of about 2 cm are achieved.

Electron identification is obtained from the analysis of the ionization energy deposition due to both the charged particle and radiation photons from the radiator immediately upstream. This latter consists of 400 polypropylene foils of 19  $\mu$ m kept in Xe at an average distance of 230  $\mu$ m. When a particle crosses the boundaries between the foils and the gas gaps, radiations in the X-ray region is emitted with an intensity proportional to the Lorentz factor  $\gamma = E/mc^2$  of the particle [15]. Consequently, electrons and pions of same energy can be distinguished by integrating the charge deposition on the sense wires. At high momentum ( $\sim$  60 GeV/c), a pion contamination of 8% is obtained for 90% electron efficiency. This identification is further enhanced at lower momenta by the multiple sampling over the 12

Figure 1.8: Schematic blowup of a radial wire drift chamber

sense wires, resulting at 5 GeV/c in a pion contamination of  $\sim 5\%$  [16].

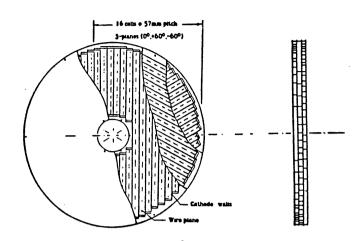

With the radial wire configuration, the polar angle  $\Theta$  is obtained by charge division with a moderate accuracy. To ensure a  $\Theta$  resolution of < 1 mrad, planar chambers have been incorporated into the FTD. They also help for the extrapolation of track segments from the radial chambers, especially in certain pathological cases, e.g. particles which fall within the double hit resolution of the radial drift cells. A planar module consists of 3 planes of parallel wires orientated at  $60^{\circ}$  relative to each other (see figure 1.9). Each of the three planes has a depth of 4 sense wires and consists of a set of drift cells which are rectangular in shape. With this geometry, the spatial resolution is homogeneous in x and y, hence giving accurate measurement of  $\Theta$ . Furthermore, particles which fall within the double hit resolution of one plane are resolved by subsequent planes with a rotated orientation.

Each forward tracker supermodule contains a multiwire proportional chamber consisting of two adjacent wire planes transverse to the beam and interleaved with 3 cathode planes. The sensitive region is from r=165 mm to r=750 mm and covers the full  $2\pi$  in  $\phi$ . This leads to an angular acceptance of  $6.5^{\circ} < \Theta < 18^{\circ}$ .

A wire plane is made of gold plated tungsten wires with a 20  $\mu m$  diameter

Figure 1.9: Planar drift chambers of the FTD

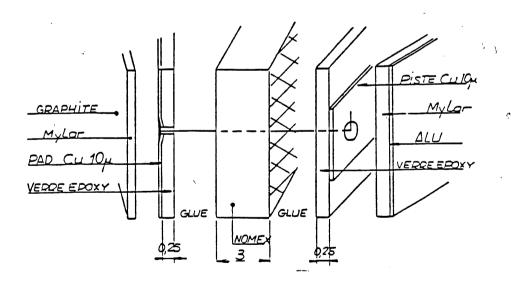

and spaced every 2 mm. The cathodes are supported on a rigid frame to ensure the flatness and a constant gap of 4 mm between the wire and cathode planes. They consist of a mylar foil, coated with a resistive graphite paint on the side adjacent to the wire plane, and attached to a epoxy board with Cu pads (see figure 1.10). These pads have a ring shape with a segmentation in r and  $\phi$  as

Figure 1.10: View of the cathodes of the forward MWPC

shown in figure 1.11. There are 192 pads on each cathode leading to 1152 channels for the 6 MWPC layers. The pads of two adjacent chambers are staggered in r and  $\phi$  so that the logical granularity is 4 times the physical granularity. They are read out via wires connected through a 2 mm rigid nomex foil and microstrip lines, edged on a fiber-glass epoxy board, to the preamplifiers. An aluminised

Figure 1.11: Arrangement of pads in the forward MWPC

mylar foil connected to ground is stretched behind the cathode planes to provide an electromagnetic shielding.

#### 1.4.2.4 Backward MWPC

The backward MWPC (BPC) is inserted between the central tracker and the BEMC. Its sensitive region is from z=-1393 cm to z=-1425 cm and r=15 to 65 cm. It covers the angular range  $155^{\circ} < \Theta < 175^{\circ}$ . The chamber is made of 4 anode wire planes transverse to the beam and oriented at  $45^{\circ}$  relative to each other. The wires are stretched with a spacing of 2.5 mm between two G10 fiber-glass epoxy rings which ensure a gap distance of 4 mm. Each chamber is closed by two circular G10 plates which provide the mechanical stability and the gas tightness. Only the wires are readout with two wires connected to one preamplifier, resulting in an angular resolution of  $\sim 1.0$  mrad.

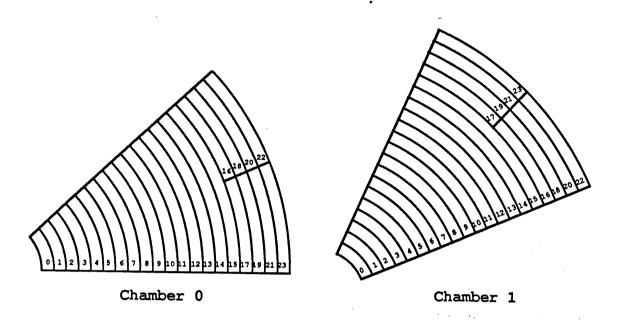

#### 1.4.3 The Outer Proportional Chambers (COP)

The design of the COP detector has been governed by the limited clearance (35 mm) available between the COZ and CJC2 detectors and by the requirement to reduce to a minimum the amount of material around the interaction region. The detector has an active length of 2172 mm with the inner wire plane at a radius of 501.5 mm and the outer at 514.5 mm, corresponding to an angular acceptance of  $25^{\circ} < \Theta < 165^{\circ}$ . The other salient parameters of COP are summarized in

table 1.3.

| COP parameters             | Inner   | Outer   | Unit                   |

|----------------------------|---------|---------|------------------------|

|                            | chamber | chamber |                        |

| Total length               | 2 3     | 861     | mm                     |

| Sensitive length           | 2 1     | .72     | mm                     |

| Radius of anode plane      | 501.5   | 514.5   | $\mathbf{m}\mathbf{m}$ |

| Anode - cathode gap        | 4       | 1       | mm                     |

| Anode plane :              |         |         |                        |

| number of wires            | 1 575   | 1 616   |                        |

| wire spacing               | 2       |         | mm                     |

| wire diameter              | 20      |         | $\mu$ m                |

| Cathode pads :             |         |         |                        |

| number of $\phi$ -segments | 16      |         |                        |

| number of z-segments       | 18      |         |                        |

| Size                       | 12 >    | < 20    | cm²                    |

Table 1.3: Dimensions and other specification of COP.

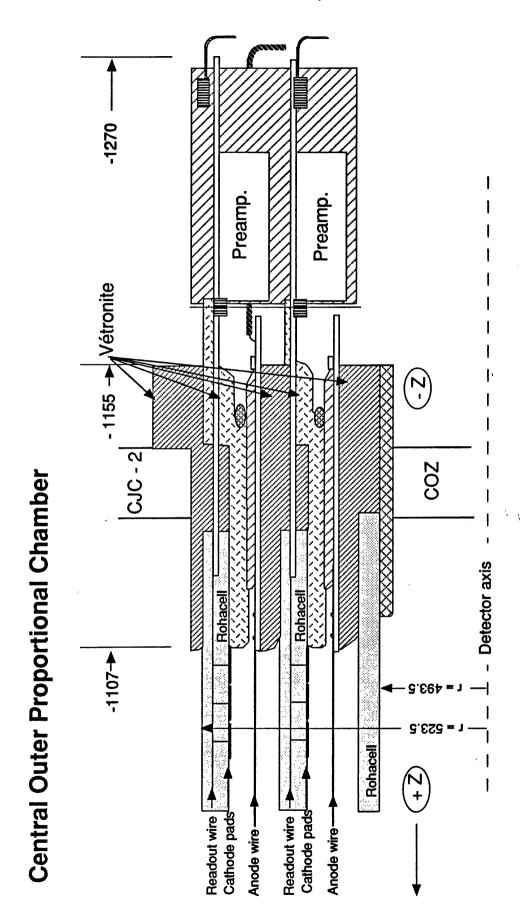

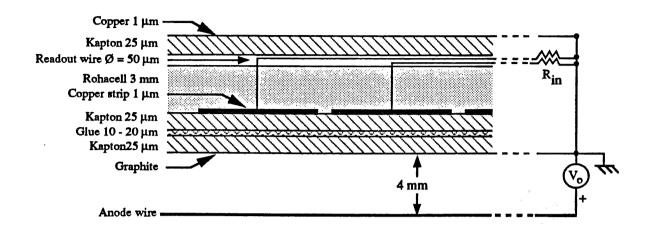

The COP chambers are made of three concentric kapton<sup>1</sup>/ rohacell<sup>2</sup>/aluminium sandwich cylinders which have been assembled on steel mandrels (see figure 1.12). The inner most cylinder is made of a 4 mm thick rohacell sheet, laminated on both sides with 25  $\mu$ m thick aluminium foils. The inner Al foil provides an electromagnetic shielding against external perturbation whereas the outer serves as the inner cathode of the first chamber.

The middle cylinder forms the readout cathode of the inner chamber and supports the second detection layer. The readout cathode is made of a kapton foil,  $25~\mu\mathrm{m}$  thick, coated with a resistive graphite paint ( $200~\mathrm{k}\Omega/\Box$ ) on the side adjacent to the inner wire plane. The outer surface is glued to a second kapton foil carrying the readout pads. These latter consist of  $12\times20~\mathrm{cm}^2$  strips edged on a 1  $\mu\mathrm{m}$  copper layer evaporated on the kapton, and oriented perpendicular to the cylinder axis. In total, the cathode is divided into 16 azimuthal and 18 longitudinal sectors.

The 288 pads are connected with 50  $\mu$ m diameter copper wires, of up to 2100 mm long, to readout printed circuit boards mounted on the end structure of the chamber. These readout wires are connected to the pads with conductive glue through a 3 mm rohacell layer which carries the wires into grooves cut on its outer surface. A Cu-coated kapton foil, glued on the rohacell, completes the readout cathode. Together with the copper wires, the foil forms a wave guide

<sup>&</sup>lt;sup>1</sup>Kapton is a polyimide film.

<sup>&</sup>lt;sup>2</sup>Rohacell is a rigid foam of polymethacrylimide.

Figure 1.12: Cross section of the COP end structure.

24

for the signal with a characteristic impedance matched to the input stage of the preamplifier. The middle cylinder is completed by the inner cathode of the outer chamber made of a 2 mm thick rohacell layer laminated with an aluminium foil on the external surface. The stucture of the outer most cylinder is similar to this.

The three cylinders are supported at both ends by glass-fiber epoxy rings which ensure a 8 mm chamber gap height and the gas tightness. Intermediate flanges support the PCBs on which the anode wires and the high voltage connections are soldered. The 20  $\mu$ m gold plated tungsten anode wires are strung parallel to the chamber axis with a tension of 60 g and a spacing of 2 mm. To ensure electrostatic stability, the wires are supported by two spacers. The flanges on the -z side also support the readout electronics and the gas distribution system.

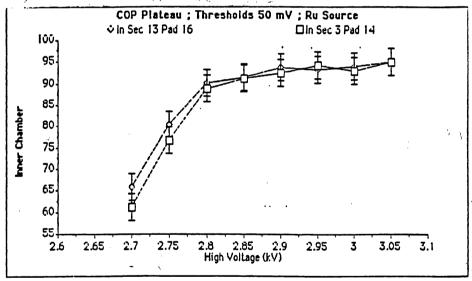

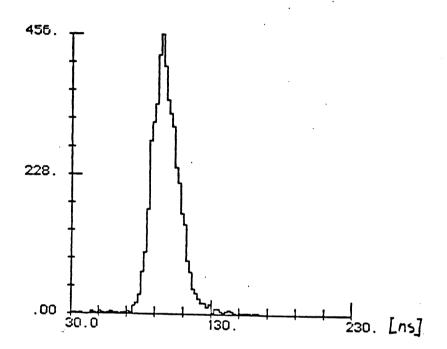

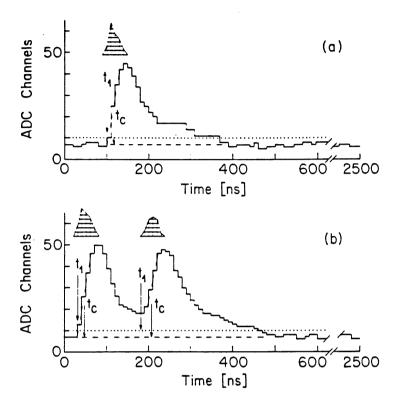

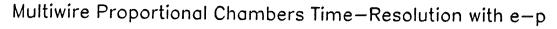

The chamber operates with a gas mixture of 49.9% Ar + 49.9%  $C_2H_6 + 0.2\%$  Freon. Using this gas, a high voltage plateau ranging from 2.9 to 3.05 kV is obtained (see figure 1.13). At 3.0 kV, a charge collection time of  $\leq 60$  ns has been measured which allows to use the COP detector for  $t_0$  determination (see figure 1.14).

Figure 1.13: COP HV plateau curve.

Figure 1.14: Time resolution measured with the COP detector

## Chapter 2

## The H1 Data Acquisition System

### 2.1 Introduction

The current high energy physics environment is characterized by the exploitation of relatively high luminosity ( $\sim 10^{30}-10^{32}~cm^{-2}s^{-1}$ ) colliders surrounded at the interaction points by large size general purpose detectors. The latter are designed to include a complex arrangement of detector components which cover, as closely as is practicable, the complete solid angle. To permit a precise reconstruction of the physics processes that occur during the collisions, the signals from the detectors must be amplified, eventually shaped, and digitised to extract the desired information, such as the pulse amplitude. This information must then be processed to suppress uninteresting data, to apply calibration corrections, and to format the data to comply with the off-line data structure conventions. The data volumes thus generated are finally assembled and recorded on high capacity storage devices, such as disks and cartridge tapes, for subsequent off-line analysis.

One of the characteristics of large experiments is the utilisation of many types of detectors (calorimeter, drift chambers . . . ). Each has specific properties and requires a particular approach for signal processing. Consequently, each sub-detector is connected at the bottom of the readout chain to dedicated analogue and digital "front-end" electronics, specially designed to process the signals from this apparatus. The data blocks formatted by the different front-end systems are collected centrally by the "Central Data Acquisition (CDAQ)" system which is responsible for coordinating the overall readout chain and for transferring the full event records to the data store. To maximise the effective use of the experiment run time, these two consecutive readout layers, front-end and CDAQ, must operate under minimum dead time conditions.

The complexity of the detectors and their associated electronic systems require a continuous monitoring of the quality of the data being recorded. For this purpose, various monitoring systems are connected along the readout chain. Their function is to check regularly the apparatus performance and to detect possible faults in the readout procedure by continuously analysing data samples on-line. As this level, a major concern is the human interface. Facilities, such as event and histogram displays, interactive menus, must be provided to allow any user to monitor the operation of the apparatus and check the running conditions.

In addition to the event processing related tasks, other important functions for the management of the experiment are assigned to the data acquisition system: the setting-up, calibration and test procedures, the control and recording of the critical detector parameters (high voltages, gas flows, temperatures ...), the communication with the off-site systems etc ...

This chapter gives an overview of the H1 data acquisition system and describes the general structure of the system hardware. In section 2.2, we review the environment which has conditioned the readout architecture. The trigger system is described in section 2.3. Sections 2.4 and 2.5 present in more detail the data acquisition system: the consecutive steps of the acquisition procedure and the description of its hardware implementation.

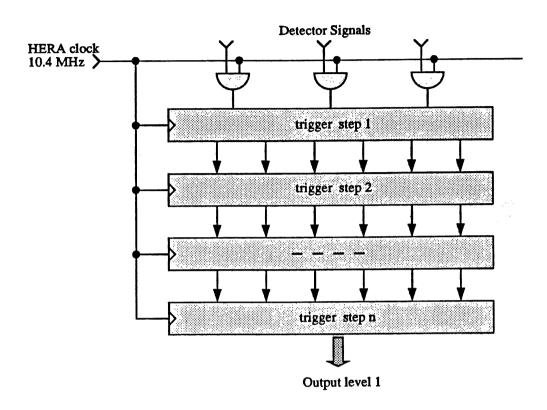

## 2.2 Basic Design Features