# Ein Teststand für die Ausleseelektronik des H1–Myon–Systems

von

Simone Baer

Diplomarbeit in Physik

vorgelegt der

Mathematisch-Naturwissenschaftlichen Fakultät der Rheinisch-Westfälischen Technischen Hochschule Aachen

im Juni 1997

angefertigt im I. Physikalischen Institut

# Inhaltsverzeichnis

| 1 | Einl           | leitung                               | 3  |

|---|----------------|---------------------------------------|----|

| 2 | HEI            | RA                                    | 5  |

| 3 | $\mathbf{Der}$ | H1-Detektor                           | 7  |

|   | 3.1            | Die Spurkammern                       | 7  |

|   | 3.2            | Die zentralen Kalorimeter             | 9  |

|   | 3.3            | Die supraleitende Spule               | 10 |

|   | 3.4            | Das Vorwärts-Myon-Spektrometer        | 10 |

|   | 3.5            | Das instrumentierte Eisen             | 11 |

|   | 3.6            | Der H1-Trigger                        | 11 |

|   | 3.7            | Luminositätsmessung                   | 13 |

| 4 | Das            | digitale Myon-System                  | 15 |

|   | 4.1            | 9                                     | 15 |

|   | 4.2            | Die Modulinstrumentierung             | 15 |

|   | 4.3            | 9                                     | 19 |

|   |                |                                       | 20 |

|   |                | 4.3.2 Der ROC                         | 21 |

| 5 | Prü            | fverfahren für das Myon-System        | 25 |

|   | 5.1            | · · · · · · · · · · · · · · · · · · · | 25 |

|   | 5.2            | Der Teststand                         | 26 |

|   | 5.3            | Direkte Prüfverfahren                 | 28 |

|   |                |                                       | 28 |

|   |                |                                       | 33 |

|   | 5.4            |                                       | 39 |

|   | 5.5            |                                       | 40 |

|   |                | 5.5.1 Die Signalerfassung             | 40 |

|   |                |                                       | 41 |

|   |                |                                       | 43 |

|   |                |                                       | 44 |

|   |                |                                       | 44 |

| 6             | Anleitung zu den Prüfverfahren          | 47        |

|---------------|-----------------------------------------|-----------|

|               | 6.1 Untersuchung des ROC im Myon–System | 47        |

|               | 6.2 Untersuchung des ROC im Teststand   | 51        |

| 7             | Zusammenfassung                         | <b>55</b> |

| $\mathbf{A}$  | Zyklus des Mode Controllers             | 57        |

| В             | Die Register des ROD                    | 61        |

| $\mathbf{C}$  | Die Register des ROC                    | 63        |

| D             | Zyklus des Test Controllers             | 67        |

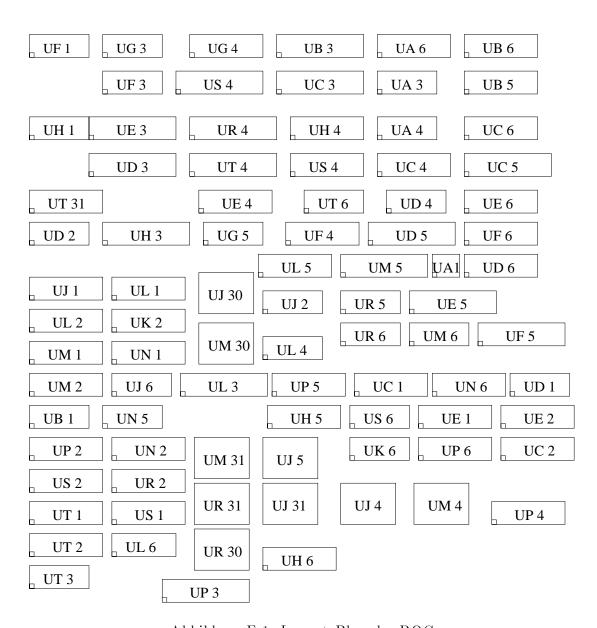

| $\mathbf{E}$  | Layout des ROC                          | 69        |

| $\mathbf{A}$  | bbildungsverzeichnis                    | 71        |

| Ta            | abellenverzeichnis                      | 73        |

| $\mathbf{Li}$ | teraturverzeichnis                      | <b>75</b> |

| D             | anksagung                               | 77        |

| Le            | ebenslauf                               | 79        |

## Kapitel 1

# **Einleitung**

In den Experimenten der Hochenergiephysik werden die elementaren Bausteine der Materie und ihre Wechselwirkungen erforscht. Nach dem heutigen Verständnis werden die elektromagnetische, die schwache und die starke Wechselwirkung im sogenannten Standardmodell der Elementarteilchenphysik zusammengefaßt. Die Grundbausteine der Materie, die Fermionen, sind Spin 1/2 Teilchen. Sie bilden zwei Teilchenfamilien, die Leptonen und die Quarks, mit jeweils drei Generationen.

Leptonen:

$$\begin{pmatrix} \nu_e \\ e^- \end{pmatrix} , \begin{pmatrix} \nu_\mu \\ \mu^- \end{pmatrix} , \begin{pmatrix} \nu_\tau \\ \tau^- \end{pmatrix}$$

Quarks:

$$\begin{pmatrix} u \\ d \end{pmatrix}$$

,  $\begin{pmatrix} c \\ s \end{pmatrix}$  ,  $\begin{pmatrix} t \\ b \end{pmatrix}$

Zu jedem Lepton und Quark existiert ein entsprechendes Antiteilchen. Die Quarks tragen drittelzahlige Ladungen. Je Zwei (Mesonen) oder Drei (Baryonen) von ihnen setzen sich zu Hadronen ("schwere Teilchen") zusammen. Die Wechselwirkungen zwischen den Konstituenten werden durch den Austausch von Spin 1 Teilchen, den Bosonen, beschrieben. Tabelle 1.1 gibt eine Zusammenfassung der Austauschteilchen mit ihren Massen und den dazugehörenden Wechselwirkungen.

Einer der größten Erfolge des Standardmodells waren die Vorhersagen des W<sup>±</sup>-Bosons, mit einer Masse von  $\sim 80$  GeV, und des Z<sup>0</sup>-Bosons, mit einer Masse von  $\sim 91$  GeV, die experimentell sehr gut bestätigt wurden (M<sub>W</sub><sup>±</sup> = 80.1 ± 0.4 GeV, M<sub>Z</sub><sup>0</sup> = 91.188 ± 0.007 GeV [1]). Trotz der großen Erfolge des Standardmodells bleiben einige Fragen offen, so z.B. warum es drei Generationen von Leptonen und Quarks gibt, oder warum es eine so große Anzahl freier Parameter gibt, zu denen unter anderem auch die Massen der Fermionen zählen.

| Austauschteilchen | Wechselwirkung         | Masse [GeV]        |

|-------------------|------------------------|--------------------|

| $\gamma$          | elektromagnetisch      | 0                  |

| $Z^0$             | schwach                | $91.187 \pm 0.007$ |

| $W^{\pm}$         | schwach                | $80.1 \pm 0.4$     |

| g <sub>1,,8</sub> | $\operatorname{stark}$ | 0                  |

Tabelle 1.1: Die Austauschteilchen der Wechselwirkungen [1]

Zur weiteren Überprüfung der Theorie ist es deshalb notwendig, die Struktur der Materie bei immer kleineren Längenskalen zu untersuchen. Das ist am besten in Beschleunigerexperimenten mit hohen Schwerpunktsenergien zu realisieren. An HERA¹ werden Elektronen an Protonen mit bisher unerreichten Impulsüberträgen und Schwerpunktsenergien gestreut. H1 ist ein universeller Detektor zur Untersuchung der Streuung und zur Ausmessung komplizierter Topologien des Endzustandes. Der Detektor besteht aus unterschiedlichen Komponenten (siehe Kapitel 3), eine davon ist das instrumentierte Eisen, das zum Nachweis von Hadronen und Myonen dient.

Das Ziel der vorliegenden Arbeit ist es, Diagnosemethoden für die Ausleseelektronik des H1 Myon-Systems zu entwickeln, um schnell und ohne Expertenwissen Fehler finden und beheben zu können. Im zweiten und dritten Kapitel wird kurz auf den Speicherring HERA und den H1-Detektor eingegangen. Nachfolgend wird das Myon-System mit seiner Ausleseelektronik beschrieben. In Kapitel fünf werden die unterschiedlichen Prüfverfahren und ihre Funktionsweisen vorgestellt. Kapitel sechs enthält die Anleitung zu den einzelnen Prüfverfahren.

$<sup>^{1}\</sup>underline{\mathbf{H}}\mathbf{adron} - \underline{\mathbf{E}}\mathbf{lektron} - \underline{\mathbf{R}}\mathbf{ing}\underline{\mathbf{A}}\mathbf{nlage}$

## Kapitel 2

## **HERA**

Zur Zeit ist die <u>H</u>adron-<u>E</u>lektron-<u>R</u>ing-<u>A</u>nlage HERA am Forschungszentrum DESY<sup>1</sup> in Hamburg weltweit der einzige  $e^{\pm}p$  Speicherring.

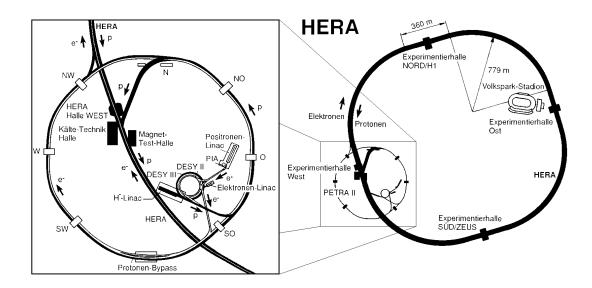

Hier werden Protonen mit einer Energie von 820 GeV mit Elektronen<sup>2</sup> der Energie von etwa 30 GeV zur Kollision gebracht. Das alles geschieht in einem Tunnel, der in einer Tiefe von 10 bis 20 m unter der Erdoberfläche verläuft und einen Umfang von 6,3 km besitzt. Abbildung 2.1 zeigt schematisch die für das HERA-Experiment wichtigen Einrichtungen am DESY.

Bevor die Einspeisung der Elektronen und Protonen in den HERA-Speicherring erfolgt, werden sie über mehrere Stufen vorbeschleunigt. Die Elektronen werden mit 14 GeV und die Protonen mit 40 GeV in den Ring geleitet. Dort laufen sie in getrennten Hochvakuum-Röhren und werden auf ihre Endenergien beschleunigt, gespeichert und zur Kollision gebracht. Aus den Energien der beiden Strahlen ergibt sich eine Schwerpunktsenergie von  $\sqrt{s} \approx 300$  GeV.

Um sowohl die Elektronen als auch die Protonen auf der vorgegebenen Bahn im Tunnel zu halten, sind große Magnetfelder erforderlich. Diese sind durch den Radius des Rings und den Impuls der Teilchen bestimmt. Für die Protonen ergibt sich damit eine Feldstärke von 4.68 T. Diese wird durch supraleitende Magnete erreicht. Aufgrund ihres viel geringeren Impulses ist für die Elektronen ein Magnetfeld von 0.165 T ausreichend.

Die Teilchen selbst sind zu Paketen (Bunches) zusammengefaßt. Die Designwerte sind für Elektronen  $3.6 \times 10^{10}$  bzw. für Protonen  $10 \times 10^{10}$  Teilchen pro Paket; e<sup>-</sup>– und p–Strahlen können jeweils bis zu 210 Bunches enthalten. Die zeitliche Differenz zwischen zwei Paketen oder auch zwischen zwei Kollisionen<sup>3</sup> beträgt 96 ns. Daraus ergibt sich eine Frequenz von  $\approx 10.4$  MHz, die als internes Taktsignal

$<sup>^{1}\</sup>underline{\mathbf{D}}$ eutsches- $\underline{\mathbf{E}}$ lektronen-Synchrotron

<sup>&</sup>lt;sup>2</sup>Seit 1994 werden Positronen statt Elektronen benutzt. Für die vorliegende Arbeit spielt dies iedoch keine Rolle, so daß im Weiteren trotzdem der Begriff Elektronen verwendet wird.

<sup>&</sup>lt;sup>3</sup>Eine Kollision ist das sich Durchkreuzen zweier Pakete, "Bunchcrossing", im weiteren Verlauf mit BC abgekürzt

Abbildung 2.1: Der Speicherring HERA am DESY

dient, das im folgenden "HERA-Clock" genannt wird.

Am HERA-Tunnel gibt es vier Hallen für Experimente. In zwei dieser vier Wechselwirkungsbereiche werden die Strahlen zur Kollision gebracht. Für die Untersuchung der Reaktionsprodukte stehen in der Halle Nord der H1-Detektor und in der Halle Süd der ZEUS Detektor zur Verfügung. In den beiden anderen Hallen wird jeweils nur einer der beiden Teilchenstrahlen zu physikalischen Untersuchungen genutzt. In Halle Ost untersucht das Experiment HERMES die Streuung polarisierter Elektronen an einem Gastarget. In Halle West befindet sich das Experiment HERA-B noch in der Testphase. Es soll nach CP-Verletzung im  $B^0\overline{B^0}$ -System suchen. Es ist ein Fixed-Target-Experiment und entsteht durch Proton-Proton-Stöße.

Weitere Informationen zu diesem Kapitel sind in [2, 3, 4, 5] zu finden.

## Kapitel 3

## Der H1-Detektor

Der H1-Detektor ist ein  $4\pi$ -Detektor, der die bei den Elektron-Proton-Stößen enstehenden Reaktionsprodukte vermißt. Die für das H1-Experiment zuständige Kollaboration besteht aus ca. 400 Wissenschaftlern aus 12 Ländern.

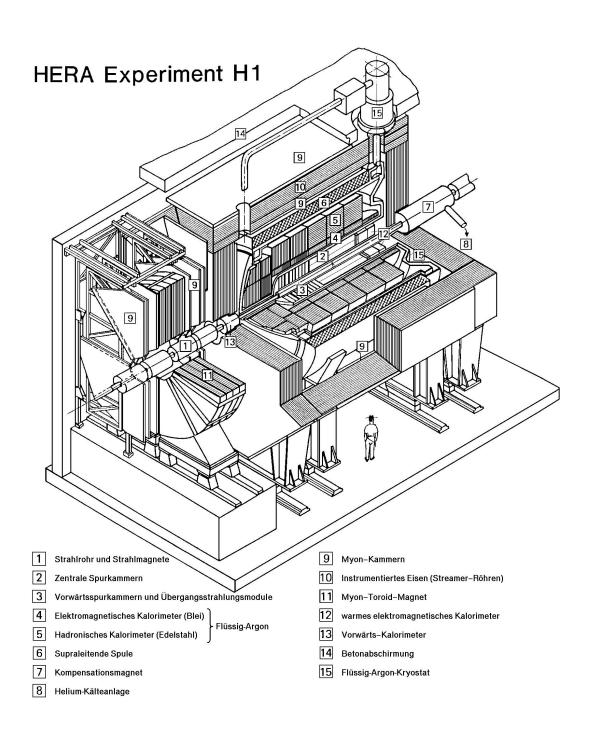

Die Abbildung 3.1 zeigt den H1 Detektor. Die einzelnen Komponenten können anhand der angegebenen Nummer nabgelesen werden. An dieser Stelle soll nur ein kleiner Überblick gegeben werden. Genaue Informationen sind in [2] und in den "Technical H1 Reports", die eine detaillierte Darstellung einzelner Detektorkomponenten beinhalten, zu finden.

Die Geometrie des Detektors ist so festgelegt, daß die z-Achse in Richtung der einlaufenden Protonen zeigt, die x-Achse zum Mittelpunkt von HERA, und die y-Achse senkrecht nach oben. Der Koordinatenursprung ist gleichzeitig der nominale Wechselwirkungspunkt<sup>1</sup>. In den meisten Fällen erfolgt die Beschreibung aber in Polarkoordinaten. Der Winkel  $\theta$  ist der Polarwinkel zur z-Achse. Durch die stark unterschiedliche Energie des e-Strahls zum p-Strahl bewegt sich das ep-Schwerpunktsystem im Vergleich zum Laborsystem mit einer Geschwindigkeit von  $\approx 0.9$  c in Protonrichtung. Daraus resultierend befinden sich über 50% der in den Reaktionen erzeugten Teilchen in einem Polarwinkelbereich von  $\theta \leq 25^{\circ}$ . Aus diesem Grund ist der Detektor asymmetrisch bezüglich der Kollisionsebene gebaut worden.

## 3.1 Die Spurkammern

Diese Detektorkomponente dient zum Nachweis von Spuren geladener Teilchen und zur Messung ihrer Impulse aus der Krümmung der Spuren. Das Spurkammer-System besteht aufgrund der Asymmetrie aus zwei großen Teilen, der zentralen Spurkammer und den Vorwärtsspurkammern.

<sup>&</sup>lt;sup>1</sup>Der tatsächliche Wechselwirkungspunkt wird im folgenden Vertex genannt

Abbildung 3.1: Der H1–Detektor

#### Zentrale Spurkammern

Die zentralen Spurkammern<sup>2</sup> 2 sind zylindrisch um den Wechselwirkungspunkt angeordnet. Nachfolgend sind die einzelnen Komponenten der zentralen Spurkammer, die das Strahlrohr 1 umschließen, von innen beginnend, aufgelistet:

- eine Vieldraht-Proportionalkammer (CIP, <u>C</u>entral <u>I</u>nner <u>P</u>roportional Chamber)

- eine innere z-Driftkammer (CIZ, Central Inner Z Chamber)

- eine innere Jetkammer (CJC1, Central Jet Chamber)

- eine äußere z-Driftkammer (COZ, Central Outer Z Chamber)

- eine äußere Proportionalkammer (COP, <u>C</u>entral <u>O</u>uter <u>P</u>roportional Chamber)

- eine äußere Jetkammer (CJC2, <u>C</u>entral <u>Jet C</u>hamber)

Die CIP und COP werden hauptsächlich für Triggerinformationen benötigt. Die CIZ und COZ vermessen die z-Koordinate der Spuren. Die Spurkammern CJC1 und CJC2 bestimmen die Teilchenspuren in der  $r-\phi$ -Ebene.

#### Vorwärtsspurkammern

Die Vorwärtsspurkammern<sup>3</sup> 3 sind aus drei "Supermodulen" aufgebaut. Ein Supermodul besteht aus drei planaren Driftkammern, die jeweils um  $60^{\circ}$  gegeneinander verdreht sind, einer Vieldraht–Proportionalkammer, mehreren Schichten Polyethylenfolie, um Übergangsstrahlung zu erzeugen, und einer radialen Driftkammer. Mit den planaren Kammern kann der Polarwinkel gemessen werden. Wie die CIP und COP werden die Vieldraht–Proportionalkammern in erster Linie für Triggerzwecke benötigt. Mit den radialen Kammern werden die Spuren in der r- $\phi$ -Ebene festgelegt und die durch die Folie entstehende Strahlung nachgewiesen.

## 3.2 Die zentralen Kalorimeter

Die Kalorimeter werden zur Energiemessung benötigt. Im folgenden sind die beiden Hauptkomponenten aufgeführt, das Flüssig-Argon-Kalorimeter und das Rückwärtige Kalorimeter.

<sup>&</sup>lt;sup>2</sup>Central Track Detector

$<sup>{}^{3}\</sup>underline{F}$ orward  $\underline{T}$ rack  $\underline{D}$ etector

#### Das Flüssig-Argon-Kalorimeter

Dieses Kalorimeter<sup>4</sup> [4] [5] liegt innerhalb der supraleitenden Spule. Es wird zur Energiemessung der Reaktionsprodukte benutzt und deckt einen Winkelbereich von  $4^{\circ} \leq \theta \leq 153^{\circ}$  ab.

Das Kalorimeter ist aus abwechselnden Schichten Absorbermaterial und Ionisationskammern aufgebaut und in zwei große Bereiche unterteilt. Der elektromagnetische Teil 4, für den Nachweis von Teilchen mit elektromagnetischer Wechselwirkung, besteht aus Blei, als Absorber, und flüssigem Argon, als zu ionisierendes Medium. Der die hadronische Wechselwirkung nachweisende Teil 5 besteht aus abwechselnden Schichten Edelstahl und Argon. Das gesamte Kalorimeter befindet sich in einem Kryostaten, der mit gekühltem, flüssigen Argon gefüllt ist.

#### Rückwärtiges Kalorimeter

Das LAr–Kalorimeter ist in Rückwärtsrichtung nicht geschlossen. Um den Winkelbereich zwischen  $151^{\circ} \leq \theta \leq 177^{\circ}$  abzudecken, befindet sich dort das Rückwärtige Kalorimeter<sup>5</sup> 12. Es ist aus in Blei eingelassenen szintillierenden Fasern aufgebaut, die parallel zur z–Achse verlaufen. In erster Linie dient es dazu, ein unter kleinen Winkel gestreutes Elektron nachzuweisen. Diese Detektorkomponente ist ein "Warmes Kalorimeter", da sie im Gegensatz zum LAr–Kalorimeter nicht mit flüssigen Gasen gekühlt wird.

## 3.3 Die supraleitende Spule

In der Mitte des Detektors herrscht ein nahezu homogenes Magnetfeld von 1.15 T, das durch die supraleitende Spule 6 erzeugt wird. Dieses Feld des Solenoidmagneten bewirkt eine Krümmung der Flugbahn geladener Teilchen. Aus dem Krümmungsradius und der Krümmungsrichtung können Impuls und Ladungsvorzeichen eines Teilchens bestimmt werden.

## 3.4 Das Vorwärts-Myon-Spektrometer

Mit dieser Detektorkomponente werden Impulse hochenergetischer Myonen in Vorwärtsrichtung in einem Polarwinkelbereich zwischen  $3^{\circ} \leq \theta \leq 17^{\circ}$  gemessen. Das Vorwärts-Myon-Spektrometer 11 besteht aus vier Driftkammern und einem Toroidmagneten. Je eine radiale und eine azimutale Kammer sind vor und hinter dem Magneten angebracht, der ein um die z-Achse toroidförmiges Magnetfeld erzeugt. Das Vorwärts-Myon-Spektrometer arbeitet vollkommen losgelöst vom zentralen Myon-System.

<sup>&</sup>lt;sup>4</sup>LAr, Liquid Argon Calorimeter

<sup>&</sup>lt;sup>5</sup>SpaCal, Spaghetti <u>Cal</u>orimeter

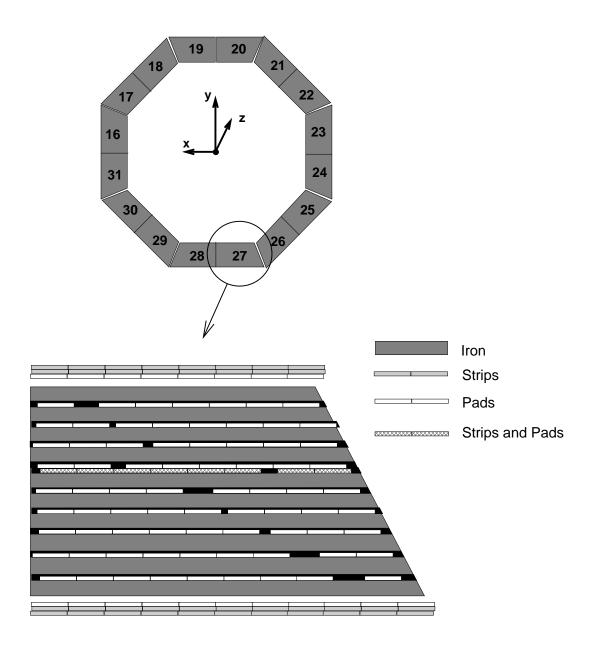

### 3.5 Das instrumentierte Eisen

Um die supraleitende Spule herum befindet sich ein Eisenjoch 10 zur Rückführung des magnetischen Flusses. Dieses Joch besteht aus 7.5 cm dicken Eisenplatten, die durch 2.5 cm breite Schlitze voneinander getrennt sind. In diese Schlitze sind Streamerrohrkammern 9 eingeschoben. Auf den Kammern sind noch weitere Ausleseelemente, "Strips" und "Pads", aufgebracht. Strips sind 17 mm breite Kupferstreifen, die einer besseren Ortsauflösung dienen. Mit den Streamerrohrkammern und den Strips werden hauptsächlich Myonen detektiert. Im Gegensatz zu den Pads werden sowohl die Streamerrohrkammern als auch die Strips digital ausgelesen.

Pads sind quadratische (30cm x 30cm) und rechteckige (40cm x 50cm) Influenzelektroden die der Energiemessung bis  $\approx 30$  GeV dienen und analog ausgelesen werden. Über diese Pads werden in erster Linie Hadronen nachgewiesen, die nicht vollständig im Kalorimeter absorbiert worden sind.

Eine ausführlichere Beschreibung des instrumentierten Eisens ist in Kapitel 4 gegeben.

## 3.6 Der H1-Trigger

Alle 96 ns kollidieren Elektron- und Protonpakete miteinander. Ein Trigger hat die Aufgabe, aus all diesen Zusammenstößen die physikalisch interessanten Wechselwirkungen herauszufiltern, die dann abgespeichert werden. Bei H1 gibt es vier hierarchisch geordnete Triggerstufen ("Level"). L1 ist die erste Triggerstufe, L4 die letzte. Die Entscheidungen der ersten beiden Level werden nur von der Hardware getroffen. Je weiter eine Triggerentscheidung vorangeschritten ist, desto mehr Informationen über ein Ereignis stehen zur Verfügung und umso länger ist die Auswahlzeit.

Auf der ersten Triggerstufe kann es nur eine positive Entscheidung geben, in dem Sinne, daß die Daten weiterverarbeitet werden sollen ("L1 keep"). Alle bis zu diesem Zeitpunkt der Entscheidung nachfolgenden Daten werden zwischengespeichert. Sobald das Signal "L1 keep" gesendet wurde, ist eine Aufzeichnung weiterer Ereignisse nicht mehr möglich. Die nun folgende Auswahlzeit, bis eine endgültige Entscheidung über die Daten getroffen wurde, ist die sogenannte Totzeit.

L1 Der Speicher, in den die während dieser Zeit stattgefundenen Ereignisse geschrieben werden, besteht aus "Front-End-Pipelines". Die Daten werden an den Anfang der Pipelines geschrieben und mit jedem weiteren BC um eine Stelle in den Pipelines weitergeschoben.

Die Entscheidung, ob ein Ereignis die nächste Triggerstufe erreicht, dauert 2.3  $\mu$ s, das sind 24 BC. Dadurch befindet sich das zu einem Trigger gehörende Ereignis grundsätzlich an denselben Stellen in den Pipelines.

Diese können, abhängig vom jeweiligen Subdetektor, die Information von 27 bis zu 35 BC speichern.

Während der Datennahme sind die Pipelines "Enabled", d.h. Daten können in die Pipelines geschrieben und weitergeschoben werden. Ist ein Trigger ausgelöst worden ("L1 keep"), werden die Pipelines "Disabled", das bedeutet, daß sie kein Taktsignal mehr erhalten und es können keine neuen Daten in die Pipelines geschrieben werden. Dieser Zustand hält solange an, bis eine endgültige Entscheidung des Triggers getroffen wurde, d.h. der Zustand kann sich über alle vier möglichen Triggerstufen erstrecken. Der Teil der Auswahlzeit, während der keine neuen Daten genommen werden können, heißt "Totzeit".

Eine ausführliche Beschreibung der ersten Triggerstufe ist in [7] gegeben.

L2 Mit Anliegen des Signals "L1 keep" ( = die Daten sollen weiterverarbeitet werden) beginnt die zweite Triggerstufe, L2, die nächsthöhere Entscheidung über die zu L1 gehörenden Daten zu treffen.

Die Daten werden über die Auslesesoftware aus den Pipelines geschoben und weiterverarbeitet, dabei gehen die anderen zwischenzeitlich gespeicherten Daten verloren. Der gesamte Vorgang bis zu der Triggerentscheidung "L2 keep" dauert 20µs. Im Falle eines "L2 reject" werden die Daten verworfen und die Signale "FastClear" und Pipeline Enable (PEn) gesendet. Die noch in den Pipelines vorhandenen Daten werden durch eine Wartezeit von ca. 32 BC quasi gelöscht und die Pipelines für neue Daten freigegeben.

L3, L4 Bei Vorliegen eines "L2 keep"- bzw. "L3 keep"-Signals werden die nachfolgenden Triggerstufen angesprochen. In der dritten Ebene beträgt die Auswahlzeit ca. 800μs. Die Entscheidungen von L3 und L4 sind reine Software-Entscheidungen. Auf der letzten Stufe, L4, werden schon Teile der Daten rekonstruiert. Hier liegt die Auswahlzeit im ms Bereich.

Bei H1 gibt es auf der ersten Stufe neun unterschiedliche Subdetektor-Triggersysteme. Die einzelnen Triggerentscheidungen laufen in der zentralen Triggerlogik<sup>6</sup> zusammen und werden dort zeitlich synchronisiert. Die Triggerentscheidungen von verschiedenen Detektorkomponenten werden zu einem Subtrigger zusammengefaßt. Wenn für einen Subtrigger alle Bedingungen erfüllt sind, wird das Signal "L1 keep" ausgelöst. Haben dann die zu diesem Trigger gehörenden Daten alle Entscheidungsstufen erfolgreich durchlaufen, wird das Ereignis auf Magnetband permanent gespeichert.

$<sup>^6</sup>$ CTL,  $\underline{C}$ entral  $\underline{T}$ rigger  $\underline{L}$ ogic

## 3.7 Luminositätsmessung

Die Luminosität  $\mathcal{L}$  ist eine Größe, die in Beschleuniger Experimenten durch die Anzahl der Teilchenpakete  $n_1$  und  $n_2$ , die Durchdringungsfläche der beiden Pakete A und die Zahl der umlaufenden Pakete pro Zeiteinheit f gegeben ist [6].

$$\mathcal{L} = n_1 \cdot n_2 \cdot f/A$$

Da A nicht genau bestimmt werden kann, muß die Luminosität gemessen werden. Am besten eignet sich dazu ein Prozeß, der theoretisch und experimentell gut bekannt ist, einen niedrigen Untergrund hat und leicht nachzuweisen ist. Bei H1 wird der Bethe-Heitler-Prozeß benutzt. Dieser Prozeß beschreibt die Bremsstrahlung beschleunigter Ladung in Vorwärtsrichtung. Die Anzahl der Ereignisse N wird gezählt. Die integrierte Luminosität ergibt sich durch Division mit dem Wirkungsquerschnitt  $\sigma_{Prozeß}$ .

$$\int \mathcal{L} \, dt = \frac{N}{\sigma_{Prozeß}}$$

Weitere Informationen zu diesem Kapitel sind in [2, 18, 19, 20, 21, 23, 29] zu finden.

## Kapitel 4

# Das digitale Myon–System

### 4.1 Aufbau

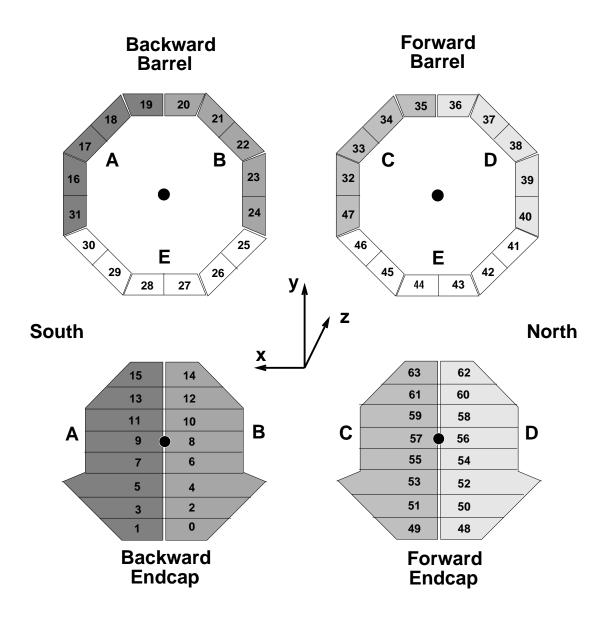

Das Eisenjoch ist zylindersymmetrisch zur z-Achse aufgebaut. Das im oberen Teil der Abbildung 4.1 gezeigte Oktagon ist in zwei "Barrelhälften" unterteilt, das Rückwärts-Barrel und das Vorwärts-Barrel. Das gesamte Barrel ist durch zwei senkrecht zur z-Achse stehende Eisenwände, die "Endkappen", abgeschlossen. Die Endkappen, wie auch die Barrelhälften, sind mit Schlitzen versehen, in die Streamerrohrkammern eingeschoben sind.

Die Endkappen und Barrelhälften ihrerseits sind wieder in je 16 Einheiten unterteilt, die Module. In dem instrumentierten Eisen befinden sich 10 Lagen von Streamerrohrkammern in den dafür vorgesehenen Schlitzen. Außerhalb und innerhalb des Eisens sind nochmaljeweils drei Lagen von Straemerrohrkammern angebracht (siehe Abbildung 4.2). Damit stehen insgesamt 16 Lagen zur Verfügung.

## 4.2 Die Modulinstrumentierung

Die Daten einer Lage werden über einen Bus-Kabel an die Ausleseelektronik weitergeleitet. Die Maximalzahl auszulesender Kanäle je Lage ist durch die Ausleseelektronik auf 256 begrenzt. Ein Kanal bezeichnet den Draht einer Streamerrohrkammer oder einen Kupferstreifen. Ist die Anzahl der Kanäle in einer Lage größer als 256, werden die Kanäle auf zwei Busse aufgeteilt. Insgesamt werden die Daten der 16 Lagen über 24 Bus-Leitungen weitergegeben.

Ein Modul ist durch die Bus-Leitungen in 24 Ebenen aufteilbar, die ersten 16 Leitungen repräsentieren die Draht-Ebenen, die restlichen acht die Strip-Ebenen. Durch die Strips wird die endgültige Ortsauflösung erhalten, da sie senkrecht zur Drahtrichtung aufgebracht sind. Ohne die Strips wären lediglich die x- und die y-Koordinate bekannt. Mit den Strips kann die letzte, die z-Koordinate eines

<sup>&</sup>lt;sup>1</sup> "Barrel" aufgrund seines tonnenförmigen Aussehens

Abbildung 4.1: Modul-Unterteilung des Eisenjochs [24]

Abbildung 4.2: Verteilung der Ausleseelemente im Eisen [24]

Teilchendurchgangs bestimmt werden. Insgesamt besitzt das Myon-System etwa 132.000 Kanäle.

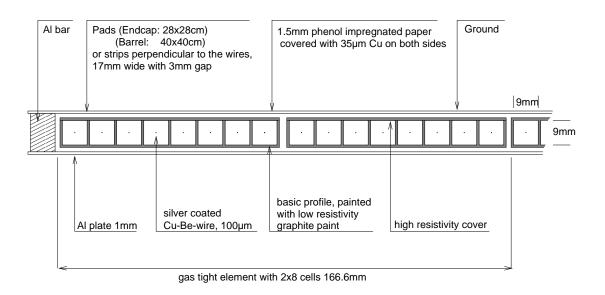

#### Der Kammeraufbau

Die kleinste Einheit ist eine Kammer mit einem Querschnitt von  $9 \times 9$  mm. In deren Mitte befindet sich ein  $100~\mu\mathrm{m}$  dicker versilberter Draht aus Cu–Be. Jeweils acht Drähte sind zu einem Profil zusammengefaßt. Die einzelnen Drähte sind untereinander durch graphitierte Stege getrennt. Zwei Profile sind zu einem Element in einer gasdichten Kunststoffbox (Luranyl) zusammengeschweißt. Die Kammern sind mit einem Gasgemisch aus  $\mathrm{CO}_2$ , Isobutan und Argon gefüllt, im Verhältnis 88:9.5:2.5. Abbildung 4.3 zeigt einen Querschnitt durch ein Element.

redrawn by Heiko Itterbeck

Abbildung 4.3: Querschnitt durch ein Element [24]

#### Der Signal-Mechanismus

Durchquert ein geladenes Teilchen eine Streamerkammer, ionisiert es die Gasatome in der Kammer. Durch die am Draht angelegte Hochspannung werden die freien Elektronen so stark beschleunigt, daß ihre Energie ausreicht, um weitere Atome zu ionisieren. Dieser Vorgang wiederholt sich sehr oft. Um die dadurch

entstehende Elektronenlawine (den "Streamer") in Richtung des Drahts zu begrenzen, wird Isobutan als Löschgas verwendet. Die Elektronen, die dann den Draht erreichen, erzeugen einen Strompuls, der über die Ausleseelektronik nachgewiesen wird. Genauere Angaben sind in [8] zu finden.

### 4.3 Die Ausleseelektronik

Die aufgrund eines Teilchendurchgangs an den Drähten erzeugten Strompulse werden über einen Widerstand in eine Spannung umgewandelt. Zur Digitalisierung der Daten wird die an dem Widerstand abfallende Spannung mit einer angelegten Referenzspannung in einem Komparator verglichen. Ist die abfallende Spannung größer als die angelegte Referenzspannung, wird ein digitales Ausgangssignal erzeugt. Jeder Komparator ist nur für einen Draht zuständig. Das Ausgangssignal eines Komparators wird synchron mit der HERA-Clock an den Anfang einer Pipeline geschrieben.

Dir Polaritäten der Referenzspannungen für die Drähte und die Strips sind unterschiedlich. Sie werden über zwei getrennte Digital-Analog-Wandler auf einer Ausleseeinheit (im folgenden ROC² genannt) erzeugt. Die Werte der Referenzspannungen werden in ein 8-Bit-Register geschrieben. Sie sind in einem Bereich von 0 bis 2.55 Volt regelbar, obwohl der Spannungsabfall der Kanäle nur zwischen 130 und 200 mV liegt. Da aber die Referenzspannungen auf gesonderte Karten weitergeleitet werden, sind sie beim Transport mit Werten im Voltbereich weniger störanfällig als im Millivoltbereich. In den Bus-Terminals werden sie auf ein Zehntel ihres ursprünglichen Wertes reduziert.

Die Karten, auf die die Referenzspannungen weitergeleitet werden, sind DMBs<sup>3</sup>. Sie befinden sich direkt an den Enden der Kammern. Auf ihnen sind jeweils 16 Komparatoren mit den dazugehörenden Pipelines aufgebracht und es ist ein ODER über acht konsekutive Kanäle abgreifbar.

Die in Kapitel 3.6 erwähnten Pipelines sind im Falle des Myon-Systems 32 BC lang. Nach einem erfolgten Triggersignal werden die Daten aus den Pipelines in einen dafür vorgesehenen Speicher (FIFO, First In First Out), der sich auf dem ROC befindet, geladen.

Je ein ROC ist für die Auslese eines Moduls zuständig, d.h. ein ROC ist für 24 Busse mit bis zu insgesamt 6144 Drähten verantwortlich. Da die Daten aller Ebenen eines Moduls parallel ausgelesen werden, erfolgt eine Zusammenführung der Bus-Kabel in einem sogenannten Bus-Terminal. Dieses stellt die Verbindung zwischen den einzelnen Ebenen der Module und den dazugehörenden ROCs her und sorgt gleichzeitig für die Weiterleitung der benötigten Signale.

Aus technischen Gründen sind die ROCs in 5 Gruppen (Cluster) zu je 13 (12) ROCs unterteilt. In Tabelle 4.1 ist die Gruppenaufteilung angegeben.

$<sup>^2 \, \</sup>mathrm{ReadOutController}$

$<sup>^{3}\</sup>underline{\mathbf{D}}$ igital  $\underline{\mathbf{M}}$ odule  $\underline{\mathbf{B}}$ oard

[19, 22, 26]

| Gruppe | ROCnummer |    |    |    |    |    |    |    |    |    |    |    |    |

|--------|-----------|----|----|----|----|----|----|----|----|----|----|----|----|

| 0 (A)  | 1         | 3  | 5  | 7  | 9  | 11 | 13 | 15 | 16 | 17 | 18 | 19 | 31 |

| 1 (B)  | 0         | 2  | 4  | 6  | 8  | 10 | 12 | 14 | 20 | 21 | 22 | 23 | 24 |

| 2 (C)  | 32        | 33 | 34 | 35 | 47 | 49 | 51 | 53 | 55 | 57 | 59 | 61 | 63 |

| 3 (D)  | 36        | 37 | 38 | 39 | 40 | 48 | 50 | 52 | 54 | 56 | 58 | 60 | 62 |

| 4 (E)  | 25        | 26 | 27 | 28 | 29 | 30 | 41 | 42 | 43 | 44 | 45 | 46 |    |

Tabelle 4.1: Die Aufteilung der ROCs in Gruppen

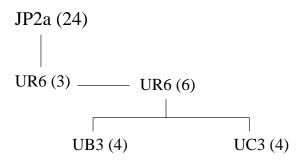

#### 4.3.1 Der ROD

Um die Signalverteilung zu den 64 ROCs technisch zu vereinfachen, gibt es fünf Verteilereinheiten (im weiteren Verlauf ROD<sup>4</sup> genannt), jeder einzelne von ihnen ist für die Signalverteilung in einem Cluster zuständig. Den RODs fällt die Aufgabe zu, die vier Signale, die vom zentralen Trigger kommen, an die ROCs zu verteilen. Dies sind im Einzelnen:

- die HERA-Clock dieses Signal liefert mit einer Frequenz von 10,4 MHz ein Taktsignal für die elektronischen Komponenten der Detektoren.

- das RUN-Signal es aktiviert das System für die Datennahme. Um tatsächlich Daten nehmen zu können, ist das System zusätzlich auf das nächste Signal angewiesen

- das Pipeline Enable-Signal im folgenden wird dieses Signal mit PEn für den aktiven und DPEn (D = Disable) für den passiven Zustand abgekürzt. Im aktiven Zustand sind die Pipelines zur Datenspeicherung freigegeben. Durch einen Trigger wird der passive Zustand ausgelöst und es können keine weiteren Daten in die Pipelines geschrieben werden (siehe Kapitel 3.6).

- das FastClear Signal dieses Signal muß nach jedem Auslesezyklus, unabhängig davon, ob er beendet oder abgebrochen wurde, gesendet werden. Damit werden alle alten, noch in den Pipelines vorhandenen Daten gelöscht und der Anfangszustand der Ausleseelektronik wiederhergestellt.

Auf der Rückseite des ROD befinden sich zwei Stecker, JP1 und JP2 [25]. Auf dem unteren Stecker (JP2) ist ein gesondertes Bus-System installiert, über das diese vier Signale zu den einzelnen ROCs geschickt werden. Zusätzlich sind auf

$<sup>^4\</sup>underline{R}$ ead $\underline{O}$ ut $\underline{D}$ istributor

diesem Stecker jeweils 16 Eingänge für die Signale RRDY (ROC is ready, ein Auslesezyklus ist abgeschlossen) und DFLAG (Digital Flag, die Mindestanforderung an möglichen Treffern ist erfüllt) vom ROC zum ROD angebracht. So können sich mit nur einem Auslesezyklus auf dem ROD die Zustände aller ROCs, für die dieser ROD zuständig ist, bestimmen lassen. In Abbildung 4.2 ist die Signalverteilung des JP2 Steckers des ROD dargestellt.

| 01a DFLAG01   | 01c RRDY01 |

|---------------|------------|

| 02a DFLAG02   | 02c RRDY02 |

| 03a DFLAG03   | 03c RRDY03 |

|               |            |

|               |            |

|               |            |

| 16a DFLAG16   | 16c RRDY16 |

| 22a RUN       | 22c GND    |

| 23a FastClear | 23c GND    |

| 24a PEn       | 24c GND    |

| 25a CLOCK     | 25c GND    |

Tabelle 4.2: Signalverteilung des JP2 Steckers auf dem ROD

#### 4.3.2 Der ROC

Die hardwaregesteuerte Auslese der einzelnen Module verläuft parallel und unabhängig voneinander. Dabei ist der ReadOutController das eigentliche Ausleseelement. Auf ihm befinden sich die Digital-Analog-Wandler für die Referenzspannungen, Speicher-Bausteine, logische Gatter und programmierbare Bausteine, die die Auslese steuern. Der wichtigste Baustein ist der Mode Controller, er ist für die Steuerung der Auslese der Daten in den Pipelines auf den DMBs in die internen Speicher auf dem ROC zuständig. Ein anderer Baustein ist der Code Manager, er verarbeitet die von den DMBs kommenden Daten in einer Kodierlogik, auf ihn wird weiter unten eingegangen.

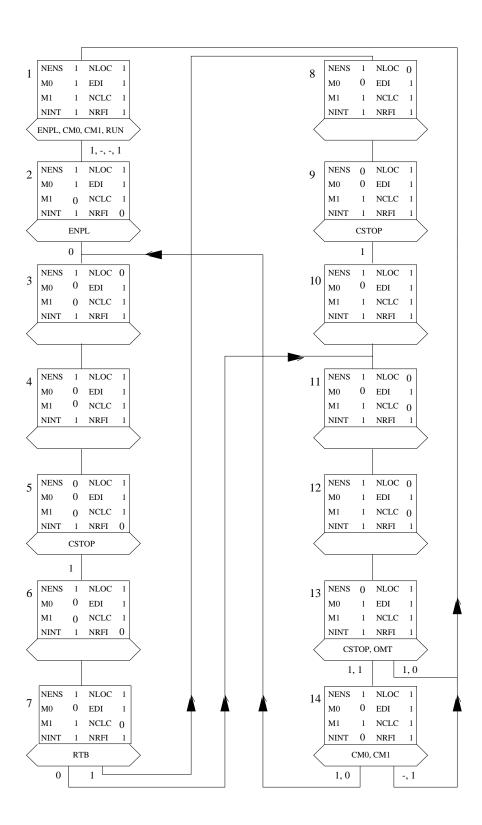

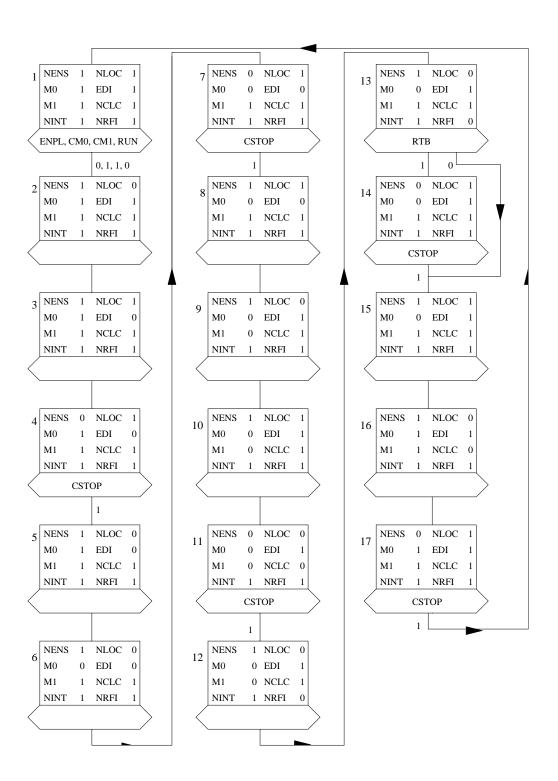

#### Der Mode Controller

Dieser Baustein ist vom Typ GAL20V8 [25]. Der Mode Controller ist eine "Zustandsmaschine", die aus 14 unterschiedlichen Zuständen besteht. Diese sind durch unterschiedliche Kombinationen der acht Ausgangsleitungen gegeben. Um

von einem Zustand in einen anderen zu gelangen, gibt es definierte Kombinationen der Eingangsleitungen.

Eine Auflistung aller Ein- und Ausgangssignale sowie ein kompletter Auslesezyklus sind im Anhang A gegeben. Der Auslesezyklus beginnt mit dem Grundzustand, der nach einem FastClear-Signal erreicht wird. Er beinhaltet das Aktivieren und Starten der Datennahme durch die Signale RUN und PEn, das Eintreffen eines Triggers, durch den Übergang des Signals PEn nach low (DPEn). Mit dem Triggersignal erhalten die Pipelines kein Taktsignal mehr von der HERA-Clock; die Daten werden innerhalb der Pipelines nicht mehr weitergeschoben. Um die Daten auslesen und weiterverarbeiten zu können, werden sie aus den Pipelines geschoben.

Das geschieht durch Zählpulse, im weiteren Strobe-Pulse genannt, die die Daten künstlich bis an das Ende der Pipelines weiterschieben. Da sich die zu einem Trigger gehörenden Daten an derselben Stelle in den Pipelines befinden, ist die Anzahl der Strobe-Pulse, die nötig ist bis die Daten am Ende der Pipelines angelangt sind, konstant. Für die ROCs der Gruppen A und C ist jeweils ein Puls notwendig. Die Daten der ROCs der Gruppen B, D und E stehen bereits am Ende der Pipelines, so daß keine Pulse benötigt werden.

Die Wirkung der Strobe-Pulse wird durch zwei Eingangsleitungen des Mode Controllers bestimmt, die ModeBits M0 und M1. Die Pulse haben drei unterschiedliche Aufgaben zu erfüllen. Die für die jeweilige Aufgabe benötigte Anzahl an Pulsen ist in je einem Register gespeichert. Zwei von ihnen sind für das Myon-System von Bedeutung.

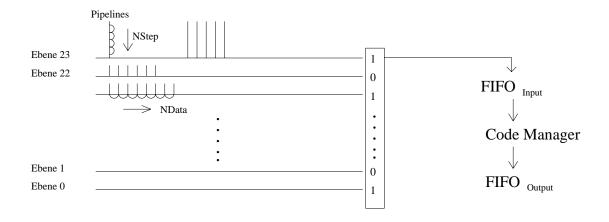

Der Inhalt des Registers  $\text{Reg}_{Step}$  wird aktiv, sobald M0 und M1 Null sind. In diesem Register steht die Zahl  $N_{Step}$ . Dieser Wert wird mit jedem Puls um Eins dekrementiert bis die Null erreicht ist. Damit befinden sich die Daten am Ende der Pipelines. Die Aus- und Eingänge der Pipelines einer Ebene sind so miteinander verknüpft, daß die Daten in ihnen seriell verschoben werden [22].

Die Ebenen werden parallel und drahtweise ausgelesen. Die Zahl  $N_{Data}$ , im Register  $Reg_{Data}$ , ist die Maximalzahl tatsächlich vorhandener Drähte einer Ebene bezogen auf die 24 möglichen Ebenen eines ROCs. Mit jedem dieser Pulse wird, für alle Ebenen eines ROC gleichzeitig, ein Bit pro Ebene in ein 24-Bit Wort geschrieben. Der Inhalt aus  $Reg_{Data}$  wird geladen, wenn M0 und M1 beide Eins sind

Die Daten, die aus den Pipelines kommen, sind invertiert. Eine Null entspricht einem gesetzten Kanal. Ist dementsprechend ein Bit in dem 24-Bit Wort ungleich Eins, werden an den Anfang dieses Worts acht Bits angefügt, die der noch zu sendenden Anzahl an Strobe-Pulsen entsprechen. Durch diese Zahl ist die Kanalnummer festgelegt. Das gesamte Wort wird in einen dafür vorgesehenen Speicher (FIFO<sub>Input</sub>) geschrieben. Es werden nur Wörter abgespeichert, in denen mindestens ein Bit ungleich Eins ist. Dieses Verfahren heißt "Nullunterdrückung".

Die Ebenen, deren Kanalzahlen kleiner als  $N_{Data}$  sind, liefern für jeden  $(N_{Data} - n)$ 'ten Puls  $(n = 0, 1, 2, ..., N_{Data})$ , für den  $N_{Data}$  - n größer als die eigene Kanalzahl ist, eine Eins. Abbildung 4.4 zeigt den Datenweg ab den Pipelines mit den Zählrichtungen von  $N_{Step}$  und  $N_{Data}$ .

Die dritte Zahl,  $N_{Trig}$  im Register  $Reg_{Trig}$ , wird im Myon-System nicht mehr verwendet.

Abbildung 4.4: Der Datenweg ab den Pipelines

$T_{Strobe}$  ist die Frequenz, mit der die Strobe-Pulse gesendet werden. Sie ist abhängig von der Kabellaufzeit  $\Delta t$  und damit von der Kabellänge L. Es gelten die Bedingungen:

$$\frac{1}{2} \cdot T_{Strobe} \leq \Delta t \leq T_{Strobe}$$

$$\Delta t = 10 \times L + 70ns$$

Die 70 ns sind die Verzögerungszeit durch die Bus-Terminals. Eine ausführliche Beschreibung dazu ist in [22].

#### Der Code Manager

Um nun die Adressen der gesetzten Kanäle zu erhalten, werden alle Einträge aus dem FIFO<sub>Input</sub> in einer Kodierlogik verarbeitet. Die aufbereiteten Daten werden umgerechnet und in einen anderen Speicher, den FIFO<sub>Output</sub>, geschrieben, wobei jede Null in einem Eintrag des FIFO<sub>Input</sub> einen Eintrag im FIFO<sub>Output</sub> zur Folge hat. Ein Wort aus diesem Speicher ist nur noch 16 Bit lang und enthält die vollständige Adresse eines einzelnen Kanals innerhalb eines Moduls. Die Bits Nummer Null bis einschließlich Nummer acht innerhalb einer Ebene geben die Kanalnummer an, die Bits Nummer neun bis einschließlich Nummer dreizehn die Ebenennummer. Die letzten beiden Bits dienen der Trigger- und der Endkennung und sind für diese Arbeit ohne Bedeutung. Die Steuerung der Kodierlogik

übernimmt ein Baustein vom Typ GAL16V8, der Code Manager [22]. Als Beispiel ist die Adresse des in Ebene eins gesetzten Kanals in Abbildung 4.4 in der 16-Bit Darstellung des FIFO $_{Output}$  angegeben. Der Inhalt des Registers Reg $_{Data}$  betrage 255, die Anzahl schon gesendeter Strobe-Pulse ist willkürlich zu 100 festgelegt, damit beträgt N $_{Data}$  zu diesem Zeitpunkt 155. Dem zuerst ausgelesene Kanal wird die höchste Kanalnummer in der betreffenden Ebene zugeordnet. Daraus ergibt sich dieselbe Kanalnummer wie N $_{DAta}$ : 155. In dezimalen Zahlen ausgedrückt entspräche die Adresse 667.

$$\underbrace{00}_{FIFOend-undTriggerkennung} \underbrace{000000}^{Ebenen} \underbrace{010011011}^{Kan\"{a}le}$$

#### Die Register des ROC

Jeder ReadOutController besitzt 19 VME-Register, die entweder les- oder beschreibbar sind. Sie bilden die Schnittpunkte der "Front-End-Elektronik" zum Prozessor und damit zur Software. Einige der beschreibbaren Register generieren interne Signale, sobald sie über ihre Adresse angesprochen werden, andere dienen als Speicher. Über die beschreibbaren Register wird zum Teil auch die Arbeitsweise des Mode Controllers mitbestimmt. Eine komplette Auflistung der Register und ihrer Aufgaben befindet sich in Anhang C [19, 22].

## Kapitel 5

# Prüfverfahren für das Myon–System

### 5.1 Motivation

Die Ausleseelektronik des Myon-Systems wurde in Zusammenarbeit von der RWTH Aachen und der Universität Hamburg speziell für den H1-Detektor entwickelt [22]. Ein bereits existierendes Programm [28] zur Überprüfung der Auslesekette war aufgrund von Veränderungen in dem Datennahmeprogramm des Myon-Systems nicht mehr lauffähig. Dadurch gab es keine Prüfverfahren mehr zur Kontrolle der Gesamtfunktion des ROC oder wichtiger Einzelfunktionen. Auch werden einige der für den ROC verwendeten Bausteine nicht mehr hergestellt und neuere, ähnliche Produkte entsprechen nicht genau den Anforderungen des Systems, so daß nur noch begrenzte Reserven zur Verfügung stehen. Aus diesem Grund wurden Testverfahren und -programme entwickelt [9], die es ermöglichen, die Funktion des ROCs zu überprüfen. Diese Verfahren und Programme sind so aufgebaut, daß eventuelle Fehler, auch ohne tiefe Kenntnisse vom Myon-System, zu finden und zu lokalisieren sind. Ein Teil der Prüfverfahren wird mit Hilfe einer multifunktionalen Input/Output-Karte, einer Lab-NB, der Firma National Instruments [10, 11], durchgeführt.

Tritt ein Defekt aufgrund eines einzelnen Bausteins auf, kann dieser leichter ersetzt werden als eine komplette Karte. Um die Funktionsweise des ROC oder einzelner Bauteile zu verstehen, war es notwendig, eine dem Myon-System entsprechende Auslesekette zu betreiben: einen Teststand. Dieser muß losgelöst vom eigentlichen System sein, um die Programme zu entwickeln und zu testen, ohne das Myon-System in seiner Funktion einzuschränken.

### 5.2 Der Teststand

Der Teststand besteht aus einem VME-Rahmen für Elektronikkarten (VME-Crate [12, 13]) und einem Macintosh Computer. Es folgt eine Auflistung der Karten, die sich in dem Einschubrahmen befinden, die jeweilige Steckplatznummer # (Slot), ist in Klammern angegeben.

- Eine Prozessorkarte (1)

- Eine Schnittstellenkarte (2)

- Ein ReadOutDistributor (6)

- Eine Input/Output-Karte zur Signalerzeugung (8)

- Ein VME-Bus-Display (11)

- Ein ReadOutController (13)

- Ein WireDigitalModuleBoard (16)

- Ein Bus-Terminal (19 + 21)

Die Prozessorkarte ist ein FIC8231, eine CPU(68030)-Karte mit einem VME-Bus-Controller, die im Teststand die Zugriffsrechte der einzelnen Teilnehmer (Karten) auf den VME-Bus regelt. Der Prozessor dieser Karte läuft ohne internes Betriebssystem, er führt die Programme aus, die er über den Macintosh Computer erhält. Die Schnittstellenkarte ist eine MacVEE-Karte [14], sie stellt die Verbindung zwischen dem Macintosh Computer und dem Crate her. Sie bildet, zusammen mit einer Micron-Karte [14] im Macintosh Computer, das Interface zwischen dem NuBus des Macintosh Computers und dem VME-Bus des Crates. Dies geschieht über zwei 60-polige Flachbandkabel, von denen eines der Adreß- und das andere der Daten-Bus ist. Im Macintosh Computer befindet sich die Lab-NB Karte, auf sie wird in Kapitel 5.4 näher eingegangen.

Damit der Teststand losgelöst von HERA operieren kann, braucht er einen eigenen internen Taktgeber. Dieser wird von einem 10 MHz Oszillator geliefert, der direkt auf dem ROD aufgebracht ist. Das RUN-Signal wird über Software auf dem ROD generiert.

Die beiden anderen Signale neben dem RUN-Signal, Pipeline Enable (PEn) und FastClear (FC), die im Myon-System der zentrale Trigger sendet, werden auf einer speziell angefertigten TTL-signalerzeugenden Input/Output-Karte generiert. Im weiteren Verlauf dieser Arbeit wird sie Signal-I/O-Karte genannt und nicht zu verwechseln mit der Lab-NB Karte. Die Daten der Signal-I/O-Karte werden über zwei LEMO-Stecker auf den ROD übertragen. In Tabelle 5.1 sind alle möglichen Signalkombinationen aufgelistet.

| Signal   | Leitung1 | Leitung 3 |

|----------|----------|-----------|

| FCuDPEn  | 0        | 0         |

| DFCuDPEn | 1        | 0         |

| FCuPEn   | 0        | 1         |

| DFCuPEn  | 1        | 1         |

Tabelle 5.1: Mögliche Signalkombinationen für den Teststand aus den Signalen PEn und FC

FCuDPEn: Das FastClear-Signal ist aktiv, während die Pipelines Disabled sind, das entspricht dem Ende bzw. dem Anfang eines Auslesezyklus im aktiven Detektor.

**DFCuDPEn**: Das FastClear-Signal ist low und die Pipelines sind Disabled, das entspricht einem Triggersignal im aktiven Detektor.

FCuPEn: Während datenaufnahmebereiter Pipelines liegt ein FastClear—Signal an. Dieser Zustand ist im aktiven Detektor nicht möglich, sondern ist ausschließlich eine Signalkombination des Teststandes.

**DFCuPEn**: Das Signal FastClear ist low während die Pipelines Enabled sind, das entspricht der normalen Datennahme.

Ein großer Vorteil dieser Signal-I/O-Karte liegt darin, daß das Signal Fast-Clear als statisches Signal erzeugt werden kann, im Myon-System ist das Signal nur ein kurzer Puls. Dieser Unterschied ist bei den Signalkombinationen in der Tabelle 5.1 zu beachten, die Kombinationen gelten nur für den Teststand. Dadurch kann der Zustand des ROC auch während eines FastClears anhand eines lesbaren Registers untersucht werden. Trotz dieser Modifizierungen ist der ROD wieder das signalverteilende Element, und es wäre ohne weiteres möglich, mehr als einen ROC im Teststand zu betreiben.

Das VME-Bus-Display kann als optische Kontrolle dienen, welche der Bits, die Adreß- oder die Datenbits, im Augenblick aktiv sind.

Der zu prüfende ROC ist an einem Extender befestigt, der in das Crate eingesetzt ist. Dadurch ist ein freier Zugriff auf den ROC, bzw. auf die auf ihm befindlichen Bausteine möglich. Damit können mit einem Oszilloskop einzelne Signale nachgemessen werden. Die Signalweiterleitung wird von dem Extender im Teststand nicht beeinflußt.

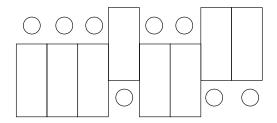

Im Teststand befindet sich weiterhin ein WDMB, ein Wire DMB, durch das eine Ebene mit 16 Drähten dargestellt wird. Da das WDMB für sich alleine nicht in das Crate eingesetzt werden kann, ist es auf einer unterstützenden Karte aufgebracht. Über den rückwärtigen Anschlußstecker dieser Karte erfolgt auch die

Spannungsversorgung des WDMB.

Das Myon-System verwendet keine VME Bus-Terminals. Um den Teststand kompakt zu halten, war es notwendig VME Bus-Terminals zu benutzen. Ausgehend von existierenden Schaltplänen¹ konnten Platinen geätzt und zu VME Bus-Terminals nachgebaut werden [25, 27]. Über diese Terminals werden die Daten vom und zum WDMB, die Referenzspannungen, sowie die Signale SCK für die HERA-Clock, STR für die Strobe-Pulse, M0 und M1 für die beiden Mode Bits und EDI (Enable Data Inn) für die Datenrichtung geschickt.

Da die Entfernungen im Teststand im Vergleich zum Myon-System sehr klein sind (max. 0.5 m Kabellänge), muß auf Kabellaufzeiten keine Rücksicht genommen werden. Dadurch besteht die Möglichkeit, in einigen Tests Oszillatoren mit kleineren Frequenzen, z.B. 1 MHz, zu verwenden. Bei diesen kleinen Frequenzen können die einzelnen Strobe-Pulse mit der Lab-NB gezählt werden (siehe Kapitel 5.5.3).

Die Testprogramme sind in zwei Gruppen unterteilt. Die Programme, die nur die Ausleseelektronik direkt ansprechen heißen Direkte Prüfverfahren. Die anderen Programme sprechen die Ausleseelektronik auch direkt an, aber arbeiten zusätzlich mit der Lab-NB. Die erste Gruppe ist wiederum in zwei Teile gegliedert, in einen "Pattern-Test" und in einen "Flaggen-Konsistenz-Test". Alle Testprogramme sind für den Teststand konzipiert worden, wobei die Programme der ersten Gruppe auch für das Myon-System genutzt werden können.

### 5.3 Direkte Prüfverfahren

Für die Direkten Prüfverfahren wurde auf dem Macintosh Computer eine benutzerfreundliche, graphische Oberfläche geschaffen. Diese wurde mit Hilfe des Programmierwerkzeugs "ViewIt<sup>TM</sup>" [15] erstellt. Die in "ViewIt" bereitgestellten Routinen ermöglichen eine einfache Darstellung von Objekten und ihre Verknüpfung mit den Programmen, in diesem Fall die Verknüpfung mit den Direkten Prüfverfahren. Damit ist ein einfaches Auswählen unterschiedlicher Programme und Einstellungen von Parametern der Direkten Prüfverfahren ermöglicht worden.

Abhängig von der Wahl des Tests, Flaggen-Konsistenz- oder Pattern-Test, gibt es unterschiedlich viele Parameter, die innerhalb angegebener Grenzen frei wählbar sind [26, 28].

## 5.3.1 Der Flaggen-Konsistenz-Test

Im Flaggen-Konsistenz-Test wird in unterschiedlichen Zuständen des Auslesezyklus jeweils das Status Register des ROC abgefragt. Aus dem Inhalt dieses

<sup>&</sup>lt;sup>1</sup>Die Schaltpläne erhielten wir von einer anderen Detektorkomponente, der BDC (BackDrift-Chamber), die VME Bus-Terminals benutzt

Registers kann der Zustand des ROC zum Zeitpunkt der Abfrage abgelesen werden. Die Anzahl der Inhalte des Registers FIFO<sub>Output</sub> werden mit dem Inhalt aus  $N_{Digi}$  verglichen und das achte Bit im Status Register, die digitale Flagge, wird explizit über den Inhalt des Registers Digi $_{Thr}$  überprüft.

Das Status Register besteht aus 16 Bits, "Flaggen". Diese werden auf ihren erwarteten Wert, ihre Konsistenz, geprüft. In Tabelle 5.2 ist die Bedeutung eines jeden in diesem Wort gesetzten Bits erläutert. Die Bits des Status Registers sind direkte Ein- und Ausgangssignale des Mode Controllers und Zustandsbits des Code Managers und der FIFOs.

| Bitnr. | Signalname und Bedeutung                                |

|--------|---------------------------------------------------------|

|        |                                                         |

| 0      | RUN, ein Run ist aktiviert worden                       |

| 1      | M0, Zustand des Mode Bits M0                            |

| 2      | M1, Zustand des Mode Bits M1                            |

| 3      | RTB, die Trigger Bits werden ausgelesen                 |

| 4      | OMT, es wird mehr als eine Zeitscheibe ausgelesen       |

| 5      | CM0, Bit 0 des Kommando Registers 0                     |

| 6      | CM1, Bit 1 des Kommando Registers 0                     |

| 7      | DFLAG, die "digitale" Flagge ist gesetzt                |

| 8      | EEVINT, die Interrupt Anforderung des Mode Controllers  |

|        | wird intern zugelassen                                  |

| 9      | EMCINT, die Interrupt Anforderung des Code Managers     |

|        | wird intern zugelassen                                  |

| 10     | OEMPTY, das FIFO $_{Output}$ ist leer                   |

| 11     | OFULL, das FIFO $Output$ ist voll                       |

| 12     | IEMPTY, das FIFO $_{Input}$ ist leer                    |

| 13     | IFULL, das FIFO $_{Input}$ ist voll                     |

| 14     | MCRD, der Mode Controller befindet sich im Zustand Eins |

| 15     | CMRD, der Code Manager hat einen Zyklus abgeschlossen   |

Tabelle 5.2: Bedeutung eines gesetzten Bits im Status Register

Der Flaggen-Konsistenz-Test dient einer groben Fehlersuche, falls sich dabei ein immer wiederkehrender Fehler bei einem bestimmten ROC im Myon-System einstellt, kann dieser dann zur genaueren Untersuchung in den Teststand eingebaut werden.

Um einem realen Auslesezyklus – wie im Myon–System – zu entsprechen, wird der Flaggen–Konsistenz–Test im OMT–Modus (One More Timeslice, siehe weiter unten "Initialisierung der Ausleseelektronik") betrieben. Mit Beginn des Programms wird als erstes die Ausleseelektronik initialisiert. Das bedeutet, in die

beschreibbaren Register des ROD und ROC werden vordefinierte Werte geschrieben.

Es folgt eine kurze Beschreibung der Test-Routinen. Der Aufbau der einzelnen Routinen ist ähnlich. Nach Abschluß der Überprüfung des Inhalts aus dem Status Register bzw. einzelner, relevanter Bits liefert das Programm jeweils einen bestimmten Wert zurück. Anhand dessen ist eine genauere Fehlerbeschreibung möglich. Der Verlauf des Flaggen-Konsistenz-Tests ist in Abbildung 5.1 zu sehen. In Tabelle 5.3 sind die Test-Routinen und die darin abgefragten Bits zusammengefaßt.

#### Initialisierung der Ausleseelektronik

Bei der Initialisierung der Ausleseelektronik wird zwischen dem Teststand und dem Myon-System unterschieden. Im Gegensatz zum Teststand befinden sich im Myon-System zwischen dem Computer und den RODs noch weitere Komponenten, die während eines Testlaufs mit anderen Parametern initialisiert werden müssen (z.B. CES VIC8250 [16]).

Im Myon-System dient der ROD lediglich als Verteiler der Signale. Die einzelnen ROCs erhalten in den meisten Fällen die gleichen Werte in die beschreibbaren Register, nur die Inhalte der Register  $\text{Reg}_{Data}$  können stark voneinander abweichen.

Im oben erwähnten OMT-Modus werden zusätzlich zu den getriggerten Daten die nachfolgenden Daten ausgelesen. Eine weitere Zeitscheibe auslesen heißt, die in den direkt nachfolgenden Plätzen in den Pipelines stehenden Daten mitauszulesen. Im Myon-System können bis zu vier Zeitscheiben ausgelesen werden.

#### Der Zustand des ROC während eines anhaltenden FastClear Signals

Aufgrund der Signal-I/O-Karte im Teststand ist es möglich ein quasistatisches FastClear-Signal zu erzeugen. Dadurch kann der Zustand des ROC während dieses Signals überprüft werden. Aus dem Zyklus des Mode Controllers ist abzulesen, daß die beiden Mode Bits M0 und M1 gesetzt sein müssen. Weitere Messungen mit einem Oszilloskop haben bestätigt, daß sowohl das 14. als auch das 15. Bit (MCRD und CMRD) gesetzt sind. Falls sich in den FIFOs – Input wie auch Output – noch Daten befunden haben, werden sie durch das FastClear gelöscht. Daraus folgt, daß die Bits OEMPTY und IEMPTY gesetzt sein müssen. Und weder OFULL noch IFULL dürfen gesetzt sein. Auch das Bit für die digitale Flagge (DFLAG) wird durch das FastClear-Signal in seinen Ursprungszustand zurückgesetzt.

Durch die vorgegebene Initialisierung des ROD darf das RUN-Bit, nicht gesetzt sein

Diese Untersuchung kann nur am Teststand durchgeführt werden, da es nicht

### Flaggen-Konsistenz-Test

Initialisierung der Ausleseelektronik

(von der Wahl des Systems abhängig)

Untersuchung des Status Registers während des Signals FC

(nur im Teststand möglich)

Untersuchung des Status Registers waehrend der Datennnahme

Senden eines Triggersignals

(Übergang von PEn zu DPEn)

Warten, bis die Kodierung der Daten beendet ist

Untersuchung des Status Registers nach der Datennahme

Vergleich der aus FIFO<sub>Output</sub> ausgelesenen Datenmenge

mit dem Inhalt des Registers N<sub>Digi</sub>

Abbildung 5.1: Der Programmverlauf des Flaggen-Konsistenz-Tests

möglich ist, am Myon-System ein quasistatisches FastClear-Signal zu erzeugen. Nach Abschluß dieser Routine wird der ROD im Teststand neu initialisiert, um sicherzugehen, daß in den einzelnen Registern nur gültige Werte stehen.

#### Der Zustand des ROC während der Datennahme (PEn)

Die Signale RUN und PEn werden gesendet, um Daten aufzunehmen. Der Inhalt des Status Registers wird auf die Bits RUN, M0, M1, RTB, OMT, DFLAG, OEMPTY, OFULL, IEMPTY, IFULL, MCRD und CMRD abgefragt.

Im Teststand können die Daten über einen von der Universität Hamburg entwickelten ROC-Eingangs-Tester (RET) erzeugt werden. Dieser sendet definierte Zustände an den ROC, die den über die Bus-Terminals aus den Komparatoren kommenden Signalen entsprechen. Je nach Schalterstellung simuliert er, daß alle Kanäle einer gewählten Ebene gesetzt oder nicht gesetzt sind. Die Verbindung vom RET zum ROC läuft nur über ein Kabel zu einem der beiden vorderen Stecker (Frontconnectoren) auf dem ROC. Je nach Wahl des Frontconnectors können die Ebenen null bis elf, oder zwölf bis 23 angesprochen werden. Liegen keine Daten an den Frontconnectoren an, befinden sich diese in einem undefinierten Zustand. Damit werden zufällige Daten generiert. Wird die Verbindung zwischen dem Bus-Terminal und dem ROC völlig unterbrochen, werden durch die offenen Enden undefinierte Daten erzeugt, d.h. es ist nicht voherzusehen, in welchem Wort des FIFO<sub>Input</sub> eventuelle Bits gesetzt sind oder nicht.

Aus dem Auslesezyklus des Mode Controllers, im Anhang A, und aus Messungen ist ersichtlich, daß die Bits RUN, M0, OMT, OEMPTY, IEMPTY und CMRD den Wert 1 besitzen müssen, die restlichen Bits den Wert 0.

Nach dieser Routine wird per Software ein Trigger generiert, d.h. die Pipelines werden Disabled und die Auslese beginnt.

#### Der Zustand des ROC nach der Kodierung der Daten

Es folgt eine Routine, die aus mehreren Warteschleifen besteht. In zwei der Schleifen werden die Inhalte der beiden Mode Bits M0 und M1 abgefragt, ob sie den erwarteten Zustand besitzen. Der wiederum ist vom Auslesemodus abhängig (OMT, Tabelle 5.3). Eines der wichtigsten Kriterien ist, daß der Code Manager mit der Kodierung der Inhalte aus dem FIFO $_{Input}$  in den FIFO $_{Output}$  abgeschlossen hat.

In die Warteschleifen ist ein Zeitlimit implementiert worden. Sobald dieses überschritten wird, bricht die Routine mit einer entsprechenden Fehlermeldung ab. Das kann der Fall sein bei einer zu großen Datenmenge, die während der Prüfprogramme durch vorgegebene Werte in der Initialisierungsroutine nicht auftreten darf, oder falls der Code Manager selbst defekt ist. Im OMT-Modus muß der Code Manager die Kodierung noch nicht beendet haben. Wenn im FIFO<sub>Output</sub> alle Speicherplätze belegt sind, können keine weiteren Daten aus dem FIFO<sub>Input</sub>

in das FIFO $_{Output}$  geschrieben werden. Das kann anhand eines gesetzten oder nicht gesetzten Bits im Status Register abgefragt werden.

#### Der Zustand des ROC nach einem abgeschlossenen Auslesezyklus

Wie in den vorherigen Programmen wird der Inhalt des Status Registers auf bestimmte Bits geprüft, in diesem Fall sind es die Bits RUN, M1, OMT, IEMPTY und CMRD, die gesetzt sein müssen, und RTB, OFULL und IFULL die nicht gesetzt sein dürfen.

Passiert es, daß das Bit OFULL gesetzt ist, ist in vielen Fällen das Bit IEMPTY nicht gesetzt. Da der Code Manager dementsprechend seinen Zyklus noch nicht abgeschlossen hat, wird das FIFO<sub>Output</sub> ausgelesen und über das Register CCINT der Code Manager aufgefordert, seine Arbeit wiederaufzunehmen und zu beenden.

Unter der Annahme, daß das Bit OFULL nicht gesetzt ist, wird der Inhalt des FIFO $_{Output}$  gelesen und die Anzahl der Einträge gezählt. Nach einer nochmaligen Überprüfung, daß sich auch im FIFO $_{Input}$  keine weiteren Daten mehr befinden, die noch umgerechnet werden müssen, d.h. Bit IEMPTY muß gesetzt sein, wird die Anzahl der tatsächlich ausgelesenen Einträge mit dem Inhalt des lesbaren Registers  $N_{Digi}$  verglichen.

Die digitale Flagge wird indirekt über die Anzahl der Testdurchläufe, und über die Register  $\operatorname{Reg}_{Data}$  und  $\operatorname{Digi}_{Thr}$  kontrolliert. Im ersten Drittel der Testdurchläufe ist der Inhalt von  $\operatorname{Digi}_{Thr}$  größer als der von  $\operatorname{Reg}_{Data}$ . Das Bit DFLAG muß null sein, da die Bedingungen für das Setzen der digitalen Flagge nicht erfüllt werden können. Im zweiten Drittel sind die Inhalte der beiden Register gleichgroß, im letzten Teil der Testdurchläufe ist der Inhalt von  $\operatorname{Reg}_{Data}$  größer als der von  $\operatorname{Digi}_{Thr}$ . In beiden Fällen muß das Bit DFLAG gesetzt sein.

Von der Erwartung der oben beschriebenen Routinen abweichende Ergebnisse werden von einer Fehlerberechnungsroutine bearbeitet. Eventuell aufgetretene Fehler werden in ihrer Art und Häufigkeit gesammelt ausgegeben.

In Tabelle 5.3 ist die Abfrage der einzelnen Bits aus dem Inhalt des Status Registers in den unterschiedlichen Routinen zusammengefaßt.

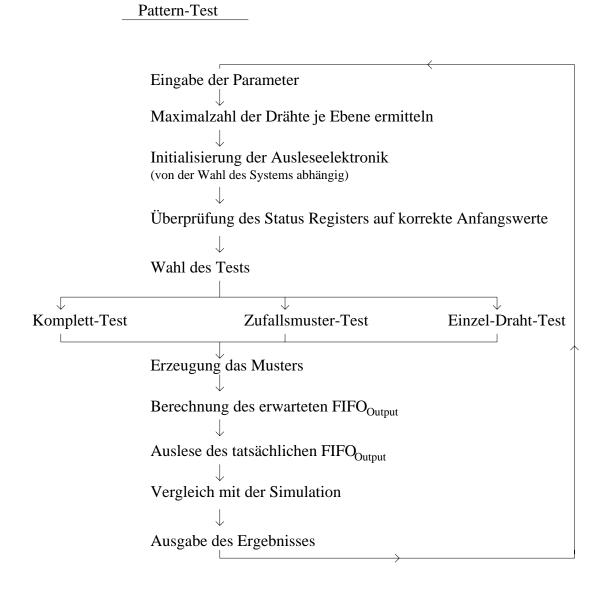

#### 5.3.2 Der Pattern-Test

Pattern ist der Ausdruck für ein beliebiges Bit-Muster. Aus den dafür vorgesehenen Speichern, den FIFO $_{Pattern}$ , wird ein Bit-Muster über das Bus-Terminal bis an die Komparatoren gesendet. Von dort wird es, wie normale Daten, vom ROC wieder ausgelesen. Der Weg führt zurück über die Pipelines, das Bus-Terminal und das FIFO $_{Input}$  in das FIFO $_{Output}$ .

Dieser Test bietet eine Möglichkeit, die komplette Auslesekette zu überprüfen.

| Bezeichnung | Routine 1 | Routine 2 | Routine 3 | Routine 4 |

|-------------|-----------|-----------|-----------|-----------|

|             |           |           | OMT/ -    |           |

| RUN         | 0         | •         | _         | •         |

| M0          | •         | •         | ∘/•       |           |

| M1          | •         | 0         | •/•       | •         |

| RTB         |           | 0         | _         | 0         |

| OMT         | _         | •         | •/∘       | •         |

| CM0         | _         | _         | _         | _         |

| CM1         | _         | _         | _         | _         |

| DFLAG       | 0         | 0         | _         | _         |

| EEVINT      | _         | _         | _         | _         |

| EMCINT      | _         | _         | _         | _         |

| OEMPTY      | •         | •         | _         | _         |

| OFULL       | 0         | 0         | _         | 0         |

| IEMPTY      | •         | •         | -         | •         |

| IFULL       | 0         | 0         | -         | 0         |

| MCRD        | •         | 0         | - / •     | _         |

| CMRD        | •         | •         | •/•       | •         |

Routine 1 : Der Zustand des ROC während eines anliegenden FastClear Signals

Routine 2 : Der Zustand des ROC während der Datennahme (PEn)

Routine 3 : Der Zustand des ROC nach der Kodierung der Daten

Routine 4 : Der Zustand des ROC nach Beendigung eines Auslesezyklus

• : Bit muß gesetzt sein

o : Bit darf nicht gesetzt sein

- : nicht relevant

Tabelle 5.3: Zusammenfassung der Abfrage der einzelnen Bits aus dem Status Register des ROC

Über das Signal EDI (siehe Anhang A) kann die Datenrichtung geändert werden. Wenn das Signal aktiv ist, werden die Daten von den Enden der Pipelines zum ROC übertragen, andernfalls vom ROC an die Eingänge der Front-End-Elektronik [22].

#### **Funktionsweise**

Zwei der beschreibbaren Register des ROC sind zur Speicherung von Bit-Mustern vorgesehen, das FIFO $_{Pattern}$ (Wire) und das FIFO $_{Pattern}$ (Strip). Beide sind 256 "Wörter" tief, im Fall des FIFO $_{Pattern}$ (Wire) sind diese 16 Bit lang. Die Wörter des FIFO $_{Pattern}$ (Strip) sind jeweils nur acht Bit lang, da es lediglich acht Strip-Ebenen bzw. -Busse gibt.

Dieser Testzyklus wird von einem weiteren programmierbaren Baustein, dem Test Controller, gesteuert. Er ist wie der Mode Controller vom Typ GAL20V8. Da der Test Controller mit den gleichen Signalen wie der Mode Controller betrieben wird, sind die an- und abgehenden Leitungen beider GALs parallel miteinander verbunden.

Durch das RUN-Signal ist sichergestellt, daß nur der jeweils zuständige Controller den ROC steuert. Die Ausgänge des gerade nicht aktiven Controllers werden hochohmig geschaltet. Der Mode Controller, der für den Auslesezyklus während der Datennahme zuständig ist, übernimmt die Steuerung des ROC, wenn das RUN-Signal gesetzt ist. Daraus folgt die Bedingung, daß der Test Controller die Zyklen ausschließlich bei einem passiven RUN-Signal kontrollieren kann. Der gesamte Pattern-Test ist nur dann möglich, wenn sowohl das RUN-Signal als auch das Signal PEn nicht gesetzt sind. Ein Zyklusbild des Test Controllers mit den Ein- und Ausgangssignalen ist im Anhang D zu finden.

Mit dem Pattern-Test sind falsche Verbindungen oder defekte Kanäle schnell zu entdecken. Anhand eventueller Fehlermeldungen ist auch zu erkennen, ob es sich um ein komplettes Element oder nur um einzelne Kanäle handelt, die defekt sind. Dieses Prüfverfahren ist in drei Bereiche gegliedert. Es können alle Drähte eines ROC nacheinander getestet werden, oder ein zufällig berechnetes Bit-Muster wird zur Kontrolle in die FIFOs geschrieben, oder es kann ein bestimmter Kanal in einer ausgewählten Ebene überprüft werden.

Zu Beginn des Programms wird mit einer Routine die Maximalzahl der Drähte einer jeden Lage des zu testenden ROC aus einer Tabelle gelesen und gespeichert. Die zu testenden Bit-Muster werden in die FIFO<sub>Pattern</sub> geschrieben und gleichzeitig für spätere Zwecke gespeichert.

Das Schreiben einer drei in das Register "Kommando Register 0" veranlaßt den ROC das Muster aus den FIFO $_{Pattern}$  bis an den Anfang der Pipelines zu schieben.

Es ist zu beachten, daß ein Wort aus dem FIFO<sub>Pattern</sub> den Ebenen "Bitweise" zugeordnet wird. Das erste Bit in einem Wort entspricht der ersten Ebene, das

zweite Bit der zweiten Ebene usw.. Wie bei der Auslese der Daten werden nun die einzelnen Worte mit dem Inhalt des Registers  $\operatorname{Reg}_{Data}$  eingelesen. Um die Daten korrekt auszulesen, müssen sie durch die komplette Pipeline geschoben werden. Da diese im Myon-System 32 bc lang ist, muß der Inhalt des Registers Reg<sub>Stev</sub> während des Pattern-Test 32 betragen. Daß zuerst in das FIFO<sub>Pattern</sub> geschriebene Wort steht auch als erstes Wort zur Auslese in das  $FIFO_{Input}$  bereit. Für die Kanäle gilt ähnliches, ein in dem ersten ausgelesenen Wort gesetztes Bit entspricht dem letzten Kanal der durch dieses Bit gesetzten Ebene (siehe Kapitel  $4.3.2 \rightarrow \text{Der Code Manager}$ ). Die in den nachfolgenden Wörtern gesetzten Bits werden den Kanälen in absteigender Reihenfolge zugewiesen. Hier ist darauf zu achten, daß die Bit-Muster nicht invertiert sind. In Kapitel 6.1 ("Die Parameter des Pattern-Test") wird die Zuordnung der Bits der Wörter aus dem FIFO<sub>Pattern</sub> zu den einzelnen Kanälen und Ebenen anhand eines Beispiels näher erläutert. Das zuvor abgespeicherte Bit-Muster wird mit Hilfe einer Routine in den erwarteten Inhalt des Registers FIFO<sub>Output</sub> umgerechnet und getrennt nach Drähten und Strips gespeichert.

Eine andere Routine vergleicht jeden Eintrag aus dem Register FIFO $_{Output}$  mit der Erwartung. Abweichungen von der Erwartung werden in getrennten Tabelle ausgegeben:

- 1. Im Register FIFO<sub>Output</sub> gefundene aber nicht erwartete Kanäle

- 2. In der Routine für die Draht-Lagen erwartete aber nicht gefundene Kanäle

- 3. In der Routine für die Strip-Lagen erwartete aber nicht gefundene Kanäle Abbildung 5.2 zeigt den Programmverlauf des Pattern-Test.

#### Komplett-Test

Bei diesem Prüfverfahren werden nacheinander alle Kanäle einer Ebene überprüft, parallel für alle Ebenen eines ROC. Dazu wird eine Schleife von null bis x durchlaufen, x entspricht dem Inhalt des Registers  $\text{Reg}_{Data}$ .

Mit der ersten Schleife wird jeweils die Nummer der zu prüfenden Kanäle festgelegt. Innerhalb der ersten Schleife wird eine zweite Schleife durchlaufen. Deren Anfangswert wird bei jedem Durchlauf um eins dekrementiert, der Anfangswert entspricht der Maximalzahl an Kanälen. Mit jedem Durchlauf der zweiten Schleife wird ein Wort in das FIFO<sub>Pattern</sub> geschrieben.

D.h. im ersten Durchlauf der ersten Schleife werden durch die zweite Schleife nur die Kanäle gesetzt, deren Nummern mit dem Inhalt des Registers  $\operatorname{Reg}_{Data}$  übereinstimmen. Alle restlichen Kanäle werden zu null gesetzt. Im zweiten Durchlauf der ersten Schleife werden alle Kanäle, deren Nummern mit dem Inhalt aus  $\operatorname{Reg}_{Data}$  - 1 identisch sind, gesetzt, die übrigen Kanäle werden wieder zu null gesetzt. Damit wird die zweite Schleife bei jedem Wert der ersten Schleife, komplett durchlaufen. Nach jedem Durchlaufen der ersten Schleife wird das oben

Abbildung 5.2: Der Programmverlauf des Pattern-Tests

beschriebene Muster in die Komparatoren gesendet und wieder ausgelesen. Der Inhalt des FIFO<sub>Output</sub> wird nach jeder ersten Schleife mit einem vorher berechneten Wert verglichen. Dieses Prüfverfahren ist sehr zeitaufwendig, es bietet aber eine sichere Möglichkeit, **alle** Kanäle zu überprüfen.

#### Zufallsmuster-Test

Die kleinste Einheit einer Lage ist ein Element, bestehend aus 16 Kanälen. Über eine Routine wird ein zufälliges Bit-Muster für jeweils ein Element aller Ebenen generiert, d.h. 16 Wörter. Dieses Pattern wird, je nach Anzahl der Elemente in einer Ebene, vervielfältigt. Die Menge der Elemente ergibt sich aus der Zahl der Kanäle in einer Ebene und ist zuvor bestimmt worden. Das Muster für die Draht- und die Strip-Ebenen ist unterschiedlich. Anhand des Zufallsmuster wird das erwartete Ergebnis berechnet und mit dem tatsächlichen FIFO $_{Output}$  verglichen. In Kapitel 6.1  $\rightarrow$  "Parameter des Pattern-Test, ist ein Beispiel für den Zufallsmuster-Test gerechnet.

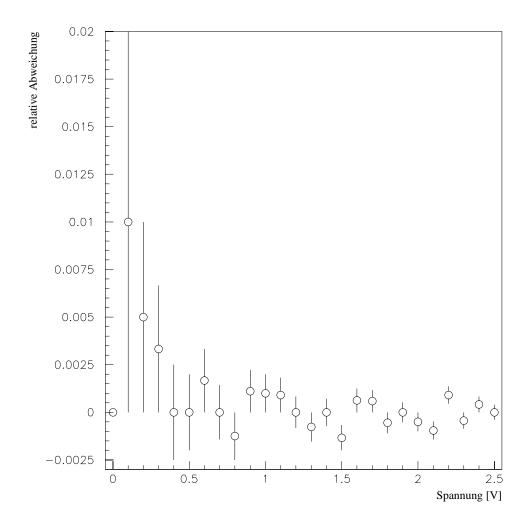

Eine Schwierigkeit des gesamten Pattern–Test besteht in der Höhe der Referenzspannungen. Damit das Muster durch die Komparatoren gelangt, müssen die Referenzspannungen für den Pattern–Test einerseits erniedrigt werden. Andererseits kann das Setzen verhältnismäßig vieler Kanäle zum gleichen Zeitpunkt und eine zu niedrige Referenzspannung das Überspringen des Signals auf einen benachbarten Kanal im WDMB und damit einen "Fehler" verursachen. Aus diesem Grund ist es wichtig, die Referenzspannungen korrekt einzustellen, um Fehler, die nicht systembedingt sind, zu vermeiden. Im Teststand sind die Werte der Referenzspannung für den Pattern–Test zu 40 mV festgesetzt. Dort wird auch nur  $\text{Ref}_{Wire}$  verwendet, so daß  $\text{Ref}_{Strip}$  ohne Bedeutung ist und den gleichen Wert wie im Myon–System besitzt, nämlich 130 mV.

#### Einzel-Draht-Test

Mit diesem Verfahren kann ein einzelner Kanal in einer bestimmten Ebene getestet werden. Die Wahl der Kanal- und Ebenennummer erfolgt wieder über die Eingabeparameter am Anfang des Pattern-Tests im Menüfenster (siehe Kapitel 6.1). Die für den Kanal und die Ebene eingegebenen Zahlen werden auf ihren Gültigkeitsbereich geprüft, da nicht jede Ebene mit der Maximalzahl an Drähten (256) ausgestattet ist.

Die Ebenen 16 bis 23, die Strip-Ebenen, werden auf die Zahlen null bis acht umgerechnet, da es für sie ein gesondertes  $FIFO_{Pattern}(Strip)$  gibt und von diesem nur die ersten acht Bits verwendet werden.

Der Eingabeparameter der Ebene wird in das zu setzende Bit umgerechnet (siehe Kapitel  $5.3.2 \rightarrow$  Funktionsweise). Die Maximalzahl an Kanälen ist wieder die Durchlaufzahl der Schleife in dieser Routine. Um den gewünschten Kanal zu setzen, wird bei jedem Schleifendurchlauf die zu dem Zeitpunkt getätigte Anzahl an

Durchläufen mit der zu setzenden Kanalzahl addiert. Diese Summe wird mit der Inhalt des Register  $\text{Reg}_{Data}$  verglichen. Solange die beiden Werte nicht übereinstimmen, wird bei jedem Durchlauf eine null in das FIFO<sub>Pattern</sub> geschrieben. Bei einer Übereinstimmung der Addition mit dem Inhalt des Registers  $\text{Reg}_{Data}$  wird ausschließlich das für diese Ebene benötigte Bit in dem Wort des FIFO<sub>Pattern</sub> zu eins gesetzt.

Als Beispiel soll in einer Ebene Nummer drei mit insgesamt 16 Kanälen der vierte Kanal gesetzt werden. D.h. erst im zwölften Durchlauf entspricht die Addition von zwölf (getätigte Anzahl an Durchläufen) mit vier (gewünschte Kanalzahl) der Maximalzahl an möglichen Kanälen (16). Da die Ebenen bitweise gesetzt werden, beträgt der Inhalt des Wort im FIFO<sub>Pattern</sub> im zwölften Durchlauf vier, das entspricht dem dritten Bit und damit der dritten Ebene. Alle übrigen Inhalte des FIFO<sub>Pattern</sub> werden zu null gesetzt.

Anhand des Ergebnisses kann abgelesen werden, ob die Auslesekette für diesen bestimmten Kanal funktioniert und ob benachbarte Kanäle zusätzlich auf das Signal angesprochen haben.

Die einzelnen Prüfverfahren sowohl des Flaggen-Konsistenz- als auch des Pattern-Tests sind mehrmals hintereinander durchzuführen, um nichtsystembedingte Fehler auszuschließen.

### 5.4 Die Lab-NB Karte

Die in Kapitel 5.1 erwähnte Input/Output–Karte der Firma National Instruments trägt den Namen Lab–NB. Sie eine kostengünstige multifunktionale analoge und digitale I/O–Karte für Macintosh NuBus Computer, mit einer Zeitauflösung von bis zu 1  $\mu$ s für digitale Signale.

Die Karte besteht aus einem 12 Bit A/D-Wandler mit acht Analog-Eingängen, zwei 12 Bit D/A-Wandlern mit Spannungs-Ausgängen, 24 digitalen I/O-kompatiblen bidirektionalen Leitungen und sechs 16 Bit Kanälen für Zeitmessungen.

Für den digitalen Datentransfer liegen die Operationsgrenzen der Lab-NB bei +5.5 V und -0.5 V auf Masse bezogen. Zur Signalerfassung wird die an den digitalen Leitungen anliegende Spannung gemessen. Übersteigt sie den Wert von 2.2 V wird ein Bit von null auf eins gesetzt, fällt sie unter 3.7 V von eins auf null [17, 10, 11].

Die 24 bidirektionalen Leitungen sind in drei gleichgroße "Ports" unterteilt (Port A, B und C). Ein Port enthält acht Leitungen, von denen jede ein Bit darstellt, so daß mit einem Port ein aus acht Bit bestehendes Wort gelesen oder geschrieben werden kann.

Mit der Karte wurden entsprechende Programme mitgeliefert, die die Benutzung der Lab-NB vereinfachen. Insgesamt verfügt die Lab-NB über 50 Ein- bzw. Ausgangspins, deren Namen und Funktionen sowie weitere Informationen zu der

Karte [10, 11] entnommen werden können.

#### 5.5 Prüfverfahren mit der Lab-NB Karte

#### 5.5.1 Die Signalerfassung

An die Karte ist ein 50-poliges Flachbandkabel angeschlossen. Das Kabel ist an einem Ende auf einer Länge von ca.40 cm in seine 50 einzelnen Leitungen aufgeteilt. An jedem Ende einer Leitung befindet sich eine kleine Prüfspitze. Die Prüfspitzen ermöglichen es, Spannungen oder Spannungspulse an den Anschlüssen der Bausteine, auch Pins genannt, auf dem ROC abzugreifen. Durch die Aufspaltung des Flachbandkabels in die einzelnen Leitungen können gleichzeitig mehrere Signale an unterschiedlichen Stellen auf dem ROC gemessen werden. Die Steuereinheit der Auslese auf dem ROC, der Mode Controller, kann mit dieser Karte nicht geprüft werden. Einige der programmierbaren Bausteine haben einen internen Taktgeber, die VME-Clock, mit einer Frequenz von 16 MHz. Diese Bausteine sind auf die HERA-Clock, bzw. den 10 MHz Oszillator abgestimmt, so daß sich aufgrund der Zeitauflösung bei Frequenzen, die kleiner als 10 MHz sind, die Eingangssignale nicht mehr zu den gewünschten Ausgangssignalen zusammensetzen. Es entstehen undefinierte Zustände.

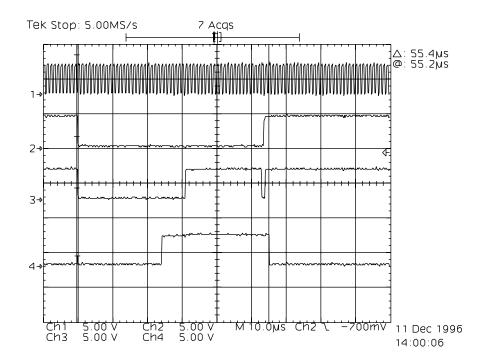

Die beiden Mode Bits M0 und M1 sind davon nicht betroffen. Abbildung 5.3 zeigt den Verlauf der beiden Mode Bits M0 und M1 mit einem 1 MHz Oszillator. Die Aufnahmen wurden mit einem 4-Kanal-Speicher-Oszilloskop angefertigt. Die auf der linken Seite des Bildes stehenden Zahlen geben die Kanalnummer an, die nebenstehenden Pfeile die zu dem Kanal gehörende Null-Linie (0 V).

Die Prüfverfahren mit der Lab-NB Karte kontrollieren die Signalwege und Dateninhalte. Anhand der Schaltpläne des ROC in [25] ist die Signalbelegung der einzelnen Pins auf den Bausteinen abzulesen. Der Signalweg ergibt sich aus den Signalnamen; z.B. das RUN-Signal, das vom ROD kommt, heißt "BRUN", nachdem es den ersten Baustein passiert hat, läuft es als "RUN" weiter. An einem Querbalken über oder an einem Stern an dem Signalnamen ist zu erkennen, ob es sich um ein invertiertes Signal handelt.

Die Anzahl der Meßpunkte entspricht der Zahl an gesetzten und nicht gesetzten Bits. Durch die Programme wird in vorgegebener Reihenfolge an jedem Meßpunkt eine Prüfspitze der digitalen Leitungen angeklemmt. Die an den Ports (siehe Kapitel 5.4) anliegenden Daten werden mit berechneten Werten verglichen. Aus einer etwaigen Differenz wird die betreffende Leitung und damit der Pin an einem Baustein ermittelt, an dem keine korrekten Daten mehr anliegen. Das Prüfverfahren gliedert sich in acht Programme. Diese können nur am Teststand durchgeführt werden, da sich die Lab-NB Karte in dem neben dem Test-

Abbildung 5.3: Verlauf der beiden Mode Bits M0 und M1 mit einem 1 MHz Oszillator

Kanal 1: Das Clock-Signal (1 MHz)

Kanal 2: Das Triggersignal PEn

Kanal 3: Das Mode Bit M0

Kanal 4: Das Mode Bit M1

stand stehenden Macintosh Computer befindet. Im Myon-System ist es auch nicht möglich einen Extender zu benutzen, da dieser auf dem VME-Bus Signalreflektionen erzeugt.

### 5.5.2 Die vier Input-Signale

#### Das Clock-Signal

Um einen reibungslosen Ablauf eines Auslesezyklus zu garantieren, müssen die einzelnen Signale mit derselben Frequenz getaktet werden. Im Myon-System wird dieses Taktsignal von der HERA-Clock geliefert. Es wird an die einzelnen Detektorkomponenten weitergegeben. Im Teststand übernimmt ein Oszillator, der auf dem ROD aufgebracht ist, die Aufgabe des Taktgebers. Wie im Myon-

System wird das Clock-Signal von den RODs an die ROCs weitergegeben.

Da die Zeitauflösung der Lab-NB Karte für ein 10 MHz Signal nicht ausreichend ist, wird das Vorhandensein der Clock statistisch überprüft. Die Bedingung für einen erfolgreichen Test könnte sein, ein alternierendes Signal zu messen. Auf dem ROC gibt es insgesamt zwölf Möglichkeiten, das Clock-Signal abzugreifen. In Sieben von den zwölf Möglichkeiten liegt das Signal invertiert vor. Bei einer Messung mit den digitalen Leitungen der Lab-NB Karte und einer Aufteilung der Signale in invertierte und nichtinvertierte Signale wäre die Erwartung, daß der Inhalt der Leitungen von Port A (nichtinvertierte Signale) entweder 31 betrage und der von Port B (invertierte Signale) null, oder der Inhalt von Port A wäre null und der von Port B betrage 127.

Aufgrund des äußerst schnellen Signalwechsels und der durch Gatterlaufzeiten bedingten Phasenverschiebungen an den einzelnen Bausteinen liegt in aufeinanderfolgenden Messungen an einzelnen Leitungen eines Ports aber sehr selten derselbe Inhalt an. Diese Phasenverschiebungen sind auch der Grund, daß die Inhalte von Port A und B gleichzeitig null bzw. nicht null sein können. Zur Vereinfachung wird allen Inhalten von Port A, die  $\leq$  zwölf sind, der Wert null zugeordnet, denjenigen, die > als zwölf sind, der Wert 31. Bei Port B verhält es sich ähnlich, alle Inhalte, die  $\leq$  50 sind, erhalten den Wert null, die übrigen den Wert 127.

Die Wahrscheinlichkeit, nach einer Messung an einem bestimmten Port mit dem Inhalt null, bei einer zweiten Messung an demselben Port auch den Inhalt null zu erhalten liegt bei 50%. Die Wahrscheinlichkeit, nach einer dritten Messung in Folge immer noch den Wert null zu erhalten, liegt nur noch bei 25%. Die Wahrscheinlichkeit, nach n Messungen immer noch denselben Wert zu erhalten, nimmt mit  $\frac{1}{2^n}$  ab.

Um eine Korrelation zwischen der Prozessorfrequenz des Macintosh Computers und dem 10 MHz Oszillator auszuschließen, wurden zweimal je 10.000 Messungen gemacht. Es besteht die Möglichkeit eines schwebungsähnlichen Zustandes, der sich maximal über 15 Messungen erstreckt. Aus diesem Grund werden bei diesem Prüfverfahren 500 Messungen vorgenommen. Die Bedingung für einen erfolgreichen Test ist, eine Alternierung des Signals messen zu können, wobei maximal drei schwebungsähnliche Zustände toleriert werden.

#### Das FastClear-Signal

Dieser Test benutzt den "Handshaking Mode". Das heißt, das an Port C an der vierten Leitung (PC< 4 >) anliegende Signal dient als Trigger. Sobald die Spannung dieses Signals unter den Mindestwert absinkt, ist das für die Karte das Zeichen, von allen anderen an der Messung beteiligten Prüfspitzen die Signale zu erfassen. Auf dem ROC gibt es 13 Möglichkeiten, das Signal FastClear abzugreifen. In fünf Fällen wird das Signal bei Ansprechen active high erwartet, in den restlichen acht Fällen durch vorhergehendes Invertieren des Signals active low.

Für eine übersichtlichere Datenerfassung liegen alle active high Signale an Port A an, alle active low Signale liegen an Port B.